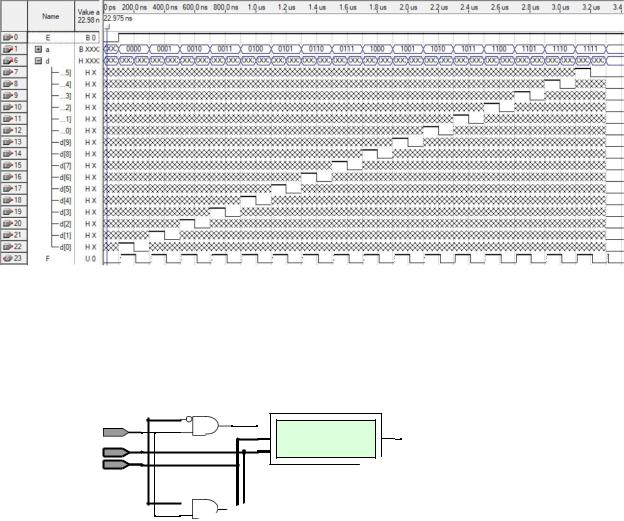

Рисунок 1.11 – Моделирование кода мультиплексора 16-1.

E0 |

|

mux_8_1:LOW_MUX |

|

|

|

E |

|

E |

|

d[7..0] |

F |

|

a[2..0] |

|

|

|

|

|

|

a[3 |

E1 |

m |

|

|

|

|

|

..0] |

|

|

|

d[15..0] |

|

|

|

Рисунок 1.12 – RTL-схема мультиплексора 16-1.

11

2. ДЕМУЛЬТИПЛЕКСОР

По условию варианта, нужно собрать схему демультиплексора типа 1-4

И-НЕ. Ниже приведены таблица истинности (2.1) и формулы для всех входов и выходов устройства. А также таблица и формулы для преобразованного устройства.

Таблица 2.1 – Таблица истинности демультиплексора 1-4.

|

Вход |

|

|

|

|

Выход |

|

||

|

ы |

|

|

|

|

ы |

|

||

E |

1 |

|

0 |

x |

3 |

2 |

|

1 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

0 |

2 |

0 |

2 |

|

0 |

0 |

1 |

1 |

|

1 |

3 |

3 |

0 |

|

0 |

0 |

0 |

x |

|

x |

x |

0 |

0 |

|

0 |

0 |

Формулы для выходов:

|

|

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ |

|

0 |

= ∩ ∩ ̅̅̅ ∩ ̅̅̅ |

||

|

1 |

0 |

|

|

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ |

||

= ∩ ∩ ̅̅̅ ∩ |

|||

1 |

1 |

0 |

|

|

|

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ |

|

2 |

= ∩ ∩ |

∩ ̅̅̅ |

|

|

1 |

0 |

|

|

|

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ |

|

3 = ∩ ∩ 1 |

∩ 0 |

||

12

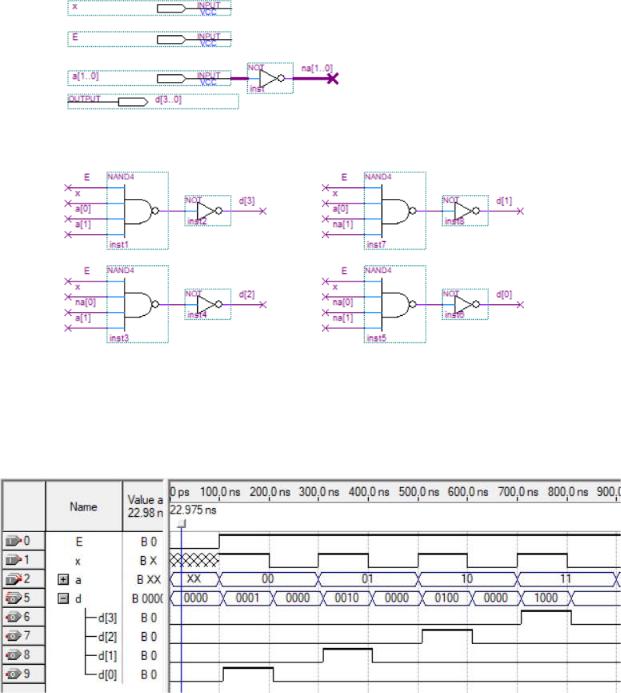

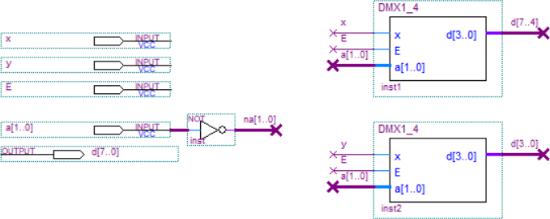

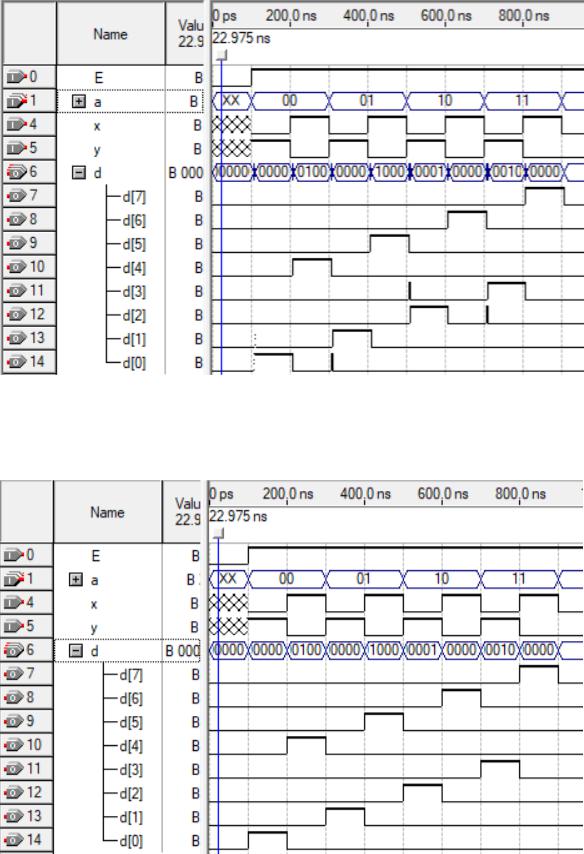

Ниже на рисунках 2.1-2.3 изображены схема и моделирование демультиплексора 1-4. На рисунках 2.4-2.6 код, моделирование и RTL-схема.

Рисунок 2.1 – Функциональная схема демультиплексора 1-4.

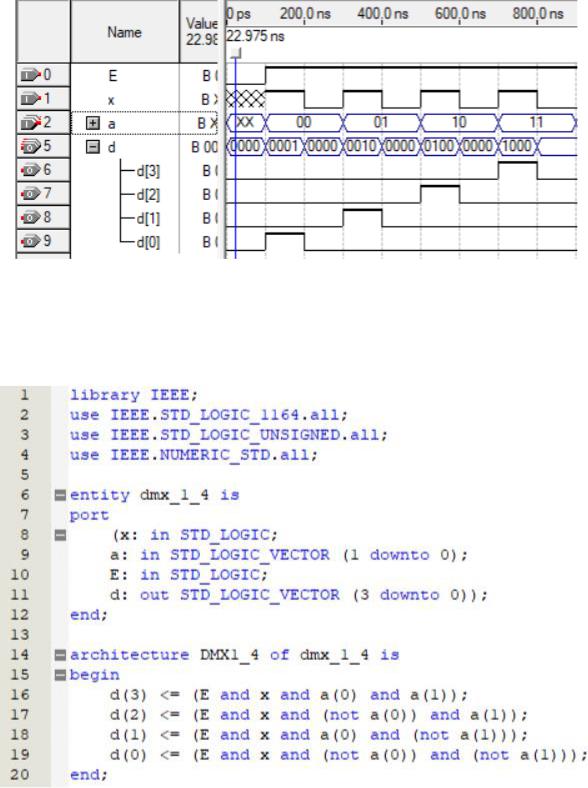

Рисунок 2.2 – Моделирование схемы демультиплексора 1-4.

13

Рисунок 2.3 – Функциональный режим моделирования демультиплексора

1-4.

Рисунок 2.4 – Код демультиплексора 1-4 на VHDL.

14

Рисунок 2.5 – Моделирование кода демультиплексора 1-4.

|

|

d~0 |

|

|

|

d~1 |

d |

|||||

x |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

~ |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

d~3 |

|

|

|

d~4 |

|

E |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d~5 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a[1..0] |

|

|

|

|

|

|

|

|

|

|

|

d~6 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d[3..0]

Рисунок 2.6 – RTL-схема демультиплексора 1-4.

15

Также, согласно варианту, демультиплексор нужно нарастить до 2-8.

Таблица истинности (2.2) показана ниже.

Таблица 2.2 – Таблица истинности демультиплексора 2-8.

|

|

Вход |

|

|

|

|

|

Выход |

|

|

|

||

|

|

ы |

|

|

|

|

|

|

ы |

|

|

|

|

E |

1 |

0 |

x |

y |

7 |

6 |

5 |

4 |

|

3 |

2 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

1 |

0 |

2 |

2 |

0 |

2 |

0 |

0 |

|

0 |

2 |

0 |

0 |

1 |

1 |

1 |

3 |

3 |

3 |

0 |

0 |

0 |

|

3 |

0 |

0 |

0 |

0 |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

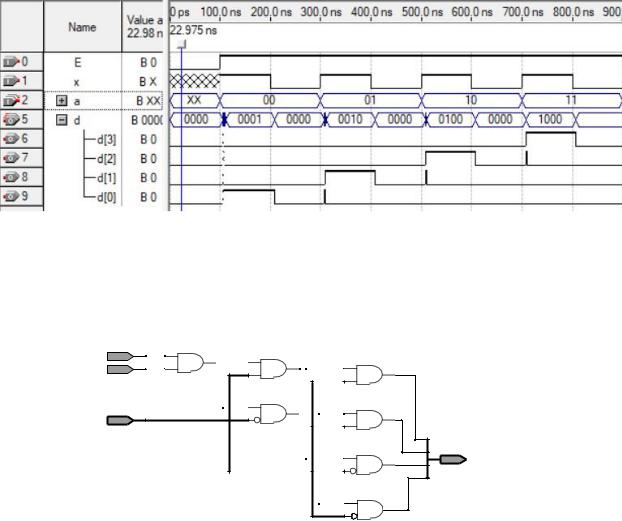

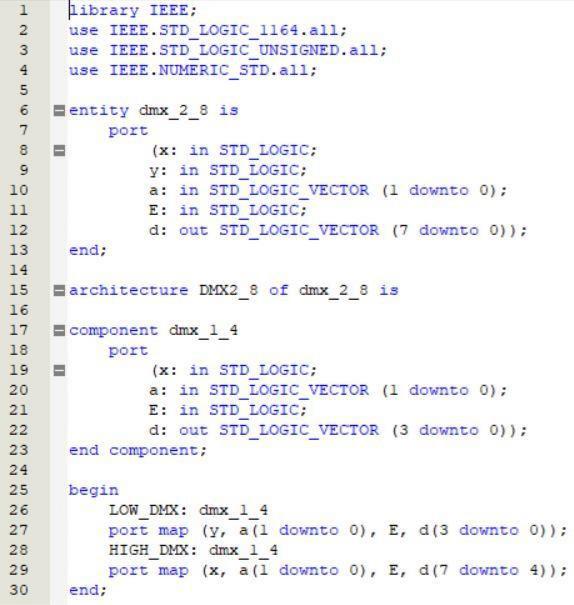

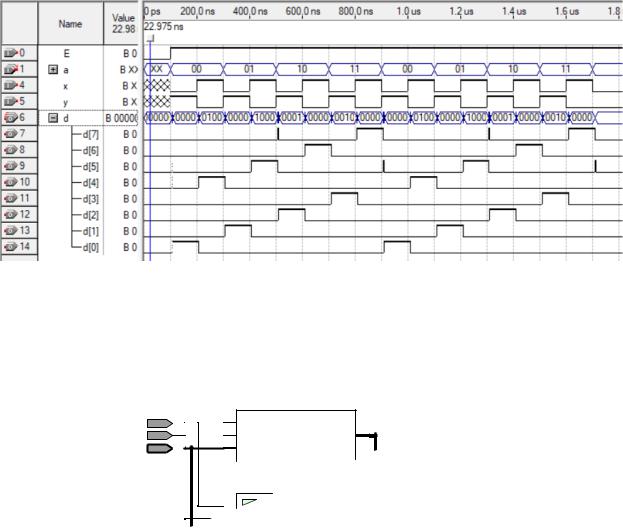

Ниже на рисунках 2.7-2.9 изображены схема и моделирование демультиплексора 1-4. На рисунках 2.10-2.12 код, моделирование и RTL-

схема.

Рисунок 2.7 – Функциональная схема демультиплексора 2-8.

16

Рисунок 2.8 – Моделирование схемы демультиплексора 2-8.

Рисунок 2.9 – Функциональный режим моделирования демультиплексора

2-8.

17

Рисунок 2.10 – Код демультиплексора 2-8 на VHDL.

18

Рисунок 2.11 – Моделирование кода демультиплексора 2-8.

dmx_1_4:HIGH_DMX

|

|

|

|

|

E |

|

|

E |

|

||||||

x |

d[3..0] |

||||||

|

|

|

|

|

|||

|

|

|

|

|

a[1..0] |

|

|

x |

|

|

|

||||

|

|

|

|||||

|

|

|

|||||

dmx_1_4

a[1

..0]

y

Рисунок 2.12 – RTL-схема демультиплексора 2-8.

19

3. РЕАЛИЗАЦИЯ ФУНКЦИИ НА ОСНОВЕ МУЛЬТИПЛЕКСОРА И

ДЕМУЛЬТИПЛЕКСОРА

По 9 варианту в первой лабораторной работе была дана функция:

= ∩ (( ) ). Ниже приведены таблица истинности (3.1) и формулы для всех входов и выходов устройства.

Таблица 3.1 – Таблица истинности.

|

|

Входы |

|

Выход |

|

|

|

|

|

|

|

x |

y |

|

z |

w |

|

|

|

|

|

|

|

0 |

0 |

|

0 |

0 |

0 |

|

|

|

|

|

|

0 |

0 |

|

0 |

1 |

0 |

|

|

|

|

|

|

0 |

0 |

|

1 |

0 |

0 |

|

|

|

|

|

|

0 |

0 |

|

1 |

1 |

0 |

|

|

|

|

|

|

0 |

1 |

|

0 |

0 |

0 |

|

|

|

|

|

|

0 |

1 |

|

0 |

1 |

0 |

|

|

|

|

|

|

0 |

1 |

|

1 |

0 |

0 |

|

|

|

|

|

|

0 |

1 |

|

1 |

1 |

0 |

|

|

|

|

|

|

1 |

0 |

|

0 |

0 |

1 |

|

|

|

|

|

|

1 |

0 |

|

0 |

1 |

0 |

|

|

|

|

|

|

1 |

0 |

|

1 |

0 |

0 |

|

|

|

|

|

|

1 |

0 |

|

1 |

1 |

1 |

|

|

|

|

|

|

1 |

1 |

|

0 |

0 |

0 |

|

|

|

|

|

|

1 |

1 |

|

0 |

1 |

1 |

|

|

|

|

|

|

1 |

1 |

|

1 |

0 |

1 |

|

|

|

|

|

|

1 |

1 |

|

1 |

1 |

0 |

|

|

|

|

|

|

20