Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ШИФРАТОРЫ И ДЕШИФРАТОРЫ

Отчет по лабораторной работе №2 по дисциплине «Электроника и схемотехника»

Вариант № 12

Студент гр.

**.**.2022

Руководитель

**** кафедры КИБЭВС _______

**.**.2022

Томск 2022

Введение

Целью работы - получить навыки создания шифраторов и дешифраторов на разных базисах и решить задачи по увеличению их размерности.

Поставленные задачи:

Собрать на холсте схемы устройств CD 4–2 (на базисе И-НЕ), DC 3– 8 (на базисе ИЛИ-НЕ), HPRI 6-3 (на базисе И,ИЛИ, НЕ), а также описать их на VHDL и промоделировать работы схем.

Собрать на холсте схемы устройств с увеличенной размерностью: СD

8–3 и DC 16–4, а также описать их на VHDL и промоделировать работы схем.

2

1ШИФРАТОР 4–2

1.1Таблица истинности

Шифраторы предназначены для преобразования кода «1 из N» в

двоичный. При подаче на один (обязательно на один, и не более) из входов шифратора на его выходе формируется двоичный код номера возбужденной входной линии. Полный двоичный шифратор имеет 2 входов и выходов.

Для информирования о том, что на вход была подана только одна единица, сигнализирует выход .

Также на вход подается сигнал E, который разрешает работу данного шифратора.

В таблице 1.1 представлена таблица истинности для устройства CD 4–2.

Таблица 1.1 Таблица истинности CD 4–2

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

|

|

|

|

|

|

|

|

|

E |

|

|

x |

|

|

a |

G |

||

|

|

|

|

|

|

|

|

||

3 |

2 |

|

1 |

0 |

1 |

|

0 |

||

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

0 |

x |

x |

|

x |

x |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

0 |

0 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

0 |

0 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

0 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

0 |

0 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

1.2Формула

Формула для выхода G будет иметь вид: =

̅̅̅ |

̅̅̅ |

̅̅̅̅̅ |

|

|

̅̅̅ |

̅̅̅ |

̅̅̅̅̅ |

|

|

̅̅̅ |

̅̅̅ |

̅̅̅ |

|

( ∩ 3 ∩ 2 |

∩ 1 |

∩ 0) |

∩ ( ∩ 3 |

∩ 2 ∩ 1 |

∩ 0) |

∩ ( ∩ 3 |

∩ 2 |

∩ 1 ∩ 0) ∩ |

|||||

( ∩ ̅̅̅3 ∩ ̅̅̅2 ∩ ̅̅̅1 ∩ 0)

Формула для выхода a0 будет иметь вид:

3

0 |

|

|

̅̅̅ |

̅̅̅ |

̅̅̅̅̅ |

|

|

̅̅̅ |

̅̅̅ |

|

̅̅̅̅̅ |

|

||

= ( ∩ 3 ∩ 2 |

∩ 1 |

∩ 0) |

∩ ( ∩ 3 ∩ 2 |

∩ 1 ∩ 0) . |

||||||||||

Формула для выхода a1 будет иметь вид: |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

̅̅̅ |

̅̅̅ |

̅̅̅ |

|

̅̅̅ |

|

̅̅̅ |

̅̅̅ |

||||

= ( ∩ 3 ∩ 2 |

∩ 1 |

∩ 0) |

∩ ( ∩ 3 |

∩ 2 ∩ 1 |

∩ 0). |

|||||||||

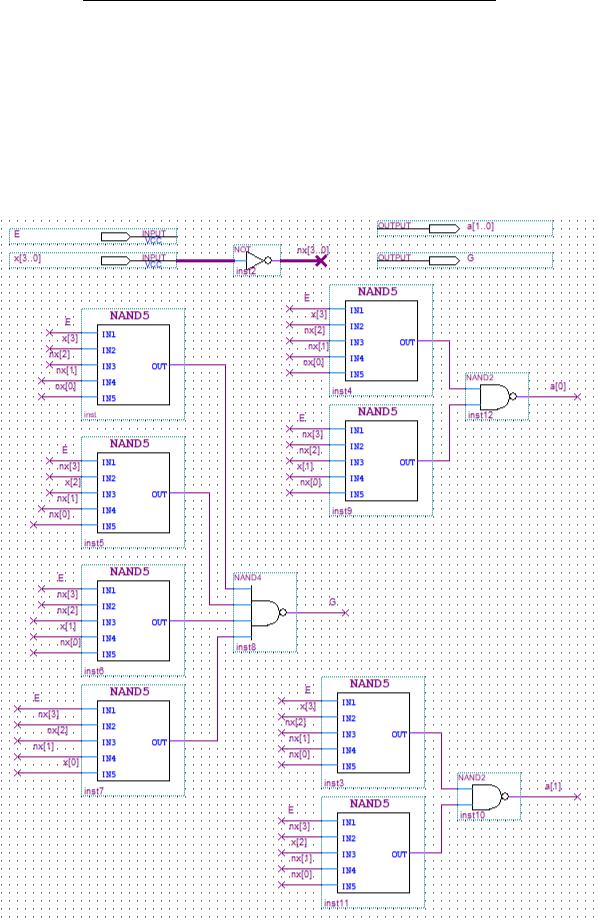

1.3Функциональная схема

На рисунке 1.1 представлена функциональная схема устройства.

Рисунок 1.1 – Шифратор 4–2 4

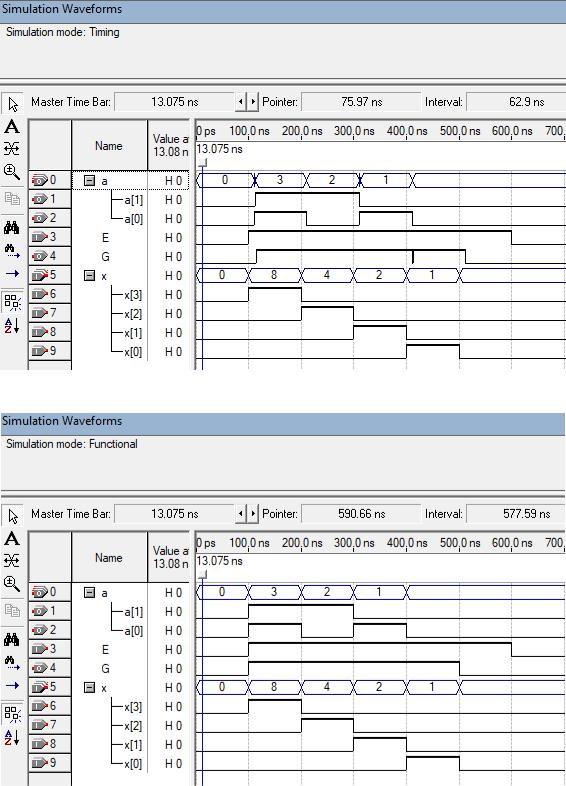

1.4Моделирование

На рисунках 1.2 и 1.3 представлено моделирование шифратора 4–2.

Рисунок 1.2 – Моделирование шифратора 4–2 (Timing)

Рисунок 1.3 – Моделирование шифратора 4–2 (Functional)

5

Моделирование соответствует таблице истинности (для удобства сигналы на входах x представлены в шестнадцатеричной системе счисления, а

на выходах a – в десятеричной).

Помимо основных состояний, при которых шифратор работает правильно, были проверены состояния, при которых сигнал должен сигнализировать о том, что на вход подан не унитарный код.

1.5Код на HDL

На рисунке 1.4 представлено описание устройства на VHDL.

Рисунок 1.4 – Шифратор 4–2 на VHDL

Программа работает аналогично функциональной схеме.

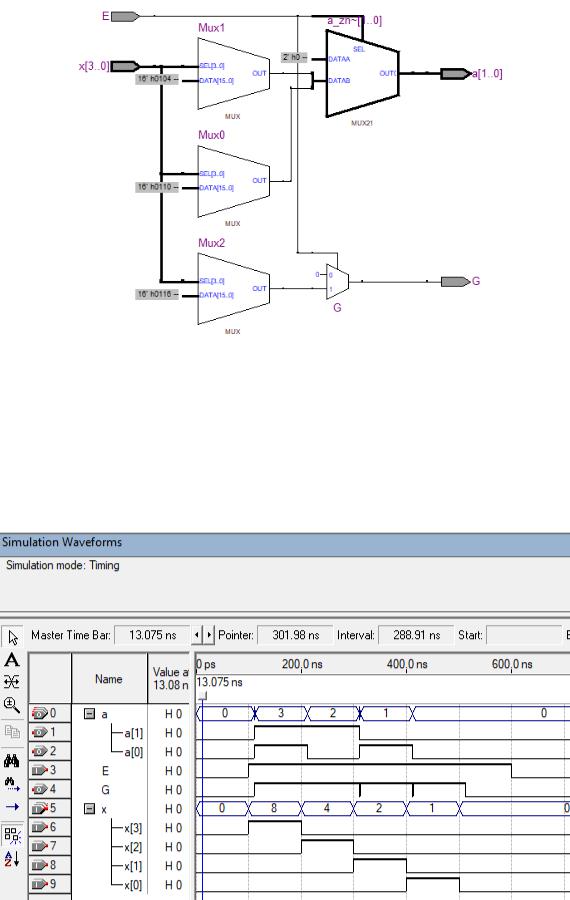

1.6Схема из RTL viewer для кода HDL

На рисунке 1.5 представлена схема из RTL viewer для кода на VHDL.

6

Рисунок 1.5 – Схема из RTL viewer

1.7Моделирование устройства, описанного кодом HDL

На рисунке 1.6 представлено моделирование шифратора 4–2,

описанного на VHDL.

Рисунок 1.6 – Моделирование шифратора 4–2 (Timing)

7

Последовательность входных сигналов и сигналы на выходе

соответствуют таблице истинности.

1.8Таблица истинности масштабируемого устройства

Втаблице 1.2 представлена таблица истинности для устройства CD 8–3.

Таблица 1.2 – Таблица истинности CD 8–3

|

|

|

|

Входы |

|

|

|

|

|

Выходы |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

|

|

|

|

x |

|

|

|

|

|

a |

|

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

7 |

6 |

5 |

|

4 |

|

3 |

2 |

1 |

0 |

2 |

1 |

0 |

||

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

x |

x |

x |

|

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

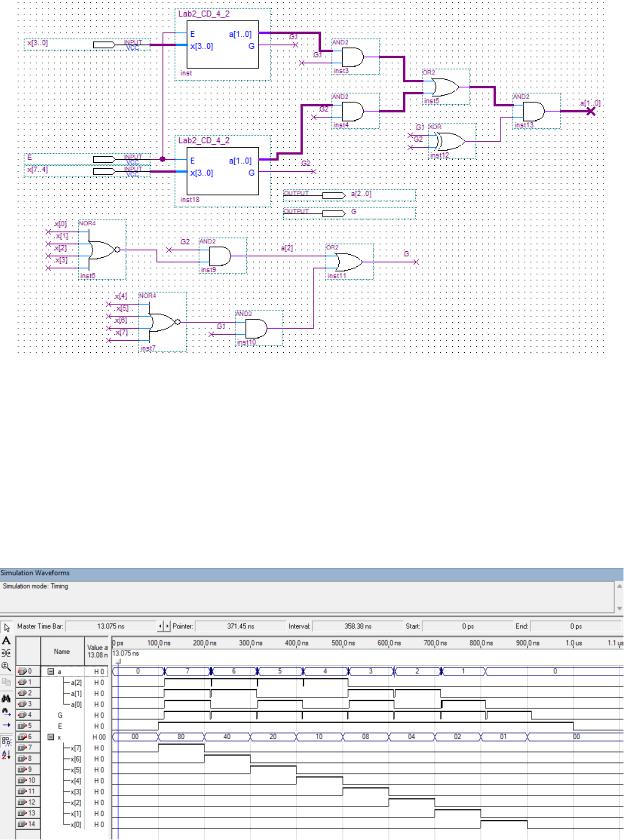

1.9Функциональная схема масштабируемого устройства

На рисунке 1.7 представлена функциональная схема устройства CD 8–3.

8

Рисунок 1.7 – Шифратор 8–3

Для построения схемы устройства использовались сохраненные в качестве символа шифраторы 4–2.

1.10 Моделирование масштабируемого устройства

На рисунках 1.8 и 1.9 представлено моделирование шифратора 8–3.

Рисунок 1.8 – Моделирование шифратора 8–3 (Timing)

9

Рисунок 1.9 – Моделирование шифратора 8–3 (Functional)

1.11 Код на HDL масштабируемого устройства

На рисунке 1.10 представлено описание устройства на VHDL.

Рисунок 1.10 – Шифратор 8–3 на VHDL

Программа работает аналогично функциональной схеме.

1.12 Схема из RTL viewer для кода HDL масштабируемого устройства

На рисунке 1.11 представлена схема из RTL Viewer для кода на VHDL.

10