Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ ТРИГГЕРОВ

Отчет по лабораторной работе №4 по дисциплине «Электроника и схемотехника»

Вариант № 12

Студент гр.

==.==.2022

Руководитель

== кафедры КИБЭВС

_______ ==

==.==.2022

Томск 2022

Введение

Цель работы − изучить основные типы триггеров, их принципы построения и работы.

Поставленные задачи:

1. Составить таблицы функционирования для схем согласно варианту.

Таблица 1 – Задание на ЛР

Триггер |

Тип |

Базис |

|

|

|

JK |

s1 |

ИЛИ-НЕ |

|

|

|

T |

d |

И-НЕ |

|

|

|

D |

s2 |

И НЕ |

|

|

|

2.Собрать схемы на холстах .bdf согласно варианту.

3.Промоделировать работу всех схем в двух режимах (timing и

functional). Сравнить результаты моделирования с составленными таблицами истинностями

4. Используя заданный вариантом HDL, описать те же устройства.

Вариант HDL: VHDL.

2

1.ОДНОСТУПЕНЧАТЫЙ JK-ТРИГГЕР В БАЗИСЕ ИЛИ-НЕ

1.1Таблица истинности

Втаблице 1.1 представлена таблица функционирования триггера s1-JK.

Таблица 1.1 – Таблица функционирования s1-JK

|

Входы |

|

|

Выходы |

Режим |

|

|

|

|

|

|

|

|

J |

K |

C |

Q(t) |

|

Q(t+1) |

|

|

|

|

|

|

|

|

X |

X |

0 |

0/1 |

|

0/1 |

Хранение |

|

|

|

|

|

|

|

0 |

1 |

1 |

X |

|

0 |

Установка в 0 |

|

|

|

|

|

|

|

1 |

0 |

1 |

X |

|

1 |

Установка в 1 |

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

|

0 |

Счётный из 1 в 0 |

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

|

1 |

Счётный из 0 в 1 |

|

|

|

|

|

|

|

1.2Функциональная схема

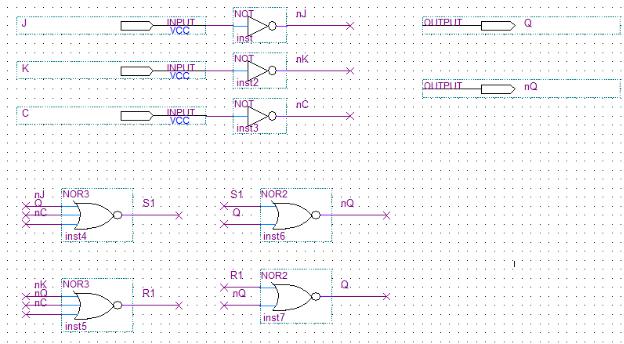

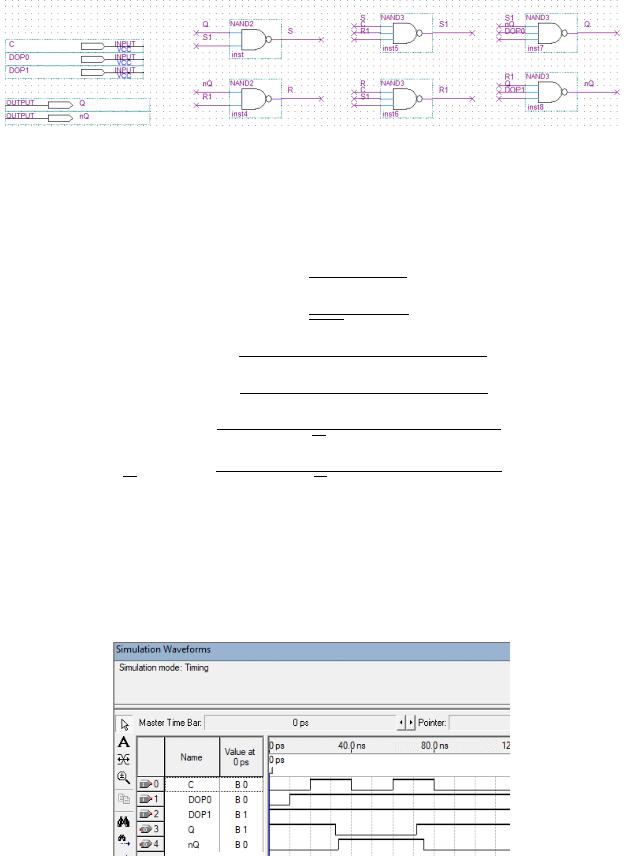

На рисунке 1.1 представлена функциональная схема s1-JK.

Рисунок 1.1 - Схема s1-JK

1.3Формула

Ниже представлены формулы схемы для s1-JK в базисе ИЛИ-НЕ:

3

̅̅̅̅̅̅̅̅̅̅̅̅

1( + 1) =

̅̅̅̅̅̅̅̅̅̅̅̅̅

1( + 1) =

̅̅̅̅̅̅̅̅̅

( + 2) = 1

̅̅̅̅̅̅̅̅̅

( + 2) = 1

1.4Моделирование функциональной схемы

На рисунке 1.2 представлен результат моделирования в режиме Timing.

Рисунок 1.2 - Результат моделирования s1-JK (Timing)

Результат моделирования совпадает со значениями из таблицы функционирования, представленной в таблице 1.1.

1.5Код на HDL

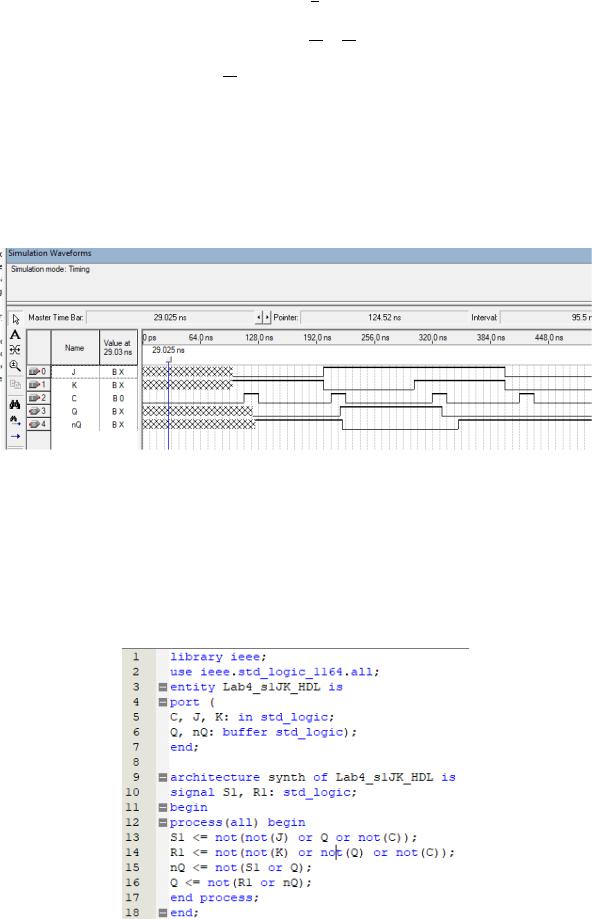

На рисунке 1.4 представлен код описания s1-JK на VHDL.

Рисунок 1.4 – Код описания s1-JK на VHDL

4

1.6Схема из RTL viewer для кода HDL

На рисунке 1.5 представлена схема из RTL viewer для кода, написанном на VHDL. Схема соответствует функциональной схеме.

Рисунок 1.5 – Схема из RTL viewer для кода s1-JK

1.7Моделирование устройства, описанного кодом HDL

На рисунке 1.6 представлен результат моделирования s1-JK, описанного на VHDL.

Рисунок 1.6 - Результат моделирования s1-JK (Timing)

По неизвестной причине, при моделировании счетного режима устройства, которое описано кодом HDL, моделирование Q и nQ становится черным как на рисунке 1.6. Исправить данную причину не удалось.

1.8Исследование минимального порога длительности активного

уровня управляющего сигнала

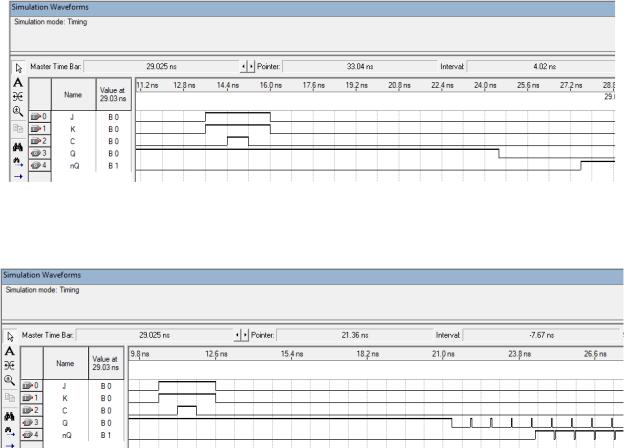

На рисунке 1.7 представлен результат моделирования при длительности

активного уровня сигнала C = 0,8 нс.

5

Рисунок 1.7 - C = 0,8 нс

На рисунке 1.8 представлен уже результат при C = 0,7 нс. Как видно,

такой длительности сигнала недостаточно для корректной работы устройства.

Рисунок 1.8 - C = 0,7 нс

2.ДИНАМИЧЕСКИЙ Т-ТРИГГЕР В БАЗИСЕ И-НЕ

2.1Таблица истинности

Втаблице 2.1 представлена таблица функционирования d-T.

Таблица 2.1 – Таблица функционирования d-T

Входы |

Выходы |

|

Режим |

|

|

|

|

|

|

C |

Q(t) |

|

Q(t+1) |

|

|

|

|

|

|

0 |

0 |

|

0 |

Хранение |

|

|

|

|

|

0 |

1 |

|

1 |

Хранение |

|

|

|

|

|

1 |

0 |

|

1 |

Счётный из 0 в 1 |

|

|

|

|

|

1 |

1 |

|

0 |

Счётный из 1 в 0 |

|

|

|

|

|

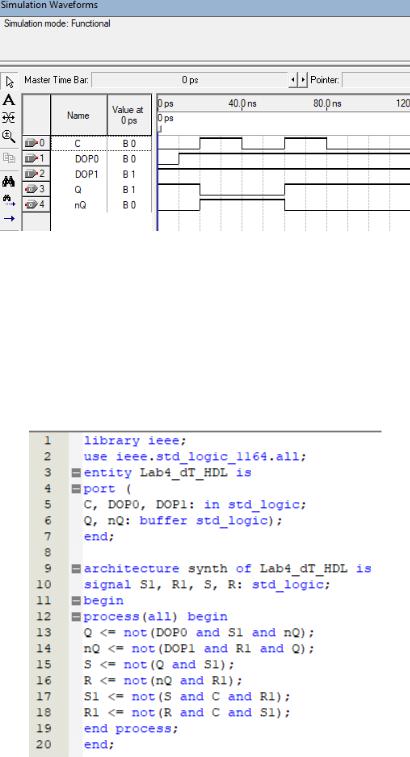

2.2Функциональная схема

На рисунке 1.1 представлена функциональная схема s1-JK. 6

Рисунок 1.1 - Схема d-T

2.3Формула

Ниже представлены формулы схемы для d-T в базисе И-НЕ:

( + 1) = Q(t) ∩ S1(t)

( + 1) = Q(t) ∩ R1(t)

1( + 2) = S(t + 1) ∩ C(t + 1) ∩ R1(t + 1)

1( + 2) = R(t + 1) ∩ C(t + 1) ∩ S1(t + 1)

( + 3) = S1(t + 2) ∩ Q(t + 2) ∩ DOP0(t + 2)

( + 3) = R1(t + 2) ∩ Q(t + 2) ∩ DOP1(t + 2)

2.4Моделирование функциональной схемы

На рисунках 2.2–2.3 представлены результат моделирования d-T в двух режимах.

Рисунок 2.2 - Результат моделирования d-T (Timing)

7

Рисунок 2.3 - Результат моделирования d-T (Functional)

Результат моделирования совпадает со значениями из таблицы функционирования, представленной в таблице 2.1.

2.5Код на HDL

На рисунке 2.4 представлен код описания d-T на VHDL.

Рисунок 1.4 – Код описания d-T на VHDL

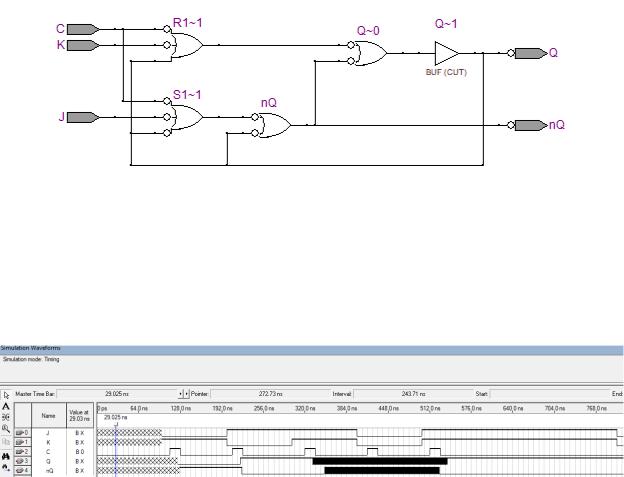

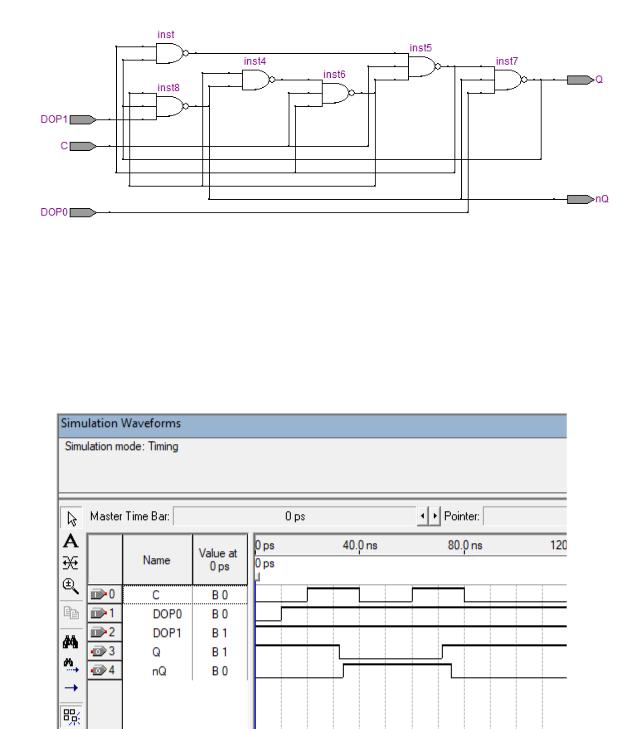

2.6Схема из RTL viewer для кода HDL

8

|

На рисунке 2.5 представлена схема из RTL viewer для кода, написанном |

||||

на |

VHDL. |

Схема |

соответствует |

функциональной |

схеме. |

Рисунок 1.5 – Схема из RTL viewer для кода d-T

2.7Моделирование устройства, описанного кодом HDL

На рисунках 2.6–2.7 представлены результаты моделирования d-T,

описанного на VHDL.

Рисунок 1.6 - Результат моделирования d-T (Timing)

9

Рисунок 2.7 - Результат моделирования d-T (Functional)

Результат моделирования совпадает со значениями из таблицы функционирования, представленной в таблице 2.1.

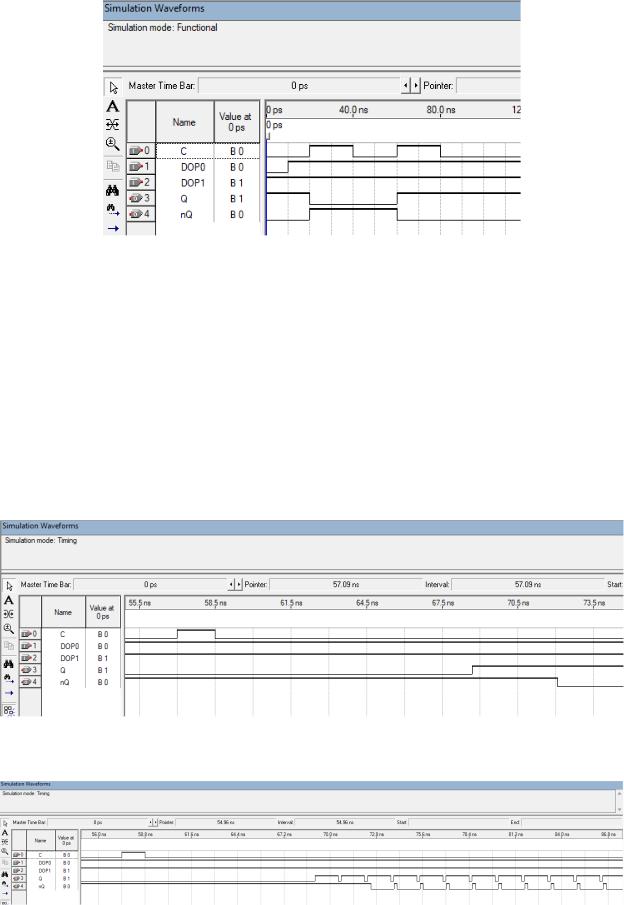

2.8Исследование минимального порога длительности активного

уровня управляющего сигнала

На рисунке 2.8 представлен результат моделирования при длительности активного уровня сигнала C = 1,5 нс.

Рисунок 2.8 - C = 1,5 нс

На рисунке 2.9 представлен уже результат при C = 1,4 нс.

Рисунок 2.9 - C = 1,4 нс

Минимальный порог длительности – 1,5 нс.

10