Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ СЧЕТЧИКОВ

Отчет по лабораторной работе №5 по дисциплине «Электроника и схемотехника»

Вариант № 12

Студент гр.

==.==.2022

Руководитель

== кафедры КИБЭВС

_______ == ==.==.2022

Томск 2022

Введение

Цель работы − изучить двоичные счётчики, их принципы построения и работы.

В ходе данной лабораторной работы требуется выполнить следующие задачи:

1. Составить таблицы истинности для схем согласно варианту.

Таблица 1 – Задание по варианту

Асинхронный

тип |

счет |

|

М |

|

|

|

|

|

|

Т |

- |

|

26 |

|

|

|

|

|

|

|

Синхронный |

|

|

|

|

|

|

|

|

фронт |

сброс |

счет |

|

М |

|

|

|

|

|

+ |

s |

+ |

|

31 |

|

|

|

|

|

2.Собрать схемы заданных счётчиков на холстах .bdf.

3.Привести расчёты для задач делителя частоты и формирования задержки (выходная частота: 2173913 Гц, задержка: 0,60 мкс)

4.Собрать схемы делителя частоты и задержки.

5.Промоделировать работу всех схем в двух режимах (timing и

functional). Сравнить результаты моделирования с составленными таблицами

истинности.

6. Используя заданный вариантом HDL, описать те же устройства.

Вариант HDL: System Verilog.

2

1.АСИНХРОННЫЙ СЧЕТЧИК

1.1Таблица истинности

Втаблице 1.1 представлена таблица истинности асинхронного

счетчика.

Таблица 1.1 – Таблица истинности

№ сигнала |

|

|

Выходы |

|

|

|

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

2 |

1 |

1 |

0 |

0 |

0 |

3 |

1 |

0 |

1 |

1 |

1 |

4 |

1 |

0 |

1 |

1 |

0 |

5 |

1 |

0 |

1 |

0 |

1 |

6 |

1 |

0 |

1 |

0 |

0 |

7 |

1 |

0 |

0 |

1 |

1 |

8 |

1 |

0 |

0 |

1 |

0 |

9 |

1 |

0 |

0 |

0 |

1 |

10 |

1 |

0 |

0 |

0 |

0 |

11 |

0 |

1 |

1 |

1 |

1 |

12 |

0 |

1 |

1 |

1 |

0 |

13 |

0 |

1 |

1 |

0 |

1 |

14 |

0 |

1 |

1 |

0 |

0 |

15 |

0 |

1 |

0 |

1 |

1 |

16 |

0 |

1 |

0 |

1 |

0 |

17 |

0 |

1 |

0 |

0 |

1 |

18 |

0 |

1 |

0 |

0 |

0 |

19 |

0 |

0 |

1 |

1 |

1 |

20 |

0 |

0 |

1 |

1 |

0 |

21 |

0 |

0 |

1 |

0 |

1 |

22 |

0 |

0 |

1 |

0 |

0 |

23 |

0 |

0 |

0 |

1 |

1 |

24 |

0 |

0 |

0 |

1 |

0 |

25 |

0 |

0 |

0 |

0 |

1 |

26 |

0 |

0 |

0 |

0 |

0 |

1.2Функциональная схема

3

На рисунке 1.1 представлена функциональная схема асинхронного счетчика.

Рисунок 1.1 - Схема асинхронного счетчика

1.2Моделирование функциональной схемы

На рисунках 1.2–1.3 представлены результат моделирования в двух режимах.

Рисунок 1.2 - Результат моделирования (Timing)

Рисунок 1.3 - Результат моделирования (Functional)

Результат моделирования совпадает со значениями из таблицы функционирования, представленной в таблице 1.1.

4

1.3Код на HDL

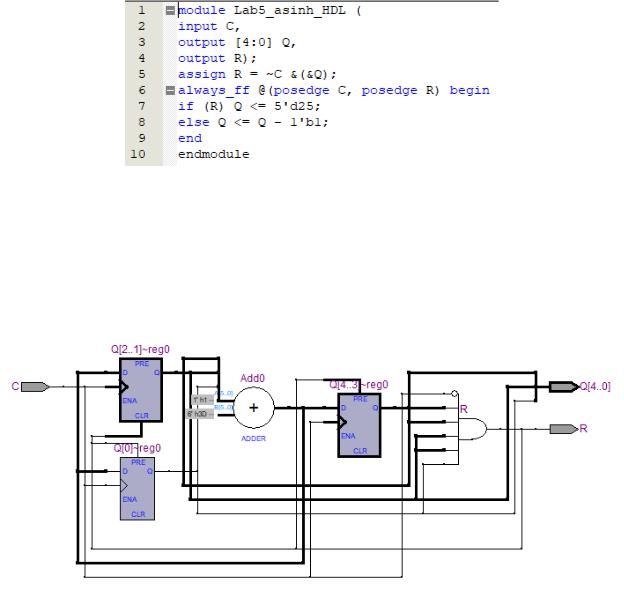

На рисунке 1.4 представлен код описания на System Verilog.

Рисунок 1.4 – Код описания устройства на System Verilog

1.4Схема из RTL viewer для кода HDL

На рисунке 1.5 представлена схема из RTL Viewer для кода,

написанном на System Verilog.

Рисунок 1.5 – Схема из RTL viewer

1.5Моделирование устройства, описанного кодом HDL

На рисунках 1.6–1.7 представлены результаты моделирования асинхронного счётчика, описанного на System Verilog.

5

Рисунок 1.6 - Результат моделирования (Timing)

Рисунок 1.7 - Результат моделирования (Functional)

Результат моделирования совпадает со значениями из таблицы истинности, представленной в таблице 1.1.

2.СИНХРОННЫЙ СЧЕТЧИК

2.1 Таблица истинности

Втаблице 2.1 представлена таблица истинности синхронного счетчика.

6

Таблица 2.1 – Таблица истинности

|

Вход |

|

|

Выходы |

|

|

№ сигнала |

CLR |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

0 |

1 |

1 |

4 |

0 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

0 |

0 |

1 |

0 |

1 |

6 |

0 |

0 |

0 |

1 |

1 |

0 |

7 |

0 |

0 |

0 |

1 |

1 |

1 |

8 |

0 |

0 |

1 |

0 |

0 |

0 |

9 |

0 |

0 |

1 |

0 |

0 |

1 |

10 |

0 |

0 |

1 |

0 |

1 |

0 |

11 |

0 |

0 |

1 |

0 |

1 |

1 |

12 |

0 |

0 |

1 |

1 |

0 |

0 |

13 |

0 |

0 |

1 |

1 |

0 |

1 |

14 |

0 |

0 |

1 |

1 |

1 |

0 |

15 |

0 |

0 |

1 |

1 |

1 |

1 |

16 |

0 |

1 |

0 |

0 |

0 |

0 |

17 |

0 |

1 |

0 |

0 |

0 |

1 |

18 |

0 |

1 |

0 |

0 |

1 |

0 |

19 |

0 |

1 |

0 |

0 |

1 |

1 |

20 |

0 |

1 |

0 |

1 |

0 |

0 |

21 |

0 |

1 |

0 |

1 |

0 |

1 |

22 |

0 |

1 |

0 |

1 |

1 |

0 |

23 |

0 |

1 |

0 |

1 |

1 |

1 |

24 |

0 |

1 |

1 |

0 |

0 |

0 |

25 |

0 |

1 |

1 |

0 |

0 |

1 |

26 |

0 |

1 |

1 |

0 |

1 |

0 |

27 |

0 |

1 |

1 |

0 |

1 |

1 |

28 |

0 |

1 |

1 |

1 |

0 |

0 |

29 |

0 |

1 |

1 |

1 |

0 |

1 |

30 |

0 |

1 |

1 |

1 |

1 |

0 |

31 |

0 |

0 |

0 |

0 |

0 |

0 |

32 |

0 |

0 |

0 |

0 |

0 |

1 |

33 |

1 |

0 |

0 |

0 |

0 |

0 |

34 |

0 |

0 |

0 |

0 |

0 |

1 |

2.2Функциональная схема

7

На рисунке 2.1 представлена функциональная схема синхронного счетчика.

Рисунок 2.1 - Схема синхронного счетчика

2.3 Моделирование функциональной схемы

На рисунках 2.2–2.3 представлены результат моделирования в двух режимах.

Рисунок 2.2 - Результат моделирования (Timing)

Рисунок 2.3 - Результат моделирования (Functional)

Результат моделирования совпадает со значениями из таблицы функционирования, представленной в таблице 2.1.

2.4 Код на HDL

8

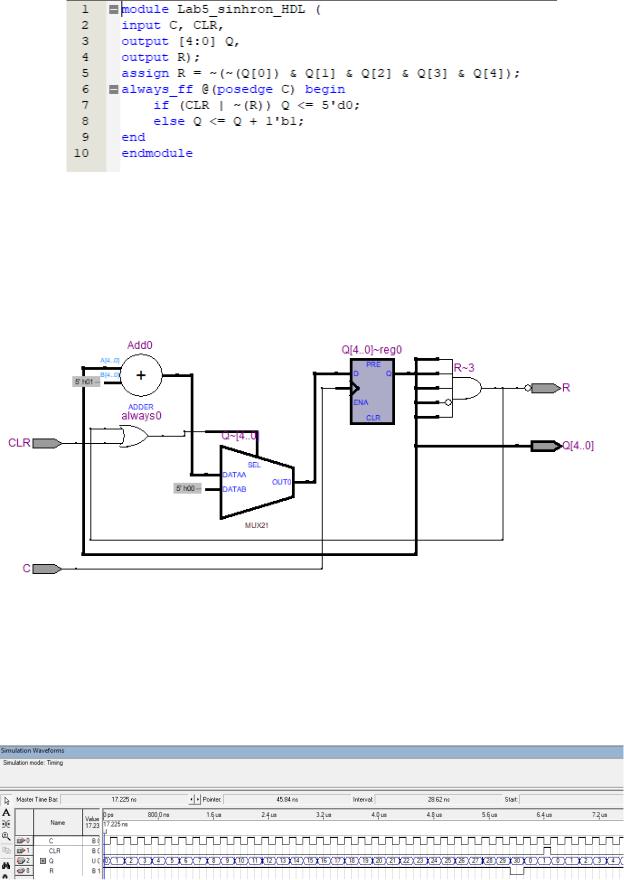

На рисунке 2.4 представлен код описания на System Verilog.

Рисунок 2.4 – Код описания устройства на System Verilog

2.5Схема из RTL viewer для кода HDL

На рисунке 2.5 представлена схема из RTL Viewer для кода,

написанном на System Verilog.

Рисунок 2.5 – Схема из RTL viewer

2.6Моделирование устройства, описанного кодом HDL

На рисунках 2.6–2.7 представлены результаты моделирования асинхронного счётчика, описанного на System Verilog.

Рисунок 2.6 - Результат моделирования (Timing)

9

Рисунок 2.7 - Результат моделирования (Functional)

Результат моделирования совпадает со значениями из таблицы истинности, представленной в таблице 2.1.

3.ДЕЛИТЕЛЬ ЧАСТОТЫ

3.1Расчеты

Ниже приведены расчёты для задачи делителя частоты: Твх = 20 нс

Fвых = 2173913 Гц

Твых = Fвых1 109 = 460 нс

М = ТвыхТвх = 23

3.2Функциональная схема

На рисунке 3.1 представлена функциональная схема делителя частоты.

Рисунок 3.1 - Схема делителя частоты

10