Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Отчет по лабораторной работе №1 по дисциплине «Электроника и схемотехника»

Вариант № 12

Студент гр.

**.**.2022

Руководитель

*** кафедры КИБЭВС

_______

**.**.2022

Томск 2022

Введение

Цель работы - изучение основных инструментов САПР Quartus II и

получение навыков моделирования в программе работы схем на основе простых логических элементов.

Поставленные задачи:

−Собрать на холсте схемы 2И, 2ИЛИ, 2искл.ИЛИ, 2И-НЕ и

2ИЛИ-НЕ, а также описать элементы на HDL и промоделировать работы схем.

− Собрать на холсте схему, выданную по варианту, а также описать элементы на HDL и промоделировать работы схем.

2

1 УСТРОЙСТВО 2И

1.1Таблица истинности

Втаблице ниже представлена таблица истинности для данного устройства (X1 и X2 входы, Y – выход)

Таблица 1.1 – Таблица истинности устройства 2И

X1 |

|

X2 |

Y |

|

|

|

|

0 |

|

0 |

0 |

|

|

|

|

1 |

|

0 |

0 |

|

|

|

|

0 |

|

1 |

0 |

|

|

|

|

1 |

|

1 |

1 |

|

|

|

|

1.2 |

Формула |

|

|

Формула для описания этой схемы будет иметь вид: Y = X1 ˄ X2.

1.3Функциональная схема

На рисунке 1.1 представлена схема устройства 2И.

Рисунок 1.1 – Схема устройства 2И

Как и подразумевалось в формуле есть два входа X1 и X2, с них сигналы поступают на логический элемент и на выходе Y получается результирующий сигнал. Достаточно подать хотя бы один 0 на вход, чтобы на выходе получить

0.

1.4Код на HDL

На рисунке 1.2 представлен код на HDL.

3

Рисунок 1.2 – Устройства на языке описания аппаратуры

1.5Моделирование

На рисунке 1.3 представлено моделирование в режиме Timing.

Рисунок 1.3 – Моделирование (Timing)

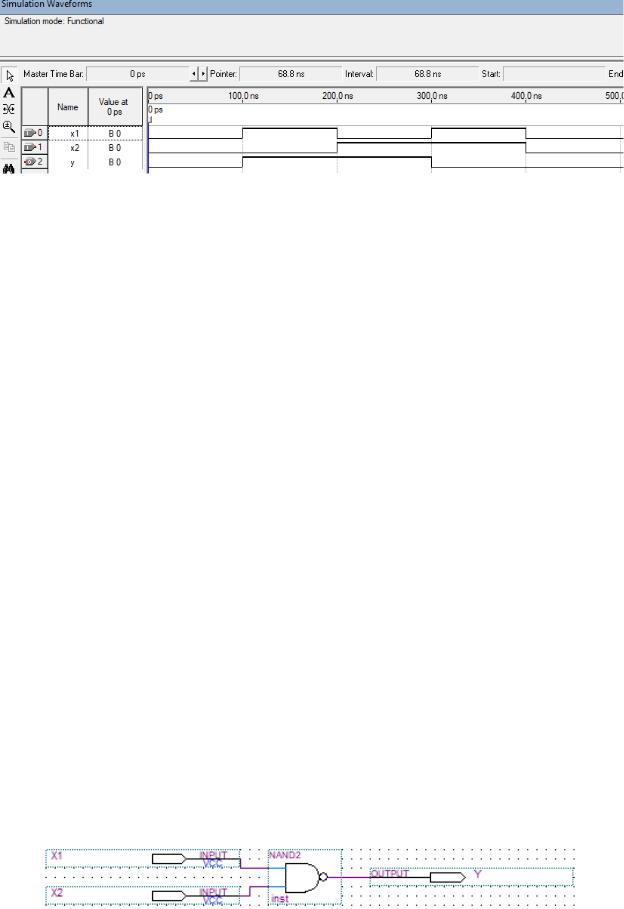

На рисунке 1.4 представлено моделирование в режиме Functional.

Рисунок 1.4 – Моделирование (Functional)

Как видно сигналы немного отличаются: в режиме Timing есть резкие перемены выходного сигнала. Это происходит потому, что входы расположены на разном расстоянии от логического элемента. Таким образом может произойти ситуация, что один сигнал еще не успел поменяться, а второй уже изменил свое значение.

4

На рисунках 1.5 и 1.6 будут представлены моделирования схем,

описанных на HDL, чтобы удостовериться, что схемы составлены идентично.

Рисунок 1.5 – Моделирование HDL (Timing)

Рисунок 1.6 – Моделирование HDL (Functional)

Моделирования соответствуют таблице истинности (для устройств).

2УСТРОЙСТВО 2ИЛИ

2.1Таблица истинности

Втаблице ниже представлена таблица истинности для данного устройства.

Таблица 2.1 – Таблица истинности устройства 2ИЛИ

X1 |

X2 |

Y |

|

|

|

0 |

0 |

0 |

|

|

|

1 |

0 |

1 |

|

|

|

0 |

1 |

1 |

|

|

|

1 |

1 |

1 |

|

|

|

|

5 |

|

2.2Формула

Формула для описания этой схемы будет иметь вид: Y = X1 ˅ X2.

2.3Функциональная схема

На рисунке 2.1 представлена схема устройства 2ИЛИ.

Рисунок 2.1 – Схема устройства 2ИЛИ

Элемент имеет входы X1 и X2 и выход Y. Достаточно подать хотя бы один 1 на вход, чтобы на выходе получить 1.

2.4Код на HDL

На рисунке 2.2 представлен код на HDL.

Рисунок 2.2 – Устройства на языке описания аппаратуры

2.5Моделирование

На рисунке 2.3 представлено моделирование в режиме Timing.

Рисунок 2.3 – Моделирование (Timing) 6

На рисунке 2.4 представлено моделирование в режиме Functional.

Рисунок 2.4 – Моделирование (Functional)

На рисунках 2.5 и 2.6 будут представлены моделирования схем,

описанных на HDL, чтобы удостовериться, что схемы составлены идентично.

Рисунок 2.5 – Моделирование HDL (Timing)

Рисунок 2.6 – Моделирование HDL (Functional)

Моделирования соответствуют таблице истинности (для устройств).

3УСТРОЙСТВО 2ИСКЛ.ИЛИ

3.1Таблица истинности

7

В таблице ниже представлена таблица истинности для данного

устройства.

Таблица 3.1 – Таблица истинности устройства 2искл.ИЛИ

X1 |

|

X2 |

Y |

|

|

|

|

0 |

|

0 |

0 |

|

|

|

|

1 |

|

0 |

1 |

|

|

|

|

0 |

|

1 |

1 |

|

|

|

|

1 |

|

1 |

0 |

|

|

|

|

3.2 |

Формула |

|

|

Формула для описания этой схемы будет иметь вид: Y = X1 X2.

3.3Функциональная схема

На рисунке 3.1 представлена схема устройства 2искл.ИЛИ.

Рисунок 3.1 – Схема устройства 2искл.ИЛИ

Элемент имеет входы X1 и X2 и выход Y. На выходе будет 1 только тогда, когда на входы подаются разные сигналы.

3.4Код на HDL

На рисунке 3.2 представлен код на HDL.

Рисунок 3.2 – Устройства на языке описания аппаратуры

8

3.5Моделирование

На рисунке 3.3 представлено моделирование в режиме Timing.

Рисунок 3.3 – Моделирование (Timing)

На рисунке 3.4 представлено моделирование в режиме Functional.

Рисунок 3.4 – Моделирование (Functional)

На рисунках 3.5 и 3.6 будут представлены моделирования схем,

описанных на HDL, чтобы удостовериться, что схемы составлены идентично.

Рисунок 3.5 – Моделирование HDL (Timing)

9

Рисунок 3.6 – Моделирование HDL (Functional)

Моделирования соответствуют таблице истинности (для устройств).

4УСТРОЙСТВО 2И-НЕ

4.1Таблица истинности

Втаблице ниже представлена таблица истинности для данного устройства.

Таблица 4.1 – Таблица истинности устройства 2И-НЕ

X1 |

X2 |

Y |

|

|

|

0 |

0 |

1 |

|

|

|

1 |

0 |

1 |

|

|

|

0 |

1 |

1 |

|

|

|

1 |

1 |

0 |

|

|

|

4.2 Формула

Формула для описания этой схемы будет иметь вид: Y = ̅̅̅̅̅̅̅̅̅̅X1 ˄ X2.

4.3Функциональная схема

На рисунке 4.1 представлена схема устройства 2И-НЕ.

Рисунок 4.1 – Схема устройства 2И-НЕ

10