Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

МУЛЬТИПЛЕКСОРЫ И ДЕМУЛЬТИПЛЕКСОРЫ

Отчет по лабораторной работе №3 по дисциплине «Электроника и схемотехника»

Вариант № 12

Студент гр.

==.==.2022

Руководитель

== кафедры КИБЭВС

_______

==.==.2022

Томск 2022

Введение

Цель работы - получить навыки создания мультиплексоров и демультиплексоров на разных базисах, а также реализовать функции на мультиплексоре и демультиплексоре.

Поставленные задачи:

Собрать на холсте схемы мультиплексора 4–1 (на базисе И-НЕ), на его основе мультиплексор 8–2, демультиплексор 1-8 (на базисе ИЛИ-НЕ), на его основе демультиплексор 1-16, а также описать элементы на HDL и

промоделировать работы схем.

Собрать на холсте схему для выражения ̅̅̅̅̅ на основе

F = xΛy z w

мультиплексора и дешифратора, промоделировать работы схем.

2

1.МУЛЬТИПЛЕКСОР 4–1

1.1Таблица истинности

Мультиплексор – это функциональный узел, осуществляющий подключение (коммутацию) одного из нескольких входов данных к выходу под управлением управляющего (адресующего) слова.

Таблица 1.1 отражает таблицу истинности для мультиплексора 4–1.

Таблица 1.1 – Таблица истинности мультиплексора 4–1.

|

|

|

Входы |

|

|

|

Выходы |

E |

D3 |

D2 |

D1 |

D0 |

a1 |

a0 |

F |

1 |

x |

x |

x |

b0 |

0 |

0 |

b0 |

1 |

x |

x |

b1 |

x |

0 |

1 |

b1 |

1 |

x |

b2 |

x |

x |

1 |

0 |

b2 |

1 |

b3 |

x |

x |

x |

1 |

1 |

b3 |

0 |

x |

x |

x |

x |

x |

x |

0 |

1.2Формула

По таблице истинности 1.1 составим формулы для выхода:

= ( ∩ 0 ∩ 1 ∩ 0) ( ∩ D1 ∩ 1 ∩ 0) ( ∩ D2 ∩ 1 ∩ 0) (

∩ D3 ∩ 1 0)

Приведенная формула в базисе И-НЕ:

= ( ∩ 0 ∩ 1 ∩ 0) ∩ ( ∩ 1 ∩ 1 ∩ 0) ∩ ∩ ( ∩ 2 ∩ 1 ∩ 0) ∩ ( ∩ 3 ∩ 1 0)

1.3Функциональная схема

На рисунке 1.1 представлена функциональная схема мультиплексора 4–

1.

3

Рисунок 1.1 – Функциональная схема мультиплексора 4–1

E, D[3..0], a[1..0] – являются входами, F – выходом, дающими результат схемы.

1.4Моделирование

На рисунке 1.2 представлено моделирование схемы в режиме Timing.

Рисунок 1.2 – Моделирование в режиме Timing

4

Так как моделирование в режиме Timing приближено к реальности и отображает задержки переключателя, из-за чего результат немного искажается от идеального. Сравнивания рисунок 1.2 и таблицу истинности 1.1, можно сделать вывод, что результаты совпадают.

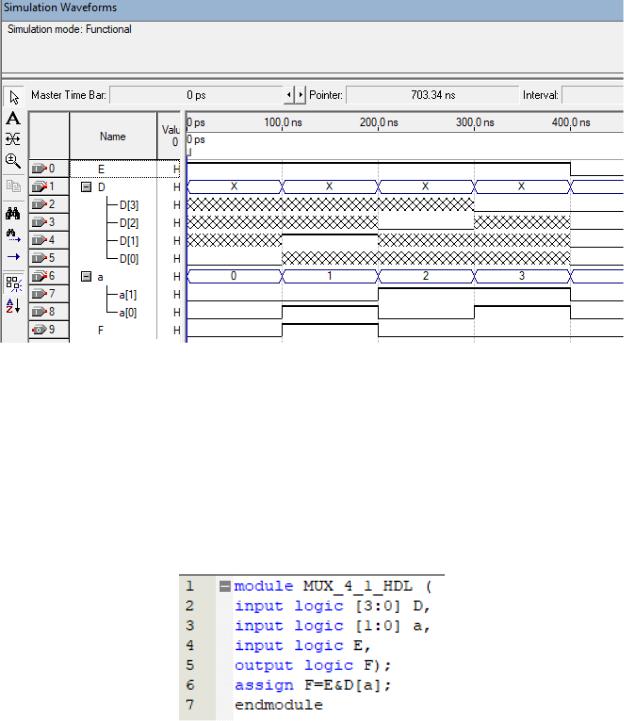

На рисунке 1.3 представлено моделирование схемы в режиме Functional.

Рисунок 1.3 - Моделирование в режиме Functional

Один временной интервал равняется 100 наносекунд. Если сравнивать моделирование в режиме Functional, то оно полностью совпадает с таблицей истинности.

1.5Код на HDL

Ниже на рисунке 1.4 представлен код схемы на SystemVerilog HDL:

Рисунок 1.4 – Код схемы

5

1.6Схема из RTL viewer для кода HDL

На рисунке 1.5 представлена схема для устройства MUX 8-1 из RTL

viewer.

Рисунок 1.5 – Схема устройства из RTL viewer

1.7Моделирование устройства, описанного кодом HDL

На рисунке 1.6 представлено моделирование устройства, описанного на

HDL, в режиме Timing.

Рисунок 1.6 – Моделирование MUX 4–1, описанного на SystemVerilog HDL (Timing)

6

1.8Таблица истинности масштабируемого устройства

Втаблице 1.2 представлена таблица истинности масштабируемого устройства MUX 8–2.

Таблица 1.2 – Таблица истинности MUX 8–2

|

|

|

|

|

Входы |

|

|

|

|

|

Выходы |

||

E1 |

E2 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

a1 |

a0 |

F1 |

F2 |

1 |

1 |

x |

x |

x |

b4 |

x |

x |

x |

b0 |

0 |

0 |

b4 |

b0 |

1 |

1 |

x |

x |

b5 |

x |

x |

x |

b1 |

x |

0 |

1 |

b5 |

b1 |

1 |

1 |

x |

b6 |

x |

x |

x |

b2 |

x |

x |

1 |

0 |

b6 |

b2 |

1 |

1 |

b7 |

x |

x |

x |

b3 |

x |

x |

x |

1 |

1 |

b7 |

b3 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

1.9Функциональная схема масштабируемого устройства

На рисунке 1.7 представлена схема устройства MUX 8–2, построенного на основе MUX 4–1.

Рисунок 1.7 – Функциональная схема MUX 8–2

1.10 Моделирование масштабируемого устройства

На рисунках 1.8 и 1.9 представлено моделирование MUX 8–2 в двух режимах.

7

Рисунок 1.8 – Моделирование MUX 8–2 (Timing)

Рисунок 1.9 – Моделирование MUX 8–2 (Functional)

Результаты моделирования совпадают с таблицей истинности.

8

1.11 Код на HDL масштабируемого устройства

На рисунке 1.10 представлено описание устройства на SystemVerilog

HDL.

Рисунок 1.10 – MUX 8–2 на SystemVerilog HDL

1.12 Схема из RTL viewer для кода HDL масштабируемого устройства

На рисунке 1.11 представлена схема для устройства MUX 16-2 из RTL

viewer.

Рисунок 1.11 – Схема устройства из RTL viewer

1.13 Моделирование масштабируемого устройства, описанного кодом

HDL

На рисунке 1.12 представлено моделирование устройства, описанного на

HDL, в режиме Timing.

9

Рисунок 1.12 – Моделирование MUX 8–2, описанного на SystemVerilog HDL (Timing)

Результаты моделирования совпадают с таблицей истинности.

10