- •Часть 1

- •Часть 1

- •Введение 5

- •4.2.1. Обзор альтернативных решений 92

- •1. Проблемы проектрования фильтров с конечной импульсной характеристикой

- •1.1. Фильтры с конечной импульсной характеристикой

- •В большинстве приложений используются нерекурсивные фильтры с точно линейной фчх. Для такого фильтра передаточная функция имеет вид:

- •1.2. Синтез передаточных функций цифровых ких-фильтров в области дискретных и целочисленных значений коэффициентов

- •1.2.1. Критерии оптимальности решения

- •1.2.2. Начальные приближения

- •1.3. Основные этапы проектирования ких-фильтров

- •1.5. Пути повышения быстродействия устройств цифровой обработки сигналов в интегральном исполнении с применением модулярной арифметики

- •2. Варианты реализации цифрового фильтра

- •2.1. Цифровой ких-фильтр с единичными коэффициентами

- •2.2. Цифровой ких-фильтр с коэффициентами вида 2n

- •3. Методика проектирования цифровых ких-фильтров

- •3.1. Основные свойства и понятия модулярной арифметики

- •3.2. Структура устройств цифровой обработки сигналов в модулярной арифметике

- •3.3. Основные вычислительные процедуры в устройствах цифровой обработки сигналов и особенности их аппаратной реализации

- •3.2.1. Принципы построения модулярных сумматоров.

- •3.4. Вариация исходных параметров взвешенной чебышевской аппроксимации в задаче синтеза ких-фильтров без умножителей

- •3.4.1. Постановка задачи

- •3.4.2. Предварительные замечания

- •3.4.3. Возможные алгоритмы

- •3.4.4. Примеры синтеза

- •3.5. Синтез цифровых ких-фильтров без умножителей с помощью генетических алгоритмов

- •3.5.1. Введение

- •3.5.2. Применение генетических алгоритмов к синтезу фильтров

- •3.5.3. Выводы и будущие исследования

- •4. Применение цпос и плис для систем защиты информации

- •4.1. Использование плис в системах защиты информации

- •4.1.1. Способы защиты информации

- •4.1.2. Средства защиты информации

- •4.1.3. Разовые расходы на проектирование и внедрение в производство

- •4.1.4. Производительность

- •4.1.5. Цена

- •4.1.6. Настраиваемость

- •4.1.7. Масштабируемость

- •4.1.8. Доступность

- •4.1.9. Защищенность от взлома

- •4.1.10. Возможность перепрограммирования

- •4.2. Постановка проблемы

- •4.2.1. Обзор альтернативных решений

- •4.3. Описание реализации

- •4.3.1. Блок управления

- •4.3.2. Блок оценки частоты помехи

- •4.3.3. Канал обработки

- •Для уменьшения неравномерности предлагается следующая структура построения фнч канала обработки. Структурная схема фнч канала обработки представленная на рис. 4.11.

- •4.3.4. Выходное ару

- •4.4. Тестирование и заключение

- •1. Модульная схема программы

- •2. Описание программы

- •3. Руководство пользователя

- •Рис п.3. Главное окно программы

- •4. Анализ результатов работы программы

- •Параметры ачх для однородного цифрового фильтра с ких

- •Часть 1

- •394026 Воронеж, Московский просп., 14

1.5. Пути повышения быстродействия устройств цифровой обработки сигналов в интегральном исполнении с применением модулярной арифметики

Проблема повышения быстродействия в системах, функционирующих в реальном времени, может быть решена не только за счет повышения степени интеграции схем и, соответственно, увеличения тактовых частот, но и за счет распараллеливания вычислительных операций. Модулярное представление (которое также называют представлением в системе остаточных классов или системе классов вычетов) является одним из возможных способов построения параллельных вычислительных архитектур. В этом случае целое число представляется как упорядоченный набор остатков в соответствующем базисе взаимно попарно простых чисел, называемых модулями, и арифметические операции сложения, вычитания и умножения выполняются уже с этими вычетами меньшей разрядности независимо друг от друга.

Литература по вычислительным устройствам в модулярной арифметике, опубликованная в нашей стране, была ориентирована главным образом на разработку компьютеров в целом /1, 2/. Данное направление не получило в дальнейшем широкого распространения в связи с развитием интегральных технологий, которые и без распараллеливания позволяли увеличивать быстродействие на основе традиционного позиционного представления данных в компьютерных системах.

В настоящее время отдельные элементы модулярной арифметики, такие как модулярные сумматоры и модулярные умножители, находят широкое применение в криптографии /3—5/ и при построении отказоустойчивых систем /6, 7/.

Также существуют и реальные коммерческие продукты в интегральном исполнении, использующие модулярный подход в конкретных применениях. Так, например, фирмой IВМ был разработан универсальный вычислитель ENYERPRISE SYSTEM/9000, использующий остаточный код по модулю 15 /8/.

В работе /9/ представлен сигнальный процессор IMS А110, фактически представляющий собой двумерный цифровой фильтр/вычислитель свертки, функционирующий в модулярной арифметике. Разработчики выбрали подход на основе модулярного представления, так как было затруднительно соответствовать требованиям по занимаемой площади и по мощности при использовании обычной двоичной арифметики.

Целью данной работы является рассмотрение и анализ основных вычислительных процедур, используемых при построении устройств цифровой обработки сигналов в модулярной арифметике с учетом их реализации в интегральном исполнении.

2. Варианты реализации цифрового фильтра

2.1. Цифровой ких-фильтр с единичными коэффициентами

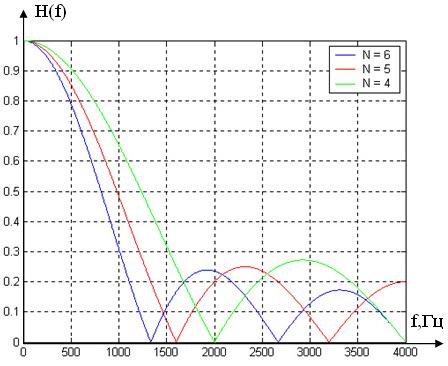

Для реализации ФНЧ будем использовать каскадное соединение нескольких фильтров различного порядка. При выборе максимального порядка фильтров необходимо руководствоваться следующими соображениями:

Первый ноль передаточной функции фильтра должен располагаться в окрестности частоты подавления синтезируемого фильтра.

Коэффициент передачи на частоте среза должен быть максимально возможным.

Прировняв к нулю числитель, в формуле амплитудно-частотная характеристика однородного фильтра N-го порядка найдем порядок фильтра, у которого ноль передаточной характеристики приходится на частоту подавления:

![]() ,

,

![]() , где n – целое число

, где n – целое число

Так как нас интересует первый ноль, то принимаем n = 1. Тогда

Таким образом, порядок фильтра может быть 6 или 7. Однако при N = 7 коэффициент передачи фильтра на частоте среза в соответствии с формулой амплитудно-частотная характеристика однородного фильтра N-го порядка составит 0,611, а при N = 6 0,707. Следовательно, выбираем N = 6. Таким образом, первый каскад синтезируемого ФНЧ будет представлять собой фильтр с единичными коэффициентами шестого порядка. Фильтры в остальных каскадах должны иметь порядок меньший, чем 6. Подберем число каскадов и порядки фильтров в них. Для моделирования ФНЧ воспользуемся системой MATLAB 6.5.

Рис. 2.1. АЧХ каскадов ФНЧ

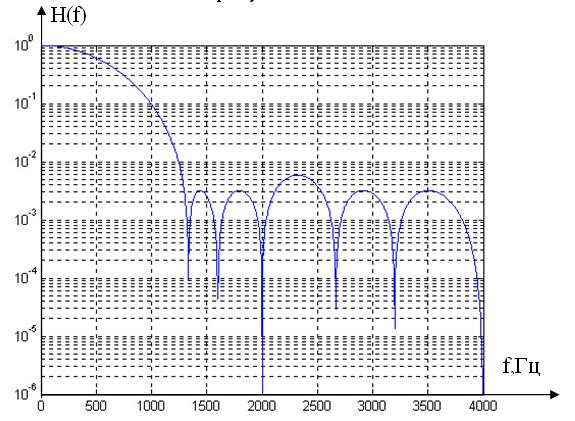

Рис. 2.2. Результирующая АЧХ

По результатам моделирования необходимое подавление достигается при числе каскадов равном трем, порядки фильтров в каскадах равны 6, 5 и 4. АЧХ каскадов, показаны, на рис. 2.1. Результирующая АЧХ показана на рис. 2.2.

Для оценки занимаемых фильтром ресурсов ПЛИС смоделируем фильтр в САПр MAXPLUS II. Структурная схема одного из каскадов фильтра (фильтр с единичными коэффициентами шестого порядка) показана на рис. 2.3.

Р ис.

2.3. Структурная схема каскада ФНЧ

ис.

2.3. Структурная схема каскада ФНЧ

Как видно из рисунка входной сигнал сначала умножается на 1/6, но так как и при реализации цифровых фильтров в ПЛИС удобнее иметь дело с целыми числами, то умножение на 1/6 необходимо свести к умножению на целое число. Для этого число 1/6 необходимо представить в виде дроби со знаменателем вида 2N, где N – натуральное число. В данном случае 1/6 ≈ 43/256. Таким образом, умножение отсчета сигнала на 1/6 сводится к умножению на 43 и делению на 256. Деление на 256 можно произвести путем числа на 8 разрядов вправо. Еще одной особенностью реализации фильтра в ПЛИС является то, что умножение на –1 осуществляется за счет того, что последующий сумматор делается вычитающим.

Остальные каскады ФНЧ реализуются аналогично, за исключением каскада четвертого порядка, в котором отсутствует входной умножитель, так как умножение на 1/4 сводится к сдвигу числа на 2 разряда вправо.

По результатам моделирования фильтр при восьмиразрядном входном сигнале требует для реализации следующие ресурсы ПЛИС:

128 триггеров;

248 вентилей.