- •Часть 1

- •Часть 1

- •Введение 5

- •4.2.1. Обзор альтернативных решений 92

- •1. Проблемы проектрования фильтров с конечной импульсной характеристикой

- •1.1. Фильтры с конечной импульсной характеристикой

- •В большинстве приложений используются нерекурсивные фильтры с точно линейной фчх. Для такого фильтра передаточная функция имеет вид:

- •1.2. Синтез передаточных функций цифровых ких-фильтров в области дискретных и целочисленных значений коэффициентов

- •1.2.1. Критерии оптимальности решения

- •1.2.2. Начальные приближения

- •1.3. Основные этапы проектирования ких-фильтров

- •1.5. Пути повышения быстродействия устройств цифровой обработки сигналов в интегральном исполнении с применением модулярной арифметики

- •2. Варианты реализации цифрового фильтра

- •2.1. Цифровой ких-фильтр с единичными коэффициентами

- •2.2. Цифровой ких-фильтр с коэффициентами вида 2n

- •3. Методика проектирования цифровых ких-фильтров

- •3.1. Основные свойства и понятия модулярной арифметики

- •3.2. Структура устройств цифровой обработки сигналов в модулярной арифметике

- •3.3. Основные вычислительные процедуры в устройствах цифровой обработки сигналов и особенности их аппаратной реализации

- •3.2.1. Принципы построения модулярных сумматоров.

- •3.4. Вариация исходных параметров взвешенной чебышевской аппроксимации в задаче синтеза ких-фильтров без умножителей

- •3.4.1. Постановка задачи

- •3.4.2. Предварительные замечания

- •3.4.3. Возможные алгоритмы

- •3.4.4. Примеры синтеза

- •3.5. Синтез цифровых ких-фильтров без умножителей с помощью генетических алгоритмов

- •3.5.1. Введение

- •3.5.2. Применение генетических алгоритмов к синтезу фильтров

- •3.5.3. Выводы и будущие исследования

- •4. Применение цпос и плис для систем защиты информации

- •4.1. Использование плис в системах защиты информации

- •4.1.1. Способы защиты информации

- •4.1.2. Средства защиты информации

- •4.1.3. Разовые расходы на проектирование и внедрение в производство

- •4.1.4. Производительность

- •4.1.5. Цена

- •4.1.6. Настраиваемость

- •4.1.7. Масштабируемость

- •4.1.8. Доступность

- •4.1.9. Защищенность от взлома

- •4.1.10. Возможность перепрограммирования

- •4.2. Постановка проблемы

- •4.2.1. Обзор альтернативных решений

- •4.3. Описание реализации

- •4.3.1. Блок управления

- •4.3.2. Блок оценки частоты помехи

- •4.3.3. Канал обработки

- •Для уменьшения неравномерности предлагается следующая структура построения фнч канала обработки. Структурная схема фнч канала обработки представленная на рис. 4.11.

- •4.3.4. Выходное ару

- •4.4. Тестирование и заключение

- •1. Модульная схема программы

- •2. Описание программы

- •3. Руководство пользователя

- •Рис п.3. Главное окно программы

- •4. Анализ результатов работы программы

- •Параметры ачх для однородного цифрового фильтра с ких

- •Часть 1

- •394026 Воронеж, Московский просп., 14

4.1.6. Настраиваемость

В данной категории микросхемы ASIC и FPGA имеют значительное преимущество перед ASSP, поскольку изначально их легче наделить теми специфическими свойствами, которые разработчик ставит целью заложить в создаваемую им архитектуру. Это преимущество выражается как в поддержке многочисленных алгоритмов, не реализованных для ASSP, так и в наличии нужных разработчику свойств для управления ИТ-системой пли настройке под конкретную задачу. Проще говоря, эти качества позволяют создать устройство с уникальными свойствами и благодаря тому обойти конкурентов.

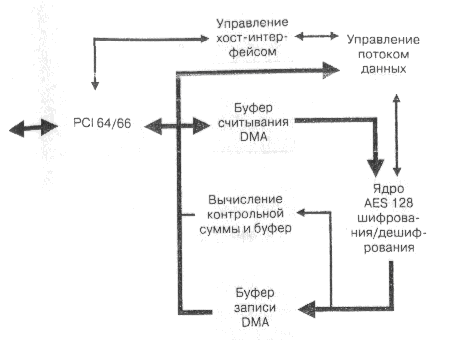

Рис. 4.3. Базовый AES-сопроцессор

Для примера рассмотрим основной сопроцессор улучшенного стандарта шифрования AES. Если использовать только основной сопроцессор, никакого преимущества получить не удается (см. рис. 4.3). Однако если использовать систему защиты данных, скажем, для архива па магнитных лептах, то можно придать системе дополнительные свойства и настроить ее архитектуру, получив, таким образом, платформу более высокого уровня.

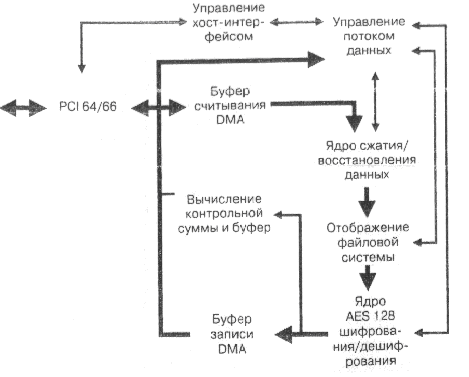

В рассматриваемом приме ре этими свойствами могут быть новейшим код AES-GCM шифрования дешифрования использование компрессии восстановления данных па маршруте передачи данных, а также подсистемы отображения блоков данных с обратной связью для сохранения целостности файловом системы, что обеспечивает интегрированное решение с возможностью его настройки под конкретные задачи (см. рис. 4.4). Преимущества этого решения особенно очевидны при сравнении с аналогичной системой на основе ASSP

4.1.7. Масштабируемость

Масштабируемость, определяется количеством возможных вариантов соотношения цена производительность для одной архитектуры. Программные средства легко масштабируемы, однако вследствие того, что их производительность снижается по мере увеличения сложности, эти средства трудно использовать на практике. В качестве одного из выходов можно предложить масштабировать производительность платформы хост-процессора, но в этом случае могут возникнуть проблемы, связанные с типом и скоростью памяти, чипсетом и стоимостью. Микросхемы ASIC также плохо масштабируются, так как обычно они заранее предназначаются для какой то определенной области применения. ASSP имеют различные варианты соотношения цена производительность для совместимых корпусов и, таким образом, обеспечивают хороший уровень масштабируемости на уровне плат.

Рис. 4.4. Архив на магнитных лентах на базе сопроцессора:

использует AES-GSM ядро шифрования/дешифрования;

использует встроенное в маршрут передачи данных ядро сжатия/восстановления данных;

поддерживает целостность файловой системы.

Для FPGA можно обнаружить самые разнообразные варианты соотношения цена производительность, которые следует рассматривать в трех аспектах:

необходимые пользователю кон фигурации логики;

широкий выбор микросхем FPGA с различными функциональными возможностями;

исключительная возможность модификации и повторного использования проектов, реализованных на микросхемах FPGA.

В самом простом случае, загружая различные конфигурации в FPGA, можно тем самым наделять ее различным набором необходимых функциональных свойств. В более сложном случае можно достичь масштабируемости на уровне плат, как и у ASSP, используя различные FPGA с совместимыми корпусами. Это позволит увеличить производительность и расширить функциональные возможности платы. Ну и в самом сложном случае пользователь может сам модифицировать функциональное ядро системы в сторону ее расширения и адаптации под различные варианты применения и удовлетворения тем самым требований рынка. В качестве примера здесь можно привести архитектуру «data at rest» па маршруте передачи данных, адаптированную под различные стандарты портов, такие как Gigabit Ethernet, 10 Gigabit Ethernet, Fibre Channel и SAS, что сделало возможным применение этой архитектуры в устройствах хранения данных.