- •ВВЕДЕНИЕ

- •1. ОБЗОР НАУЧНО-ТЕХНИЧЕСКОЙ ЛИТЕРАТУРЫ

- •2.1. Комплектующие

- •2.1.1. Микроконтроллер

- •2.1.2. Шасси и электропривод

- •2.1.3. Радиомодуль

- •2.1.4. Датчик температуры и влажности воздуха

- •2.1.5. Инерциальный датчик

- •2.1.6. Модуль вычисления глобального местоположения

- •2.1.7. Ультразвуковой дальномер

- •2.1.8. Модуль измерения радиоактивного фона

- •2.2. Взаимодействие комплектующих

- •2.3. Сопряжение уровней логических сигналов

- •2.4. Интерфейс прямого доступа к памяти

- •2.5. Последовательный интерфейс UART микроконтроллера

- •2.6. Последовательный интерфейс i2c микроконтроллера

- •3.1. Многозадачность

- •3.2. Комбинированная многозадачность средствами ОСРВ

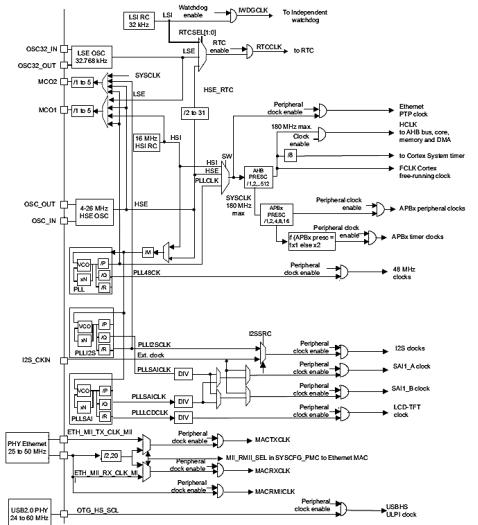

- •3.3. Управление тактовой частотой микроконтроллера

- •3.4. Работа с последовательным интерфейсом UART

- •3.5. Работа с последовательным интерфейсом I2C

- •3.6. Управление по радиоканалу

- •3.7. Вывод телеметрии

- •3.8. Передвижение роботизированного устройства

- •3.9. Измерение температуры и влажности воздуха

- •3.10. Вычисление ориентации в пространстве

- •3.10.1. Получение измерений инерциального датчика

- •3.10.2. Калибровка датчика

- •3.10.3. Преобразование данных инерциального датчика

- •3.11. Вычисление глобального местоположения

- •3.12. Следование по маршруту

- •3.12.1. Вычисление направления на точку маршрута

- •3.12.2. Удержание направления на точку маршрута

- •3.13. Программа дистанционного управления

- •3.13.1. Описание программы

- •ЗАКЛЮЧЕНИЕ

- •БИБЛИОГРАФИЧЕСКИЙ СПИСОК

- •ПРИЛОЖЕНИЕ 1

- •Принципиальная электрическая схема отладочной платы

- •ПРИЛОЖЕНИЕ 2

- •Принципиальная электрическая схема драйвера электродвигателей

- •ПРИЛОЖЕНИЕ 3

- •Принципиальная электрическая схема радиомодуля

- •ПРИЛОЖЕНИЕ 4

- •ПРИЛОЖЕНИЕ 5

- •Принципиальная электрическая схема инерциального датчика

- •ПРИЛОЖЕНИЕ 6

- •Принципиальная электрическая схема датчика глобального местоположения

- •ПРИЛОЖЕНИЕ 7

- •Принципиальная электрическая схема ультразвукового дальномера

- •ПРИЛОЖЕНИЕ 8

- •Принципиальная электрическая схема измерителя радиации

- •ПРИЛОЖЕНИЕ 9

- •Принципиальная электрическая схема платы сопряжения

- •ПРИЛОЖЕНИЕ 10

- •Принципиальная электрическая схема Arduino DUE

- •Схема распиновки Arduino DUE

- •Редактор Е. А. Кусаинова

- •Подписано в печать 26.10.2020.

- •ФГБОУ ВО «Воронежский государственный технический университет»

- •394026 Воронеж, Московский просп., 14

LL_RCC_PLL_ConfigDomain_SYS(), LL_RCC_SetAHBPrescaler(), LL_RCC_Set APB1Prescaler(), LL_RCC_SetAPB2Prescaler(), и LL_RCC_SetSysClkSour-ce ().

Заключительным этапом включается PLL и ожидается установление его переходных процессов. На этом тактовая частота микроконтроллера считается настроенной и составляет 168 МГц.

Рис. 3.2. Схема тактирования микроконтроллера

Таким образом, рассмотрена система тактирования микроконтроллера. Описан процесс использования в качестве источника тактирования внешнего кварцевого резонатора. Рассмотрен процесс настройки тактовой частоты ядра и периферии.

3.4. Работа с последовательным интерфейсом UART

Для того, чтобы не нагружать микроконтроллер обработкой прерываний интерфейса UART, последний используется совместно с технологией ПДП.

49

Кроме того, данный подход позволяет использовать большие скорости передачи, а также более удобен в программировании.

Однако, прежде чем приступать к работе с интерфейсом, его необходимо инициализировать и настроить. Управление параметрами интерфейса осуществляется при помощи записи соответствующих значений в определенные регистры. Рассмотрим регистры интерфейса UART более подробно [5]. В табл. 3.1 показана структура регистра статуса (USART_SR). Биты с 16 по 31 являются зарезервированными и в таблице отсутствуют. Прочерк означает отсутствие значения. Символ «ч» показывает, что бит доступен только для чтения, символ «з» - только для записи. Соответственно, «ч/з» означает доступ и для чтения и для записи.

|

|

|

|

|

|

|

|

Таблица 3.1 |

||

|

|

|

Биты регистра USART_SR |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

Разряд |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

|

7 |

|

Назва- |

PE |

FE |

NF |

ORE |

IDLE |

RXNE |

TC |

|

TX |

|

ние |

|

|

|

|

|

|

|

|

E |

|

Доступ |

ч |

ч |

ч |

ч |

ч |

ч/з |

ч/з |

|

ч |

|

Разряд |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

|

15 |

|

Назва- |

LBD |

CTS |

- |

- |

- |

- |

- |

|

- |

|

ние |

|

|

|

|

|

|

|

|

|

|

Доступ |

ч/з |

ч/з |

- |

- |

- |

- |

- |

|

- |

|

Бит TXE устанавливается аппаратно после того, как содержимое регистра DR было передано в сдвиговый регистр интерфейса. Если данный бит установлен в единицу и разрешено соответствующее прерывание, то микроконтроллер начинает обработку данного прерывания. Значение единица свидетельствует о том, что данные были отправлены в сдвиговый регистр.

Бит TC сигнализирует об окончании передачи. Он устанавливается аппаратно, если установлен бит TXE и все данные из сдвигового регистра интерфейса были переданы. Единица означает, что передача завершена, ноль – передача не завершена.

RXNE – регистр чтения данных не пуст. Бит устанавливается аппаратно в случае, если содержимое сдвигового регистра интерфейса было записано в регистр DR. Если бит установлен в единицу и разрешено соответсвующее прерывание, то микроконтроллер начинает обработку данного прерывания. Значение ноль означает что принятых данных нет, единица означает наличие нового принятого байта данных.

Остальные биты регистра нет необходимости использовать в роботизированном устройстве, поэтому их описание не приводится.

Следующий регистр - USART_DR. Регистр является восьмиразрядным и используется для записи и чтения байтов данных. Если необходимо передать данные при помощи интерфейса, то необходимо в данный регистр записать пе-

50

редаваемое значение. При возникновении события приема данных (бит RXNE регистра USART_SR) значение регистра необходимо считать.

USART_BRR – регитстр управления скоростью передачи. Содержит целую и дробную часть делителя тактовой частоты микроконтроллера для формирования частоты работы интерфейса. Поле DIV_Fraction занимает биты с нулевого по третий и содержит дробную часть делителя. Поле DIV_Mantissa занимает биты с четвертого по пятнадцатый и содержит целую часть делителя.

USART_CR1 – регистр управления. Структура регистра приведена в табл. 3.2.

Таблица 3.2

Структура регистра USART_CR1

Разряд |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

Название |

SBK |

RWU |

RE |

TE |

IDLEI |

RXNEI |

TCIE |

TXEIE |

|

|

|

|

|

E |

E |

|

|

Доступ |

ч/з |

ч/з |

ч/з |

ч/з |

ч/з |

ч/з |

ч/з |

ч/з |

Разряд |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

Название |

PEIE |

PS |

PCE |

WAK |

M |

UE |

- |

OVER |

|

|

|

|

E |

|

|

|

8 |

Доступ |

ч/з |

ч/з |

ч/з |

ч/з |

ч/з |

ч/з |

- |

ч/з |

Бит OVER8 определяет режим размер выборки для приема данных интерфейсом. Ноль означает величину выборки в шестнадцать отсчетов, единица

– восемь.

Бит UE используется для разрешения работы интерфейса. Когда бит очищен, интерфейс переходит в режим пониженного энергопотребления и не реагирует на изменения значений других регистров.

Бит M определяет длину передаваемого слова данных. Значение ноль означает работу со словом длиной восемь бит, единица – девять бит.

Бит PCE включает либо выключает контроль четности данных интерфейса. Соответственно, если бит установлен в единицу, то после данных при передаче вставляется бит честности. При приеме также рассчитывается бит четности и сравнивается с переданным. Благодаря этому появляется возможность выявления некоторых ошибок при передаче.

Биты PEIE, TXEIE, TCIE, RXNEIE, IDLEIE используются для разрешения либо запрета прерываний при возникновении соответствующих событий в ре-

гистре USART_SR.

Бит TE осуществляет разрешение либо запрет работу передатчика интерфейса.

Бит RE осуществляет разрешение либо запрет работу приемника интерфейса.

51

В программе микроконтроллера предусмотрена специализированная функция для инициализации и настройки каждого интерфейса. Например, для работы с Bluetooth – MyBtInit (), для GPS – MyGpsInit (). Самым первым шагом в указанных функциях производится инициализация ПДП для приема и для передачи. В структуре DMA_InitStruct устанавливаются:

•канал передачи;

•направление передачи (из периферии в память или обратно);

•приоритет;

•адреса периферии и буферов в памяти;

•размер буферов и другие параметры.

После этого происходит вызов функции LL_DMA_Init () из библиотеки LL, в параметры которой передается указатель на структуру DMA_InitStruct и указатель на интерфейс ПДП. После проделанных манипуляций ПДП готова к использованию.

Следующим этапом настраиваются выводы микроконтроллера. Для этого параметры выводов заносятся в специализированную структуру GPIO_InitStruct (табл. 3.3).

|

Таблица 3.3 |

|

Параметры настройки выводов UART |

||

|

|

|

Параметр |

Значение |

|

Номера выводов порта |

Вывод приемника и передатчи- |

|

|

ка конкретного интерфейса |

|

Функция выводов |

Альтернативная |

|

Скорость работы выводов |

Высокая |

|

Тип выводов |

Push pull |

|

Подтяжка |

К напряжению питания |

|

После заполнения структуры GPIO_InitStruct происходит вызов функции LL_GPIO_Init () из библиотеки LL. В параметрах функции передается указатель на структуру, а также порт микроконтроллера.

И только после проделанных манипуляций можно производить настройку непосредственно UART. Для этого используется структура USART_InitStruct. Необходимо задать скорость передачи данных, количество стоповых бит, наличие бита четности, а также другие параметры при необходимости. После заполнения структуры вызывается функция LL_USART_Init (), в параметрах которой передается указатель на структуру, а также указатель на интерфейс UART микроконтроллера.

LL_DMA_Init (), LL_GPIO_Init () и LL_USART_Init () производят вычис-

ление и установку значений регистров соответствующей периферии. Кроме того, перед проведением описанных действий необходимо разрешить тактирование соответствующей периферии микроконтроллера.

52

Рассмотрим прием данных при помощи интерфейса UART. Как уже было сказано, в данной работе не используется система прерываний UART. Когда интерфейс принимает очередной байт данных, то при помощи ПДП данный байт попадает в промежуточный циклический буфер небольшой длины (порядка 16 байт). Данный буфер необходим для выравнивания скоростей приема и обработки данных, чтобы данные могли следовать непрерывно. Длина буфера выбирается экспериментальным путем с учетом максимальной скорости приема. Буфер не должен успевать переполняться. В бесконечном цикле задачи ОСРВ для обработки принятых данных происходит проверка наличия данных в буфере. Если данные есть, то они извлекаются и анализируются.

В роботизированном устройстве весь обмен данными по интерфейсу UART происходит в пакетном режиме. Это сделано для возможности контролирования целостности данных и наличия ошибок. Каждый пакет начинается с префикса и кода завершения пакета. Код завершения обычно представляет собой последовательность байт 0x0D0A в шестнадцатеричном виде.

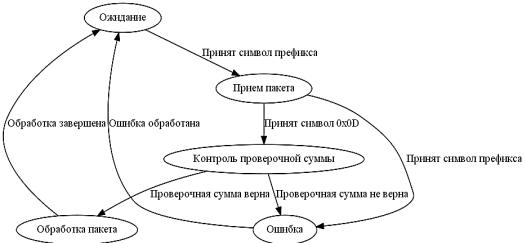

Для хранения пакета используется отдельный буфер (не циклический) уже большего размера (порядка 512 байт, в зависимости от максимальной длины пакета). Для приема пакета используется конечный автомат, который может находиться в строго определенных состояниях. Опишем состояния более подробно.

Состояние ожидания (psIdle). В данном случае каждый извлеченный из промежуточного буфера байт отбрасывается до тех пор, пока его значение не будет равно префиксу начала пакета. В последнем случае конечный автомат переходит в состояние приема пакета.

Состояние приема пакета (psPacket). В данном состоянии каждый извлеченный байт из промежуточного буфера заносится в буфер пакета. Если значение извлеченного байта равно первому байту признака конца пакета (0x0D), то конечный автомат переходит в следующее состояние.

Состояние окончания пакета (psCR). Служит для проверки целостности пакета. При каждом извлечении байта из промежуточного буфера происходит вычисление проверочной суммы пакета. Байт, предшествующий окончанию пакета содержит проверочную сумму, вычисленную на передающей стороне. Если проверочная сумма на передающей стороне и вычисленное значение не совпадают, то пакет считается поврежденным и отбрасывается. Если же проверочные суммы совпадают и следующий принятый байт равен второму байту признака окончания пакета (0x0A), то происходит обработка пакета.

Состояния конечного автомата и переходы между ними изображены на рис. 3.3.

Для передачи пакет сперва формируется в отдельном буфере заранее определенной длины. При этом перед вызовом функции передачи пакет уже нельзя будет редактировать, то есть он должен быть заполнен полностью.

При вызове функции UartSend () происходит настройка ПДП для передачи содержимого буфера. В параметрах функции передается, собственно, указа-

53

тель на буфер данных, а также размер данных в батах. После этого передача идет в автоматическом режиме без участия ядра микроконтроллера. После завершения передачи ПДП переходит в состояние ожидания.

Рис. 3.3. Состояния конечного автомата приема пакета UART [17]

Для передачи пакет сперва формируется в отдельном буфере заранее определенной длины. При этом перед вызовом функции передачи пакет уже нельзя будет редактировать, то есть он должен быть заполнен полностью.

При вызове функции UartSend () происходит настройка ПДП для передачи содержимого буфера. В параметрах функции передается, собственно, указатель на буфер данных, а также размер данных в батах. После этого передача идет в автоматическом режиме без участия ядра микроконтроллера. После завершения передачи ПДП переходит в состояние ожидания.

Так как во время передачи данных интерфейс UART микроконтроллера может быть использован одновременно несколькими задачами ОСРВ, то с момента настройки ПДП и до момента заве ршения передачи выполнение задачи, инициировавшей передачу, приостанавливается, а доступ к интерфейсу UART блокируется мьютексом. При этом другие задачи при обращении к заблокированному интерфейсу переходят в режим ожидания и находятся в нем до тех пор, пока интерфейс не разблокируется.

Таким образом, рассмотрен процесс программной реализации обмена данными между микроконтроллером и внешними устройствами при помощи последовательного интерфейса UART. Описан процесс инициализации интерфейса, процессы приема и передачи данных. Рассмотрено решение проблемы обеспечения одновременного взаимодействия с интерфейсом нескольких задач ОСРВ.

54