- •ВВЕДЕНИЕ

- •1. ОБЗОР НАУЧНО-ТЕХНИЧЕСКОЙ ЛИТЕРАТУРЫ

- •2.1. Комплектующие

- •2.1.1. Микроконтроллер

- •2.1.2. Шасси и электропривод

- •2.1.3. Радиомодуль

- •2.1.4. Датчик температуры и влажности воздуха

- •2.1.5. Инерциальный датчик

- •2.1.6. Модуль вычисления глобального местоположения

- •2.1.7. Ультразвуковой дальномер

- •2.1.8. Модуль измерения радиоактивного фона

- •2.2. Взаимодействие комплектующих

- •2.3. Сопряжение уровней логических сигналов

- •2.4. Интерфейс прямого доступа к памяти

- •2.5. Последовательный интерфейс UART микроконтроллера

- •2.6. Последовательный интерфейс i2c микроконтроллера

- •3.1. Многозадачность

- •3.2. Комбинированная многозадачность средствами ОСРВ

- •3.3. Управление тактовой частотой микроконтроллера

- •3.4. Работа с последовательным интерфейсом UART

- •3.5. Работа с последовательным интерфейсом I2C

- •3.6. Управление по радиоканалу

- •3.7. Вывод телеметрии

- •3.8. Передвижение роботизированного устройства

- •3.9. Измерение температуры и влажности воздуха

- •3.10. Вычисление ориентации в пространстве

- •3.10.1. Получение измерений инерциального датчика

- •3.10.2. Калибровка датчика

- •3.10.3. Преобразование данных инерциального датчика

- •3.11. Вычисление глобального местоположения

- •3.12. Следование по маршруту

- •3.12.1. Вычисление направления на точку маршрута

- •3.12.2. Удержание направления на точку маршрута

- •3.13. Программа дистанционного управления

- •3.13.1. Описание программы

- •ЗАКЛЮЧЕНИЕ

- •БИБЛИОГРАФИЧЕСКИЙ СПИСОК

- •ПРИЛОЖЕНИЕ 1

- •Принципиальная электрическая схема отладочной платы

- •ПРИЛОЖЕНИЕ 2

- •Принципиальная электрическая схема драйвера электродвигателей

- •ПРИЛОЖЕНИЕ 3

- •Принципиальная электрическая схема радиомодуля

- •ПРИЛОЖЕНИЕ 4

- •ПРИЛОЖЕНИЕ 5

- •Принципиальная электрическая схема инерциального датчика

- •ПРИЛОЖЕНИЕ 6

- •Принципиальная электрическая схема датчика глобального местоположения

- •ПРИЛОЖЕНИЕ 7

- •Принципиальная электрическая схема ультразвукового дальномера

- •ПРИЛОЖЕНИЕ 8

- •Принципиальная электрическая схема измерителя радиации

- •ПРИЛОЖЕНИЕ 9

- •Принципиальная электрическая схема платы сопряжения

- •ПРИЛОЖЕНИЕ 10

- •Принципиальная электрическая схема Arduino DUE

- •Схема распиновки Arduino DUE

- •Редактор Е. А. Кусаинова

- •Подписано в печать 26.10.2020.

- •ФГБОУ ВО «Воронежский государственный технический университет»

- •394026 Воронеж, Московский просп., 14

для защиты от выбросов повышенного напряжения при использовании транзистора с соответствующими параметрами.

Таким образом, решена проблема согласования логических уровней линий передачи данных между микроконтроллером и внешними устройствами.

2.4. Интерфейс прямого доступа к памяти

Прямой доступ к памяти (ПДП) используется для обеспечения высокоскоростной передачи данных между периферией и памятью, а также между памятью и памятью. Данные могут быть быстро перемещены при помощи ПДП без каких либо действий со стороны микроконтроллера. Это позволяет освободить ресурсы микроконтроллера для других операций. Контроллер ПДП сочетает в себе две шины передачи данных с независимой очередью (FIFO) для оптимизации пропускной способности системы. Два контроллера ПДП имеют в общей сложности 16 потоков (по 8 для каждого контроллера), каждый из которых связан запросами управления на доступ к памяти от одного или нескольких периферийных устройств. Каждый поток может иметь до 8 каналов (запросов) и у каждого есть арбитр для обработки приоритета. Следует обратить внимание, что одновременно несколько каналов одного потока работать не могут.

В случае возникновения определенного события в периферийном устройстве, последний может отправить сигнал в контроллер ПДП. В результате происходит запуск процесса обмена данными, состоящего из трех шагов:

•загрузка данных из регистра периферийного устройства (в случае, если направление передачи периферия-память) или загрузка данных из памяти (при направлении передачи память-память);

•сохранение загруженных данных в память (направление периферияпамять) или в периферийное устройство (направление память-периферия);

•уменьшение значения регистра счетчика данных ПДП на единицу (при значении, равном нулю, передача завершается).

Подробно об использовании ПДП в процессе обмена данными написано в последующих разделах.

Таким образом, описана технология ПДП, позволяющая производить доступ к памяти периферийным устройствам микроконтроллера без участия самого ядра. Благодаря этому происходит экономия вычислительных ресурсов а также повышается скорость передачи данных.

2.5. Последовательный интерфейс UART микроконтроллера

UART представляет собой последовательный асинхронный полнодуплексный интерфейс передачи данных. В микроконтроллере STM32F407ZGT6 имеется возможность использования синхронной версии данного интерфейса – USART. При помощи интерфейса возможна передача данных в широком диапазоне скоростей, фактически ограниченном лишь тактовой частотой системной

38

шины процессора. Всего в микроконтроллере предусмотрено шесть таких интерфейсов.

Для каждого интерфейса UART имеется собственный вектор прерываний с настраиваемым приоритетом, что позволяет добиться максимального быстродействия при передаче данных. Среди особенностей реализации интерфейса можно выделить следующие:

•Программно-настраиваемый дробный делитель тактовой частоты для формирования нужной скорости передачи данных;

•возможность использования бита контроля четности для обнаружения ошибок при передаче;

•настраиваемое количество стоп-битов;

•буферизация переданных и принятых байтов в специализированной области памяти;

•возможность использования технологии прямого доступа к памяти (ПДП) для передачи данных без участия ядра микроконтроллера;

•независимое использование приемника и передатчика.

Во время работы интерфейс формирует следующие события, связанные с состоянием передачи данных:

•буфер приемника полон;

•буфер передатчика пуст;

•окончание передачи;

•передача бита четности;

•успешная проверка четности;

•ошибка переполнения;

•обнаружение шума;

•ошибка кадра;

•ошибка четности.

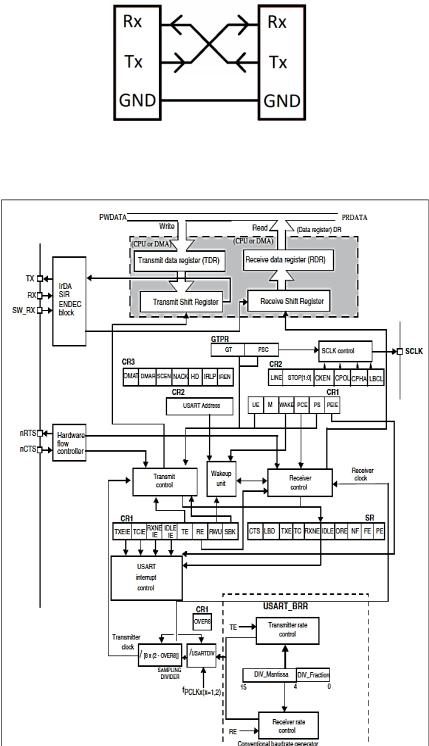

Сданными событиями связаны прерывания, приведенные в табл. 2.11. Для взаимодействия двух устройств при помощи интерфейса UART необходимо соединить их перекрестно, как показано на рис. 2.22. Приемник одного устройства соединяется с передатчиком другого и наоборот. Также необходимо соединить общие выводы обоих устройств.

|

|

Таблица 2.11 |

|

|

Прерывания интерфейса UART |

||

|

|

|

|

Прерывание |

|

Описание |

|

CTS |

|

обнаружение обрыва линии |

|

TXE |

|

регистр передачи данных пуст |

|

TC |

|

передача завершена |

|

RXNE |

|

регистр приема данных полон |

|

39

|

Окончание табл. 2.11 |

|

|

|

|

IDLE |

ожидание линии |

|

ORE |

ошибка переполнения |

|

NF |

ошибка шума |

|

PE |

ошибка четности |

|

Рис. 2.22. Подключение устройств для взаимодействия по интерфейсу

UART [4]

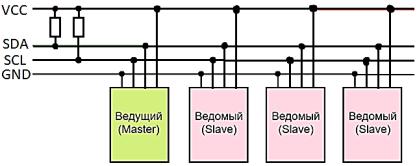

Рис. 2.23. Структурная схема интерфейса UART микроконтроллера [4]

40

При этом перед началом очередной передачи формируется старт-бит, а после завершения стоп-бит.

Подробно процесс передачи одного байта данных изображен на рис. 2.24. В случае приема байта данных сигнал из линии связи побитно заносится в сдвиговый регистр приемника, после чего байт данных также попадает в регистр DR. Таким образом, можно осуществлять одновременную передачу и прием данных.

Рис. 2.24. Диаграмма передачи одного байта при помощи интерфейса

UART [4]

После передачи либо приема байта данных формируется соответствующее прерывание (буфер передатчика пуст, либо буфер приемника полон). Данные прерывания возникают не после завершения передачи, а после того как, в случае передачи, данные будут перемещены из регистра DR в сдвиговый регистр. В случае приема - в обратном направлении. Таким образом, обеспечивается возможность непрерывного обмена.

Таким образом, рассмотрены внутреннее устройство последовательного интерфейса передачи данных UART, а также принципы его работы. Описана последовательность действий для приема и передачи байта данных. Программное управление и конфигурирование интерфейса описаны в последующих разделах.

2.6. Последовательный интерфейс i2c микроконтроллера

Интерфейс передачи данных I2С также является последовательным. Для передачи данных он использует две двунаправленные линии – SDA и SCL. Используется в основном для обмена данными между низкоскоростными компонентами внутри электронных устройств.

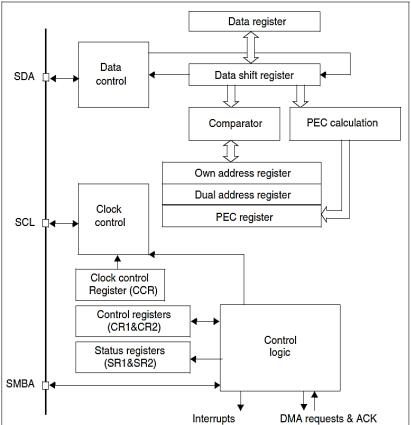

Линии SDA и SCL подключаются через резисторы, подтягивающие линии к питанию, по схеме с открытым стоком. SDA используется непосредственно для передачи данных, а SCL – для тактирования. Интерфейс имеет возможность подключения до 127 устройств на линии при использовании 7-

41

битной адресации. Также существуют версии интерфейса с 10-бит адресацией. Стандартная скорость передачи данных – 100 кбит/с, однако некоторые реализации поддерживают 400 кбит/с и 1 Мбит/с. Также стандарт предоставляет возможность использования приостановки передачи для того, чтобы более медленные устройства успевали работать с шиной. Подключение нескольких устройств для совместной работы по шине проиллюстрировано на рис. 2.25.

Рис. 2.25. Подключение устройств для обмена по интерфейсу I2C [5]

К шине могут быть подключены два типа устройств: мастер либо подчиненный. Мастер осуществляет генерирование тактового сигнала и, собственно, управляет передачей. Подчиненный может только отвечать на запросы мастера. Идентификация конкретного подчиненного осуществляется путем указания его адреса.

Микроконтроллер STM32ZGT6 имеет в своем составе три интерфейса I2C, способных работать на скорости вплоть до 400 кбит/с. Структурная схема реализации интерфейса в микроконтроллере приведена на рис. 2.26.

Обмен данными может осуществлять как в режиме мастер, так и в режиме подчиненный. В случае использования интерфейса в разработанном устройстве обмен всегда проходит в режиме мастер. Управление интерфейсом осуществляется путем записи определенных значений в регистры. Основными регистрами являются: CR1 – регистр управления 1; CR2 – регистр управления 2; DR

– регистр данных; SR1 – регистр состояния 1; SR2 – регистр состояния 2. Регистры управления используются, соответственно, для конфигурирования шины, а регистры состояния – для отслеживания режимов работы и ошибок.

Для каждого интерфейса в микроконтроллере имеется свой набор независимых прерываний с настраиваемым приоритетом. Список прерываний приведен в табл. 2.12.

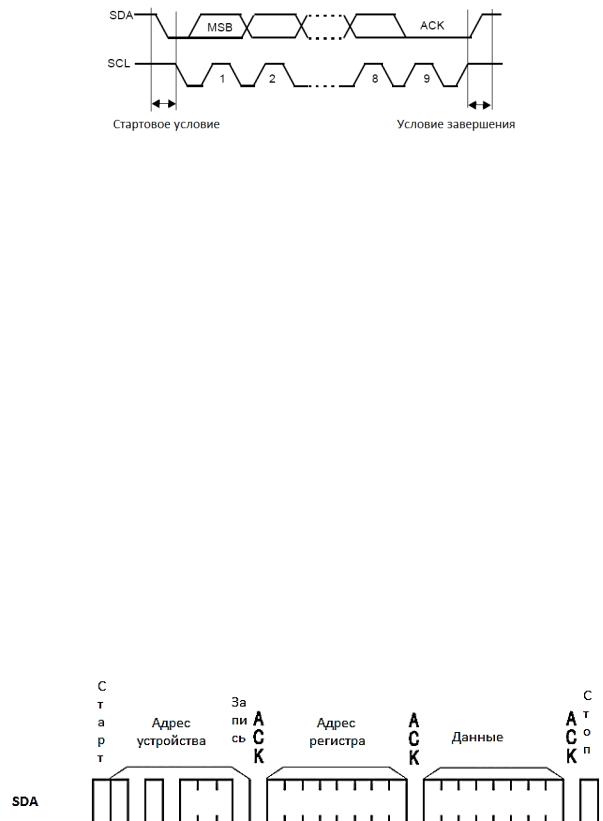

Общее представление о процессе обмена данными по шине I2C можно получить из рис. 2.27. При возникновении стартового условия все устройства на шине начинают принимать данные. В случае, если на шине возникло условие завершения, обменивающиеся устройства прекращают информационный обмен.

Мастер может осуществлять либо запись данных в подчиненное устройство, либо считывание. На рис. 2.28 показана последовательность действий для

42

записи данных. Буквой «S» обозначено состояние шины при начале обмена данными – сигнал «Старт».

Рис. 2.26. Структурная схема интерфейса I2C микроконтроллера [5]

|

Таблица 2.12 |

|

|

Прерывания интерфейса I2C |

|

|

|

|

Прерывание |

Описание |

|

SB |

Формирование на шине сигнала «Старт» в режиме мастер |

|

ADDR |

Отправка адреса устройства в режиме мастер либо при- |

|

|

ем адреса в режиме подчиненного |

|

ADDR10 |

10-бит адрес отправлен (режим мастер) |

|

STOPF |

Формирование на шине сигнала «Стоп» |

|

BTF |

Передача байта завершена |

|

RxNE |

Буфер приема не пуст |

|

TxE |

Буфер передачи пуст |

|

BERR |

Ошибка шины |

|

ARRLO |

Потеря арбитража в режиме мастер |

|

AF |

Ошибка подтверждения приема |

|

OVR |

Переполнение |

|

TIMEOUT |

Превышено время передачи одного бита |

|

43

Рис. 2.27. Общий вид обмена данными по шине I2C [5]

Данное состояние генерирует мастер путем переключения линии SDA из состояния логической «1» в состояние логического «0», при этом на линии SCL уровень сигнала высокий. Данное состояние уведомляет подчиненные устройства о начале передачи данных.

После сигнала «Старт» происходит передача адреса устройства. Если к шине подключено устройство с переданным адресом, то оно должно уведомить мастера подтверждением приема (ACK). Кроме того, каждый байт переданных данных также должен подтверждаться. Это происходит следующим образом. После передачи одного байта мастер «отпускает» линию данных (на линии устанавливается уровень, соответствующий напряжению питания). Подчиненное устройство на время одного периода сигнала синхронизации подтягивает линию данных к «земле». Таким образом, мастер информируется об успешном приеме байта подчиненным. После передачи адреса следуют байты данных, и описанная процедура повторяется.

После передачи всех байтов данных мастер генерирует на шине сигнал «Стоп». На рис. 2.28 данный сигнал отмечен буквой «P». Осуществляется это путем переключения линии SDA из низкого состояния в высокое при высоком уровне SCL. Таким образом, все устройства на шине информируются об окончании передачи. Во время с начала сигнала «Старт» и до окончания сигнала «Стоп» шина считается занятой и никакие другие устройства не могут осуществлять передачу данных.

Рис. 2.28. Диаграмма передачи данных в режиме записи по интерфейсу

I2C [5]

44