LR-5

.doc

МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра систем автоматизированного проектирования

отчет

по лабораторной работе №5

по дисциплине «Схемотехника»

Тема: Компаратор

Студенты гр. 8363 |

|

Павкина А. Соболевская А.А. Нерсисян А.С. |

Преподаватель |

|

Фахми Ш.С. |

Санкт-Петербург

2020

Техническое задание

Изучить принципы функционирования и проектирования цифровых компараторов (схем сравнения), научится программировать функциональные особенности схем в Active-HDL, проводить моделирование работы микросхем.

Теоретическая часть

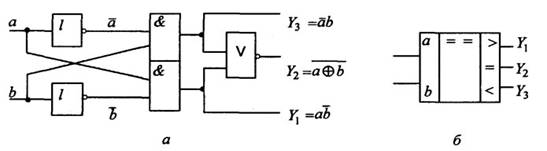

Описание схемы

Схемы компараторов предназначены для реализации логических условий, которые сравнивают два поступающих числа в микропрограммах, и выводит цифровой сигнал, указывающий на увеличение одно сигнала над другим.

Схема модуля

Структурная

Принципиальная

Таблица истинности

Практическая часть

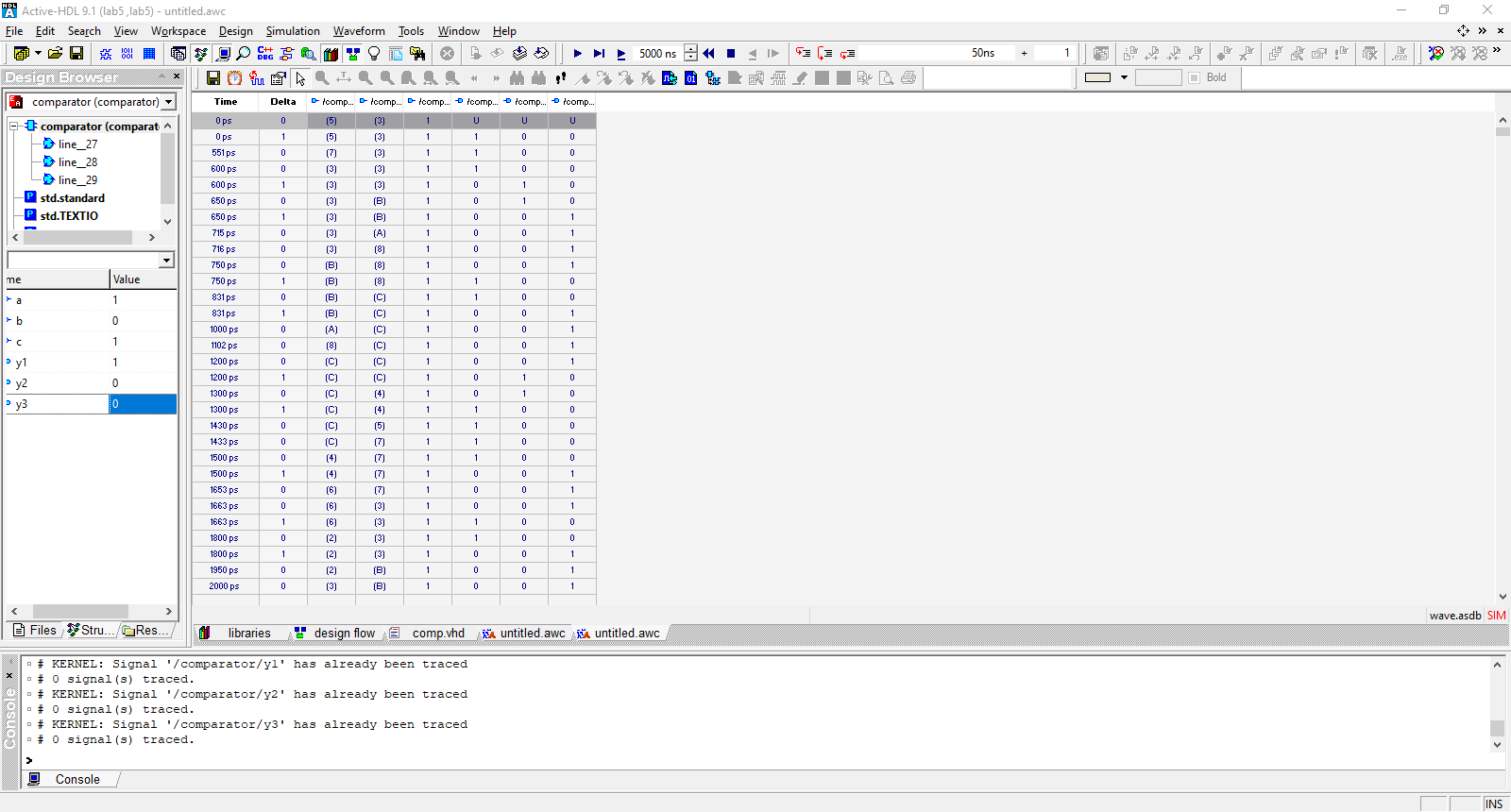

Разработка VHDL

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity comparator is

port(

a : in STD_LOGIC_VECTOR(3 downto 0);

b : in STD_LOGIC_VECTOR(3 downto 0);

c : in STD_LOGIC;

y1 : out STD_LOGIC;

y2 : out STD_LOGIC;

y3 : out STD_LOGIC

);

end comparator;

architecture comparator of comparator is

signal z3: STD_LOGIC;

signal z2: STD_LOGIC;

signal z1: STD_LOGIC;

signal z0: STD_LOGIC;

begin

z3 <= ((a(3) and b(3)) or (not(a(3)) and not(b(3))));

z2 <= ((a(2) and b(2)) or (not(a(2)) and not(b(2))));

z1 <= ((a(1) and b(1)) or (not(a(1)) and not(b(1))));

z0 <= ((a(0) and b(0)) or (not(a(0)) and not(b(0))));

y1 <= ((a(3) and not(b(3))) or ((a(2) and not(b(2))) and z3) or ((a(1) and not(b(1))) and z3 and z2) or ((a(0) and not(b(0))) and z3 and z2 and z1)) and c;

y2 <= (z3 and z2 and z1 and z0) and c;

y3 <= ((b(3) and not(a(3))) or ((b(2) and not(a(2))) and z3) or ((b(1) and not(a(1))) and z3 and z2) or ((b(0) and not(a(0))) and z3 and z2 and z1)) and c;

end comparator;

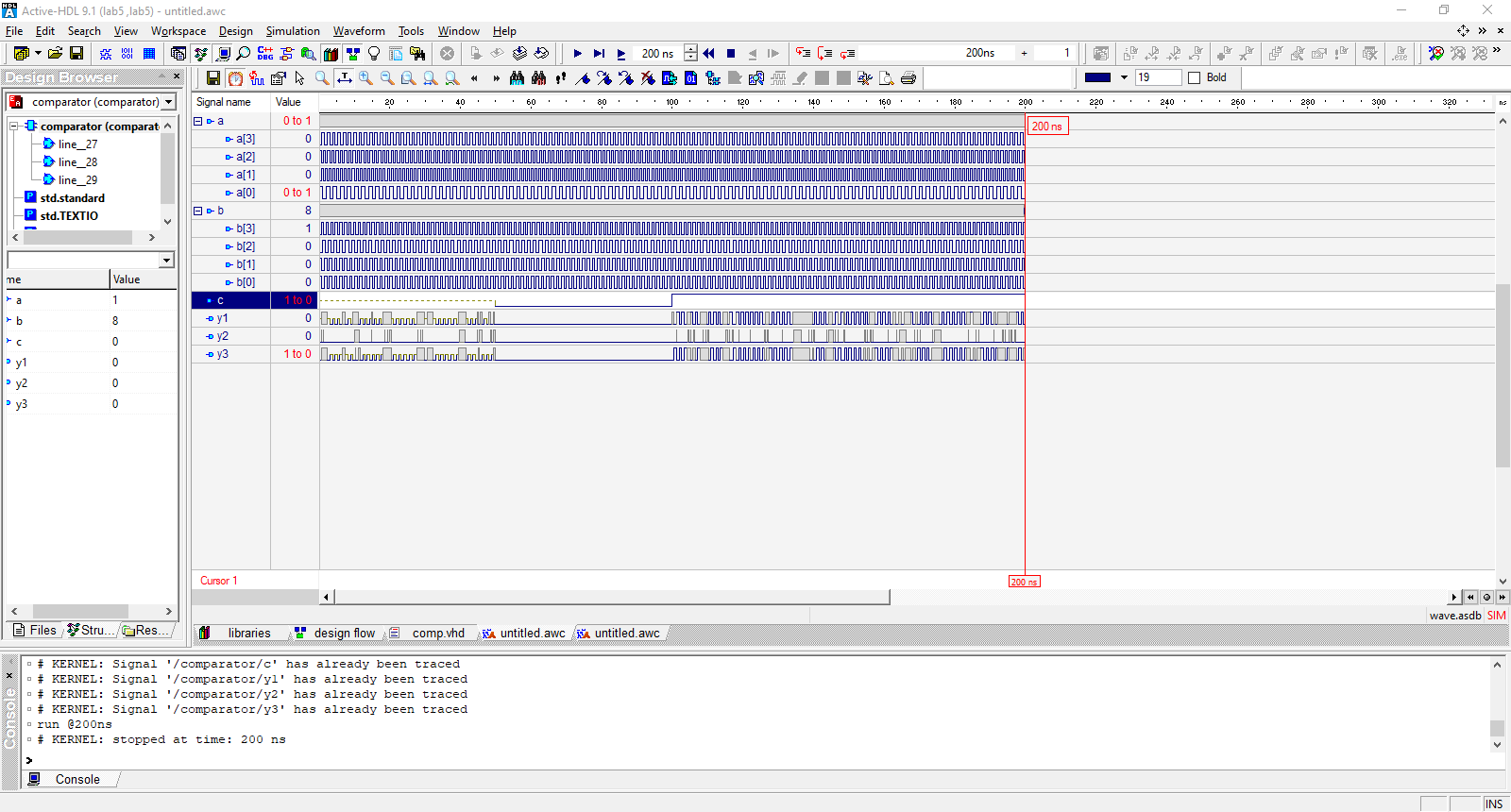

Разработка временных диаграмм

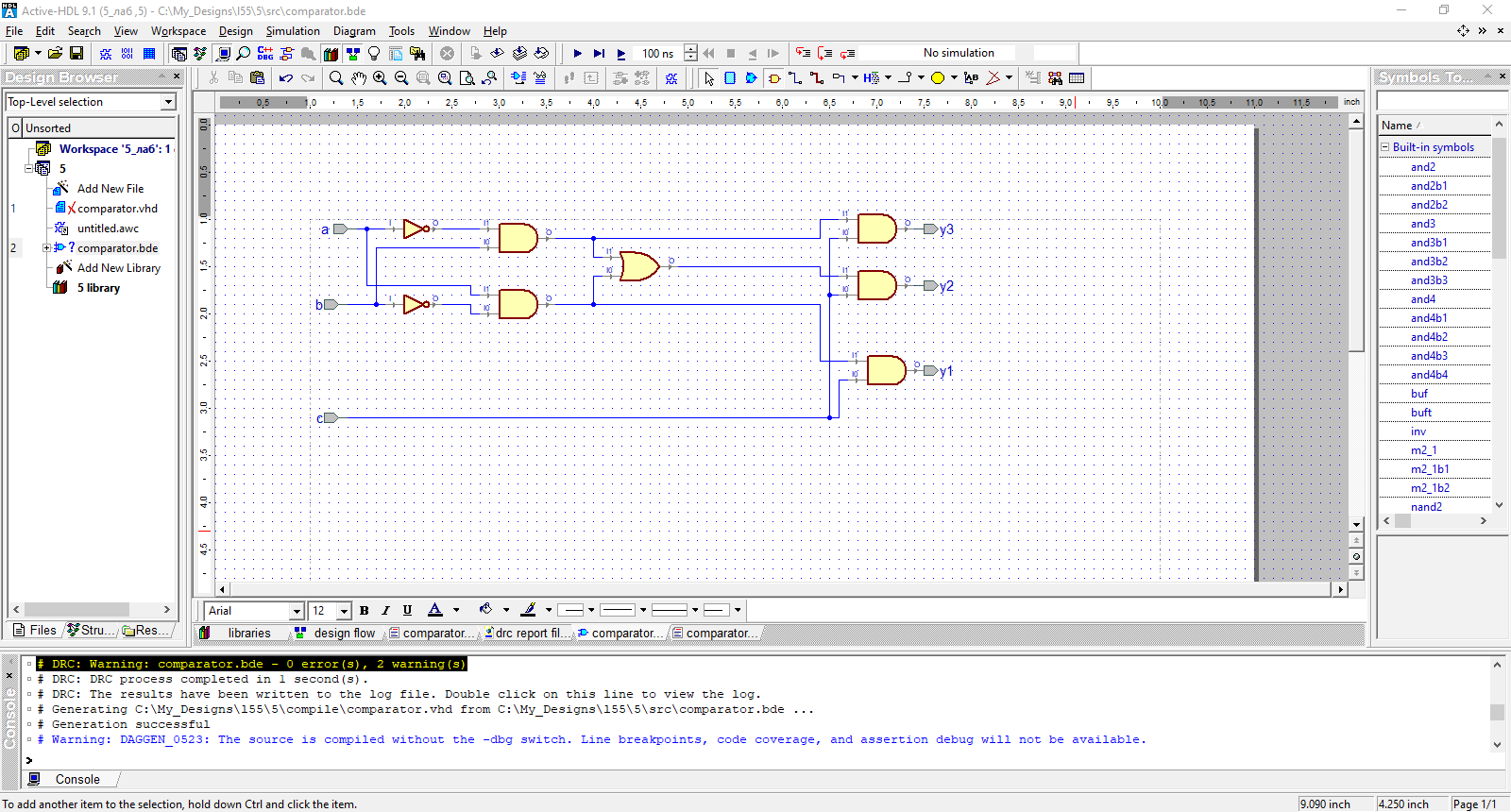

Разработка схемы подключений

.

Вывод.

Изучили функционирования и проектирования цифровых компараторов (схем сравнения), научились программировать функциональные особенности схем в Active-HDL, проводить моделирование работы микросхем.

Литература

1. Фахми Ш. С., Соколов Ю. М. М.: Издательство СПбГЭТУ «ЛЭТИ» 2019.

.