LR-4

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра САПР

отчет

По лабораторной работе № 4

по дисциплине «Схемотехника»

Тема: Накапливающий сумматор

Студенты гр. 8363 |

|

Павкина А. Соболевская А.А. Нерсисян А.С. |

Преподаватель |

|

Фахми С.Ш. |

Санкт-Петербург

2020

ТЕХНИЧЕСКОЕ ЗАДАНИЕ на ЛАБОРАТОРНУю работу

Тема работы : Накапливающий сумматор

|

Исходные данные: Проектировать схему накапливающего сумматора в среде САПР-Active HDL (Aldec), разработать VHDL код схемы. |

Содержание пояснительной записки: Теоритическая часть, описание схемы, схема требуемого модуля, структурная схема, функциональная схема, таблица истинности, практическая часть, разработка VHDL кода схемы, описание процесса проектирования схемы в среде САПР-Active HDL (Aldec), разработка временных диаграмм схем (ти в виде графика), разработка схемы подключения, выводу по работе, список использыванных источников. |

2. Теоритическая часть

Описание схемы

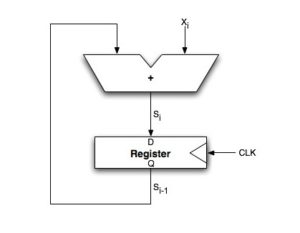

Накапливающие сумматоры в основном строиться по структуре комбинационный сумматор плюс регистр хранения. Можно реализовать две схемы: с запоминанием результата операции S = А плюс В; с накоплением результата S = S плюс А.

Функциональная

схема накапливающего сумматора приведена

на рисунке ниже. Она включает один

четырехразрядный комбинационный

сумматора D1 и два регистра D2, D3.

Комбинационные сумматоры, выполняют

операцию суммирования двух четырехразрядных

двоичных чисел A и B с учетом

переноса из предыдущего разряда P0 и

формируют перенос P4 в

последующий разряд. Запоминающие

регистры, представляют собой набор

четырех и шести триггеров с общим входом

сброса  и синхронизации С. Установка триггеров

в нулевое состояние производится низким

уровнем сигнала на входе R. При этом

выполняется микрооперация очистки

регистров:

и синхронизации С. Установка триггеров

в нулевое состояние производится низким

уровнем сигнала на входе R. При этом

выполняется микрооперация очистки

регистров:

Y1: RG1(4) := 0;

Y2: RG2(4) := 0.

Синхровходы С служат для записи информации, установленной на входах Dl, D2, D3, D4 регистров, т.е. выполняют микрооперации

Y3: RG1(4) := S1;

Y4: RG2(4) := RG1(4).

На первом этапе производится очистка регистров, и на вход первого сумматора устанавливается первое слагаемое A0. Сумматор выполняет функцию сложения:

D1: S1 = RG2(4) + А(4),

где А(4) – слагаемое А, поступившее на вход сумматора,

RG2(4) – слагаемое B, поступившее на вход сумматора с выхода второго регистра.

Поскольку регистры перед началом суммирования были обнулены, слагаемое B равно нулю и, следовательно, первая сумма будет равна

D1: S1 = 0 + А(4) = А(4).

Схема требуемого модуля

а) структурная схема

б) функциональная схема

Функциональная схема четырехразрядного накапливающего сумматора

3. Практическая часть

3.1. Разработка VHDL кода схемы

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity accumulator is

port(clk, reset : in std_logic;

Din : in std_logic_vector(3 downto 0);

Q : out std_logic_vector(3 downto 0));

end accumulator;

architecture bhv of accumulator is

signal tmp: std_logic_vector(3 downto 0);

begin

process (clk, reset)

begin

if (reset='1') then

tmp <= "0000";

elsif rising_edge(clk) then

tmp <= tmp + Din;

end if;

end process;

Q <= tmp;

end bhv;

Используемая литература

Математическое и программное обеспечение устройств с программируемой логикой. 2019 г. Фахми, Соколов

https://www.kit-e.ru/articles/circuit/2009_03_134.php - лекции по схемотехнике

https://go-radio.ru/registr.html - теоретические сведения про сдвигающие регистры