LR-2

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра электронных приборов и устройств

отчет

по лабораторной работе №2

по дисциплине «Схемотехника»

Тема: Умножитель двоичных чисел

Студенты гр. 8363 |

|

Павкина А. Соболевская А.А. Нерсисян А.С. |

Преподаватель |

|

Фахми Ш.С. |

Санкт-Петербург

2020 г.

Цель работы.

Разработать на языке описания схем Verilog шестнадцатиразрядный умножитель двоичных чисел.

Основные теоретические положения.

Процедура умножения двоичных кодов чисел достаточно часто встречается при цифровой обработке сигналов. Если рассматривать целые числа, то умножение можно представить как многократное сложение. К примеру, чтобы умножить 3 на 5, требуется тройку пять раз сложить с самой собой. Данным способом умножение можно выполнять, используя, в частности, накапливающие сумматоры. Однако время выполнения этой процедуры будет достаточно велико и, кроме того, оно окажется зависимым от величины множителя.

Другие подходы к реализации процедуры перемножения чисел требуют многократного последовательного выполнения операций сложения и сдвига. Их количество, а следовательно, скорость выполнения умножения, также зависят от разрядности множителя.

Разработка специальных алгоритмов умножения позволила создать так называемые параллельные или матричные умножители. Одна из их разновидностей называется множительным, а другая - множительно-суммирующим блоком. Последние обеспечивают возможность наращивания разрядности обрабатываемых операндов.

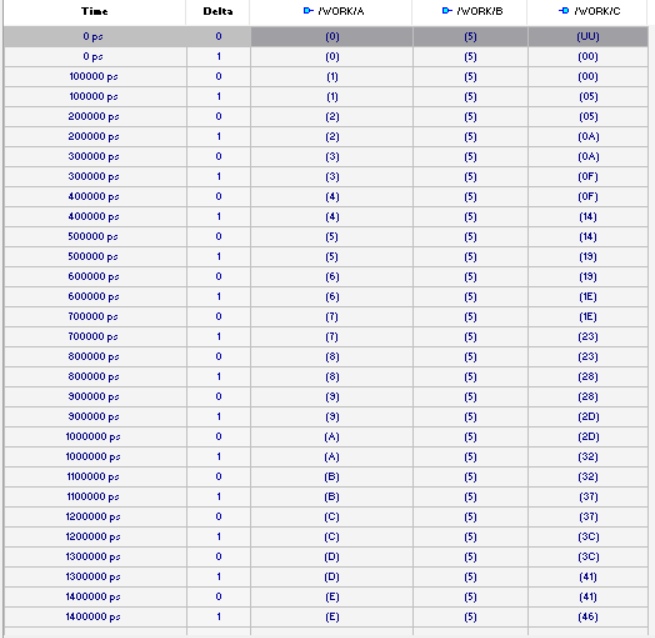

Таблица истинности

Разработка Verilog кода схемы

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

entity WORK is

port(

A : in STD_LOGIC_VECTOR(3 downto 0);

B : in STD_LOGIC_VECTOR(3 downto 0);

C : out STD_LOGIC_VECTOR(7 downto 0)

);

end WORK;

architecture WORK of WORK is

begin

process(A,B)

variable pv,bp: STD_LOGIC_VECTOR(7 downto 0);

begin

pv := "00000000";

bp := "0000" & B;

for i in 0 to 3 loop

if A(i) = '1' then

pv := pv + bp;

end if;

bp := bp(6 downto 0) & '0';

end loop;

C <= pv;

end process;

end WORK;

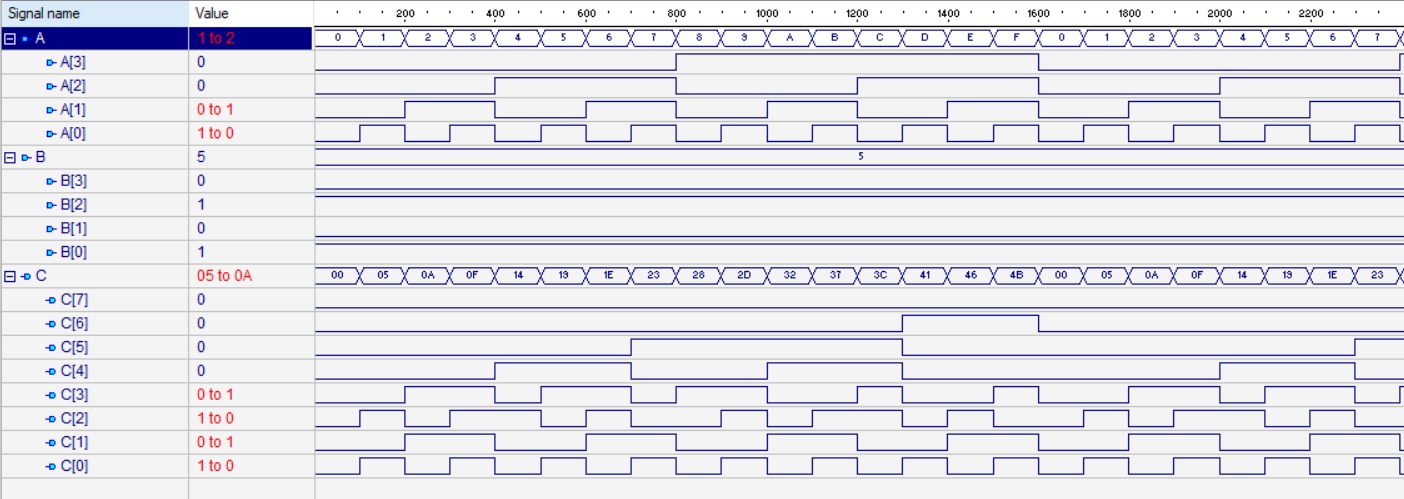

В ременная

диаграмма

ременная

диаграмма

Примеры использования

Промышленностью выпускаются в интегральном исполнении функционально законченные блоки для быстрого умножения двух восьмиразрядных чисел - микросхема К1802ВР3, двенадцатиразрядных – К1802ВР4 и шестнадцатиразрядных – К1802ВР5. Время выполнения операции умножения у них составляет порядка 100÷120 нС. В настоящее время аналогичные устройства встраиваются в сопроцессоры и ряд микроконтроллеров.

Выводы

В результате выполнения лабораторной работы был получен код, описывающий умножитель двоичных чисел на языке Verilog. Также была построена временная диаграмма, таблица истинности функциональная и принципиальны.

Используемая литература

Математическое и программное обеспечение устройств с программируемой логикой. 2019 г. Фахми, Соколов

https://www.kit-e.ru/articles/circuit/2009_03_134.php - лекции по схемотехнике