- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

Метод вычитания

На первом шаге определяется старший разряд двоичного числа n для переводимого десятичного числа N0 из условия

2 n+1 > N0 2 n

и в этот разряд вписывается единица. Затем из исходного числа N0 вычитается 2n и находится первая разность:

N1 = N0 – 2n.

Для этой разности находится следующая максимальная степень числа 2 (в порядке убывания), и производится вычитание, а в соответствующий разряд вписывается единица. Эта процедура продолжается до тех пор, пока десятичное число не станет равным нулю. Разряды, в которых отсутствуют единицы, заполняются нулями.

Пример 2.2.7 Перевести десятичное число 83 в двоичный код.

В итоге имеем 8310 = 10100112.

Перевод дробного десятичного числа выполняется аналогично. Процедура продолжается до получения заданной степени точности.

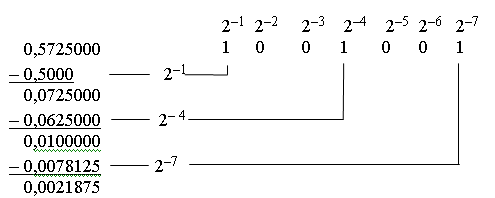

Пример 2.2.8 Перевести дробное десятичное число 0,5725 в двоичный код методом вычитания (с точностью до семи разрядов).

Подобным образом переводятся десятичные числа в восьмеричный и шестнадцатеричный коды.

Перевод чисел из восьмеричной, шестнадцатеричной системы счисления и обратно. Для перевода числа из восьмеричной системы счисления в двоичную каждую цифру этого числа необходимо записать трехразрядным двоичным числом (триадой). При этом восьмерично-двоичный код совпадает с двоичным.

Пример 2.2.9

(235,275)8 = 010 011 101, 010 111 1018– 2 =10011101, 0101111012

28 38 58, 28 78 58.

Для перевода числа из двоичной системы счисления в восьмеричную необходимо разбить это число вправо и влево от запятой на триады и записать каждую группу цифрой в восьмеричной системе. Крайние неполные триады дополняются нулями.

Пример 2.2.10

10101,01112 = 010 101, 011 1008–2 = 25,348

28 58, 38 48.

Для перевода числа из шестнадцатеричной системы счисления в двоичную необходимо каждую цифру этого числа записать тетрадой, при этом шестнадцатерично-двоичный код совпадает с двоичным, поскольку 16 = 24 .

Пример 2.2.11

9D,5E16 = 1001 1101, 0101 111016–2 = 10011101,01011112

910 1310 , 510 1410.

Для перевода числа из двоичной системы счисления в шестнадцатеричную необходимо разбить это число вправо и влево от запятой на тетрады и каждую тетраду представить шестнадцатеричной цифрой.

Пример 2.2.12

111100,101012 = 0111 1100, 1010 100016–2 = 7C,A816 ,

716 С16 , А16 816.

Основными недостатками двоичной системы счисления являются большая длина разрядной сетки по сравнению с другими системами счисления, необходимость перевода исходных числовых данных из десятичной системы счисления в двоичную, а результатов решения − из двоичной в десятичную.

Двоично-десятичная система счисления имеет основание d = 10, и каждая цифра (0, 1, 2, 3, 4, 5, 6, 7, 8, 9) изображается в этой системе счисления четырехразрядным двоичным числом, называемым тетрадой. Она используется в ЭВМ не только в качестве вспомогательной системы счисления при вводе и выводе данных, но и в качестве основной при решении задач, когда в ЭВМ вводится и выводится большое количество чисел, а вычислений над ними производится мало. Десятичные числа в двоично-десятичной системе счисления кодируются в прямом нормально-взвешенном коде 8-4-2-1, т.е. каждую цифру десятичного числа необходимо заменить соответствующей тетрадой двоичных чисел.

Для перевода десятичного числа в двоично-десятичный код, десятичный символ следует заменить его двоичным изображением в виде тетрады.

Пример 2.2.13

91,3710 = 1001 0001, 0011 01112–10

910 110, 310 710

Для перевода двоично-десятичного числа в десятичное необходимо исходный код разбить на тетрады вправо и влево от запятой (неполные тетрады дополнить нулями) и заменить полученные тетрады соответствующими десятичными символами.

Пример 2.2.14

11001,001112–10 = 0001 1001, 0101 1000 = 19.5810

110 910 , 510 810

В таблице 2.2 приведены изображения десятичных чисел 0...20 в двоичном, восьмеричном и шестнадцатеричном кодах.

Таблица 2.2

Десятичное число |

Двоичный код |

Восьмеричный код |

Шестнадца- теричный код |

0 |

00000 |

0 |

0 |

1 |

00001 |

1 |

1 |

2 |

00010 |

2 |

2 |

3 |

00011 |

3 |

3 |

4 |

00100 |

4 |

4 |

5 |

00101 |

5 |

5 |

6 |

00110 |

6 |

6 |

7 |

00111 |

7 |

7 |

8 |

01000 |

10 |

8 |

9 |

01001 |

11 |

9 |

10 |

01010 |

12 |

A |

11 |

01011 |

13 |

B |

12 |

01100 |

14 |

C |

13 |

01101 |

15 |

D |

14 |

01110 |

16 |

E |

15 |

01111 |

17 |

F |

16 |

10000 |

20 |

10 |

17 |

10001 |

21 |

11 |

18 |

10010 |

22 |

12 |

19 |

10011 |

23 |

13 |

20 |

10100 |

24 |

14 |

Код 7421 отличается тем, что любая кодовая комбинация содержит не более двух единиц. В коде 2 из 5 все кодовые комбинации содержат только две единицы из пяти. Это свойство используется для выявления ошибок в кодовых комбинациях (любое отклонение от этого указывает на ошибку). При выполнении арифметических операций широко используются самодополняющиеся коды, инверсия двоичных цифр в которых дает дополнение до 9. Таким свойством обладают код 2-4-2-1, код с избытком 3, код с избытком 6. Например, в коде с избытком 6 цифре 0 соответствует кодовая комбинация 0110, ее инверсия 1001 соответствует цифре 9 (в коде 8-4-2-1), сумма этих чисел 0 и 9 дает 9 (1111) и т.д.(Таблица 2.3).

Таблица 2.3

Десятичная

|

Двоичное кодирование десятичной цифры |

|||||

код 8421 |

код 7421 |

Код 2421 |

код 2 из 5 |

код с избыт. 6 |

код с избыт. 3 |

|

0 |

0000 |

0000 |

0000 |

11000 |

0110 |

0011 |

1 |

0001 |

0001 |

0001 |

01100 |

0111 |

0100 |

2 |

0010 |

0010 |

0010 |

00110 |

1000 |

0101 |

3 |

0011 |

0011 |

0011 |

10011 |

1001 |

0110 |

4 |

0100 |

0100 |

0101 |

10100 |

1010 |

0111 |

5 |

0101 |

0101 |

1011 |

10101 |

1011 |

1000 |

6 |

0110 |

0110 |

1100 |

01010 |

1100 |

1001 |

7 |

0111 |

1000 |

1101 |

00101 |

1101 |

1010 |

8 |

1000 |

1001 |

1110 |

10010 |

1110 |

1011 |

9 |

1001 |

1010 |

1111 |

01001 |

1111 |

1100 |