- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

18 Программируемые делители

Цифровое устройство, называемое делителем, предназначено для деления числа входных импульсов или частоты их следования на заданный коэффициент. Строятся делители на основе счетчиков любых типов, хотя предпочтение отдается двоичным. Делители, как правило, не имеют промежуточных выходов, а лишь один основной. Коэффициент деления может иметь постоянное или переменное значение, например, задаваемое программой. Делители с переменным коэффициентом деления Кдел, называемые ДПКД, могут быть построены по различным схемотехническим вариантам, например, с предварительной установкой счетчика в некоторое исходное состояние от которого ведется счет до переполнения счетчика при суммировании, либо обнуление при вычитании, либо с установкой промежуточного значения коэффициента счета, после которого произойдет сброс счетчика в нулевое состояние и начнется новый цикл. Кроме того, возможно построение ДПКД на основе кольцевых счетчиков, у которых возможно изменение схемы обратных связей.

18.1 Программируемые делители с предварительной установкой

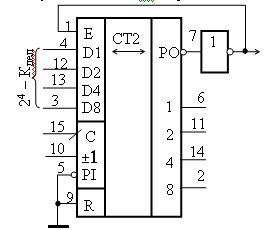

Пример программируемого делителя, построенного по варианту с предварительной установкой, приведен на рисунке 18.1. На входы предустановки ИС К564ИЕ11 подают код, соответствующий числу «лишних» состояний 2n – Kдел. Запись числа во все триггеры происходит параллельно через входы D с поступлением на вход «Разрешение установки» Е уровня лог. 1. Этот импульс приходит с инвертора, подключенного к выходу переноса РО. Тактовые импульсы поступают на вход С, переключение триггеров в счетчике происходит по положительному фронту. При подаче на вход 1 высокого уровня счетчик производит сложение последовательности импульсов (входного числа), подаваемых на тактовый вход С, с числом записанным в счетчике. Счетчик проходит состояния от исходного, предварительно установленного, до конечного, при котором он заполняется единицами и формирует на выходе РО сигнал переноса. Этим сигналом разрешается запись в счетчик исходного кода, и цикл повторяется. На выходе инвертора получим импульсную последовательность, частота которой будет равна Fвх /Kдел. При подаче на вход 1 низкого уровня напряжения счетчик производит вычитание из числа, записанного в счетчике Куст (код установки) последовательности импульсов, подаваемых на вход С. В этом случае сигнал переноса формируется при обнулении счетчика и, следовательно, коэффициент деления будет равен коду, установленному на входах D, а частота выходного сигнала будет равна Fвх /Kуст.

Установление всех разрядов счетчика в нулевое состояние можно осуществить путем подачи на вход R лог.1, причем вход R имеет абсолютный приоритет по отношению к любому другому входу. В счетчике предусмотрены вход и выход переноса (Р1 и Р2) , что позволяет увеличить разрядность обрабатываемых чисел путем последовательного соединения нескольких счетчиков с помощью входов Р1 и выходов Р2.

Рисунок 18.1 – Делитель на ИС К564ИЕ11 с предварительной установкой.

Принцип предустановки можно использовать при построении многоразрядных программируемых делителей (рисунок 18.2). Для этих целей удобно использовать МСХ К555ИЕ9 . Чтобы получить указанный режим, достаточно сигнал переноса старшего разряда, через инвертор, подать на V вход разрешения записи всех счетчиков, а на информационные входы D1–D8 подать двоичный код, определяющий коэффициент пересчета. При установке счетчика в процессе счета в состояние все «девятки» счетчик перейдет в режим параллельной записи и при подаче следующего тактового импульса вместо перехода в 00…0 произойдет запись параллельного кода, поданного на входы D1 – D4 каждой микросхемы. В результате общий коэффициент пересчета N уменьшится на величину K и составит

N = 10 m – K,

где m – число микросхем в делителе.

Коэффициент пересчета может меняться в делителе для выхода 2 в пределах 1…10m, так как длительность выходных импульсов положительной полярности равна длительности паузы между положительными импульсами входной последовательности. Для выхода 1 коэффициент пересчета меняется в пределах 20 m , поскольку длительность импульсов отрицательной полярности равна периоду входных импульсов.

Рисунок 18.2 – Делитель с управляемым коэффициентом деления с предустановкой на ИС К555ИЕ9

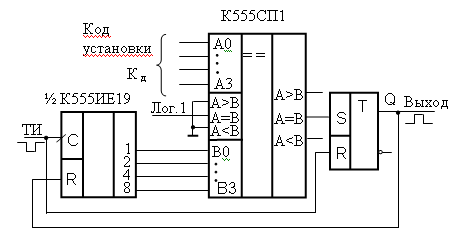

Программируемый делитель с цифровым компаратором. Вариант ДПКД с использованием цифрового компаратора приведен на рисунке 18.3.

Рисунок 18.3 – Программируемый делитель на счетчике и цифровом компараторе

На входы А0 – А3 цифрового компаратора подан код предустановки, соответствующий Кдел. При достижении счетчиком состояния, код которого равен установленному, компаратор на выходе А=В формирует сигнал выходного уровня и переводит SR-триггер в единичное состояние. По цепи обратной связи сигнал с выхода триггера поступает на вход R счетчика и обнуляет его. Следующий тактовый импульс по фронту выключает триггер, а по срезу начинает новый цикл счета. Дополнительный триггер необходим для исключения возможности сбоя при разбросе временных параметров счетчика (повышения надежности работы). Во многих случаях этот триггер можно исключить.