- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

17.6.2 Синхронные счетчики

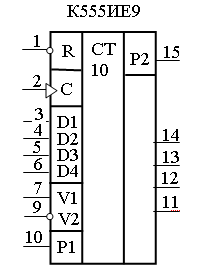

Микросхема К555ИЕ9 (рисунок 17.20) – синхронный десятичный счетчик на JK-триггерах с внутренней задержкой с возможностью параллельной записи информации по фронту тактового импульса, имеет восемь управляющих входов и вход асинхронного сброса. Для обеспечения режима счета на входе R необходимо подать лог.1, тот же сигнал должен быть подан на входы разрешения параллельной записи V2, разрешения счета V1, разрешения выдачи сигнала переноса P1. Изменение состояния триггеров счетчика при счете происходит по спаду импульсов отрицательной полярности, подаваемых на вход C.

Рисунок 17.20 – Условное обозначение ИС К555ИЕ9

При подаче лог. 0 на вход V2 микросхема переходит в режим параллельной записи информации со входов Dl – D8. Запись синхронная и происходит по фронту тактового импульса на входе С. При записи на входе R должен быть высокий уровень, сигналы на входах Vl и P1 – произвольные. На выходе переноса Р2 лог. 1 появляется в том случае, когда счетчик находится в состоянии 9, а на входе P1 присутствует лог.1, в остальных случаях на выходе Р2 лог. 0. Подача лог. 0 на вход P1 запрещает выдачу логической 1 на выходе Р2 и счет импульсов. Подача лог. 0 на вход V1 запрещает счет, но не запрещает выдачу сигнала переноса. Сигнал запрета счета (лог. 0 на входах V1 или P1) действует лишь в том случае, если он полностью перекрывает по длительности импульс отрицательной полярности на входе С, в том числе он может совпадать с ним по времени. Для обеспечения параллельной записи информация на входы Dl–D8 может быть подана как при лог. 1, так и при лог.0 на входе С и удерживаться до момента появления перепада 0/1, тогда и произойдет запись.

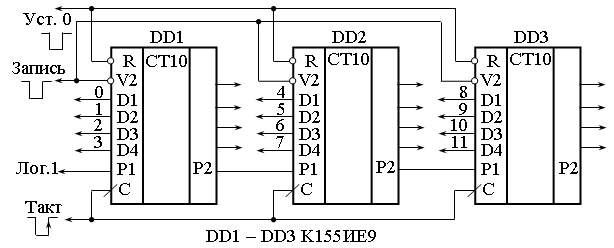

Для счета с числа, введенного в микросхему при параллельной записи, низкий уровень на входе V2 должен быть изменен на лог. 1 или одновременно с переходом 0/1 на входе C, или при лог. 1 на входе С.На рисунке 17.21 приведена схема соединения микросхем ИЕ9 в многоразрядный синхронный счетчик, которая, к сожалению, снижает общее быстродействие счетчика, так как для его нормальной работы необходимо, чтобы сигнал переноса от младшего разряда прошел через все микросхемы до старшего разряда до подачи очередного тактового импульса.

Рисунок 17.21 – Соединение микросхем ИЕ9 в многоразрядный счетчик

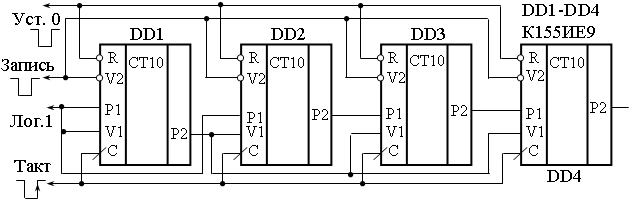

Для получения максимального быстродействия многоразрядного счетчика, равного быстродействию отдельной микросхемы, микросхемы можно соединить по схеме рисунка 17.22. В этом случае сигнал переноса с выхода Р микросхемы DD1 разрешает работу остальных микросхем лишь в те моменты, когда микросхема DD1 находится в состоянии 9, поэтому от счетчика DD2 – DD9 требуется быстродействие в 10 раз меньшее быстродействия микросхемы DD1, что обеспечивается при любой практически встречающейся длине счетчика.

Рисунок 17.22 – Соединение микросхем ИЕ9 в счетчик для получения максимального быстродействия

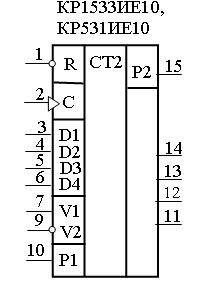

Микросхема ИЕ10 (рисунок 17.23) – синхронный четырехразрядный двойной счетчик, выполненный на двухступенчатых D-триггерах, управляемых фронтом импульса синхронизации.

Рисунок 17.23 – Условное обозначение ИС ИЕ10

Запись информации происходит с информационного входа D сначала в основной триггер, а затем передается во вспомогательный. Выходы счетчика могут быть предварительно установлены в любое состояние. Вход R предназначен для установки счетчика в состояние низкого уровня. Установка в нулевое состояние является асинхронной, т.е. низкий уровень на входе R приводит к обнулению всех триггеров независимо от импульса синхронизации и состояний на любых других входах.

Управление счетом осуществляется с помощью входов V1 и Р1. В режиме счета на входах должен быть высокий уровень. Вход Р1 управляет выходом схемы переноса. Для осуществления операции переноса необходимо, чтобы на входах VI и Р1 был подан сигнал высокого уровня, тогда на выходе P2 также появится сигнал высокого уровня.

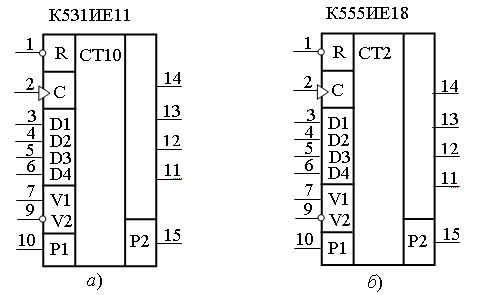

Микросхема 1533ИЕ11 – десятичный синхронный счетчик (рисунок 17.24, а). Логика его работы соответствует логике работы счетчиков ИЕ9. Отличие лишь в том, что для сброса в нуль счетчика ИЕ9 необходима подача на вход R лог. 0, а для сброса в нуль счетчика ИЕ11, кроме подачи на вход ER (разрешение установки нуля) лог.0, необходима подача тактового импульса отрицательной полярности на вход С, по спаду которого и происходит сброс счетчика. Таким образом, все изменения выходных сигналов этой микросхемы происходят по спаду импульсов отрицательной полярности на входе С.

Микросхема

К555ИЕ18

–

четырехразрядный синхронный двоичный

счетчик (рисунок 17.24,б),

выполненный на двухступенчатых

D-триггерах.

Управление режимом счета осуществляется

с помощью входов разрешения счета V1,

предварительной записи

![]() и разрешения переноса. В режиме счета

на указанных входах должен быть высокий

уровень сигнала.

и разрешения переноса. В режиме счета

на указанных входах должен быть высокий

уровень сигнала.

а − ИС К531ИЕ11; б− К555ИЕ18

Рисунок 17.24 – Условное обозначение

Предварительная

установка счетчика осуществляется по

входу установки

![]() .

Предварительная установка и обнуление

счетчика являются синхронными операциями,

которые происходят с приходом

синхроимпульса на вход C

при наличии разрешающих сигналов на

входах

.

Предварительная установка и обнуление

счетчика являются синхронными операциями,

которые происходят с приходом

синхроимпульса на вход C

при наличии разрешающих сигналов на

входах

![]() и

и

![]() .

Управление режимом счета осуществляется

с помощью двух входов: разрешения счета

.

Управление режимом счета осуществляется

с помощью двух входов: разрешения счета

![]() и разрешения переноса

и разрешения переноса

![]() .

В режиме счета на обоих входах должен

быть высокий уровень.

.

В режиме счета на обоих входах должен

быть высокий уровень.

В целом данная микросхема аналогична по функционированию микросхеме ИЕ11, но ее коэффициент пересчета равен 16.

Замечание. Микросхемы счетчиков серии КР531 имеют входные токи по управляющим входам, как правило, больше стандартных. При подаче на входы лог.0 токи могут составлять величины 1 –5 мА и более.