- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

17 Счетчики

Счетчик – это цифровое устройство, осуществляющее счет числа появлений на счетном входе устройства сигналов высокого или низкого логического уровня. Если уровень особо не оговаривается, то будем считать, что счетчик подсчитывает число поступивших на вход уровней лог. 1. Микрооперация счета заключается в изменении числа N в счетчике на ± 1. Счетчик, в котором выполняется микрооперация счета N = N + 1, называется суммирующим, а счетчик, реализующий микрооперацию N = N – 1 – вычитающим. Счетчик называют реверсивным, если он имеет возможность реализовать обе операции. Счетчик, образованный цепочкой из n триггеров, может однозначно подсчитать в двоичном коде N 2n импульсов. Число n определяет количество разрядов двоичного числа, которое может быть записано в счетчик. Число Кcч = 2n называют коэффициентом (модулем) счета. Таким образом, счетчик представляет собой логическое устройство последовательного типа, в котором новое состояние определяется предыдущим состоянием и значением логической переменной на входе.

Для представления чисел в счетчике может использоваться двоичная или двоично-десятичная системы счисления. Причем цифры двоичных разрядов числа определяются, как правило, соответствующими уровнями (лог. 0 или лог. 1) на прямых выходах триггеров. Младшие разряды счетчика относятся ко входным триггерам счетчика, а старшие – к выходным.

Основными эксплуатационными параметрами счетчика, кроме модуля счета, являются быстродействие и потребляемая мощность. Быстродействие счетчика определяется допустимой максимальной частотой входных сигналов Fmax. и временем установления счетчика tуст. Обратная величина, равная

tразр.сч= 1/ Fmax., называется разрешающей способностью. Под разрешающей способностью понимают минимальное время между двумя входными сигналами, в течении которого еще не возникают сбои в работе. Время установления кода tуст равно времени между моментом поступления на вход очередного счетного импульса и переходом всех триггеров счетчика в новое состояние. Счетчики реализуются на Т-триггерах, а также двухступенчатых D-триггерах и универсальных JK-триггерах. По способу организации переносов между триггерами счетчики делятся на счетчики с последовательным, параллельным и последовательно–параллельным переносом. Символом счетчиков на схемах служат буквы СТ (от англ. Сounter – счетчик). При необходимости после символа проставляют число, характеризующее модуль счета (например, 2, 2/5, 2/6, 2/10). В обозначениях микросхем символом счетчика служат буквы ИЕ.

17.1 Двоичные суммирующие счетчики с последовательным

переносом

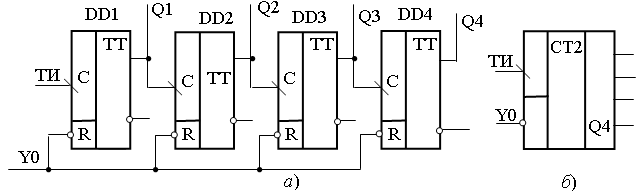

Двоичные счетчики строятся на счетных триггерах, на триггерах типа D, тактируемых фронтом и переведенных в счетный режим, а также на универсальных JK-триггерах. Триггеры включаются последовательно: выход предыдущего соединяется со счетным входом последующего, цепи начальной установки объединяются. Информация снимается, как правило, с прямых выходов триггеров, выходной сигнал (сигнал переноса) – с выхода последнего триггера. На рисунке 17.1, а, б приведена функциональная схема трехразрядного двоичного суммирующего счетчика, выполненного на Т-триггерах (рисунок 17.1, а), и его условное графическое изображение (рисунок 17.1,б).

Приведем счетчик к исходному нулевому состоянию, путем подачи на асинхронный вход R импульса положительной полярности: Y1: СЧ(4): = 0, при этом счет импульсов прекращается, а на выходах Q4–Q1 установится логический ноль. На счетный вход С первого триггера подадим последовательность тактовых импульсов. По функциональному обозначению входа С видно, что переключение триггера возможно только в моменты перехода сигнала из состояния «1» в «0» (перепад 1/0, срез импульса).

Рисунок 17.1 – Функциональная схема:

а − двоичного счетчика; б − условное графическое обозначение

Счетчик должен работать в режиме суммирования, то есть должна выполняться микрооперация прибавления единицы к содержимому счетчика: Y2: СЧ(4): = СЧ(4) + 1.

Таблица 17.1

ai |

Pi |

Si |

Pi+1 |

0 0 1 1 |

0 1 0 1 |

0 1 1 0 |

0 1 0 1 |

Сложение ведется по правилам двоичной арифметики в соответствии с таблицей 17.1. Пусть последовательность чисел в двоичном счетчике описывается совокупностью четырехразрядных двоичных чисел – a4a3a2a1. Сопоставим каждому разряду числа аi двоичное число на выходе Qi. Исходное состояние триггера будем описывать значением аi, входной сигнал (сигнал переноса из предыдущего разряда) – Pi, результат сложения – Оi и перенос в следующий разряд – Pi+1. Причем следует помнить, что весовая функция сигнала переноса всегда равна двум единицам младшего разряда. Поэтому весовая функция первого разряда – 1, второго – 2, третьего – 4 и четвертого – 8. Такой код называют нормально взвешенным и отмечают как 8-4-2-1 (таблица 17.2).

С

приходом первого импульса в счетчике

фиксируется первая единица, так как

значение суммы в соответствии с таблицей

17.1 будет

![]() .

Перенос в следующий разряд будет

отсутствовать, поскольку он формируется

по правилу Pi

+1 = ai

Pi.

Перенос во второй триггер возникает с

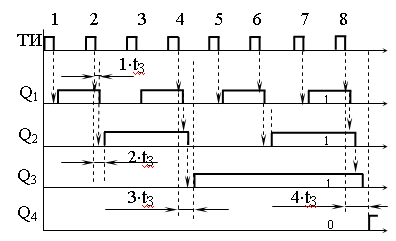

приходом второго ТИ (рисунок 17.2). Третий

триггер переключается в момент прихода

на вход счетчика каждого четвертого

импульса. Четвертый триггер включается

в момент прихода восьмого тактового

импульса.

.

Перенос в следующий разряд будет

отсутствовать, поскольку он формируется

по правилу Pi

+1 = ai

Pi.

Перенос во второй триггер возникает с

приходом второго ТИ (рисунок 17.2). Третий

триггер переключается в момент прихода

на вход счетчика каждого четвертого

импульса. Четвертый триггер включается

в момент прихода восьмого тактового

импульса.

После пятнадцатого импульса все триггеры оказываются в единичном состоянии (a4 a3 а2 a1 = 11112). Шестнадцатый импульс возвращает все триггеры в исходное нулевое состояние, на этом заканчивается первый счетный цикл и процесс повторяется.

Число импульсов поступивших на вход счетчика определяется как М = a4 Q4 + a3 Q3 + a2 Q2 + a1 Q1,

где Q4–Q1 – двоичные числа (0 или 1) в соответствующих разрядах кодовой комбинации, a4 –a1 – весовые коэффициенты этих разрядов (8-4-2-1).

Таблица 17.2 – Таблица истинности

двоичного счетчика

-

N

Q4

Q3

Q2

Ql

0

0

0

0

0

1

0

0

0

1

2

0

0

1

0

3

0

0

1

1

4

0

1

0

0

5

0

1

0

1

6

0

1

1

0

7

0

1

1

1

8

1

0

0

0

9

1

0

0

1

10

1

0

1

0

11

1

0

1

1

12

1

1

0

0

13

1

1

0

1

14

1

1

1

0

15

1

1

1

1

Рисунок 17.2 – Эпюры напряжений двоичного счетчика

Например, по временным диаграммам видим, что состояние на выходах счетчика Q4= 0, Q3= Q2= Q1= 1, откуда следует вывод, что на его вход поступило семь тактовых импульсов:

М = 8 0 + 4 1 + 2 1 + 1 1 = 7.

Более удобной и компактной формой описания закона функционирования цифрового устройства (счетчика) по сравнению с эпюрами напряжений является таблица истинности (таблица 17.2). Основным достоинством двоичных счетчиков с последовательным переносом является исключительная простота функциональной cхемы и, как следствие, высокая надежность. Двоичные счетчики можно использовать как делители частоты, в том числе при использовании различных вариантов обратных связей. В режиме деления частоты у счетчика используется выходной сигнал только последнего триггера, а промежуточные состояния остальных триггеров не учитываются. Любой счетчик может быть использован в качестве делителя частоты, в связи с чем такое устройство будет называться счетчиком-делителем. Такие делители имеют целочисленный коэффициент деления. Современная элементная база позволяет строить делители с дробными коэффициентами деления.

Счетчики-делители в виде самостоятельных изделий имеются в составе всех серий цифровых микросхем, причем номенклатуру счетчиков отличает большое разнообразие. Многие счетчики обладают универсальными свойствами и позволяют управлять коэффициентом и направлением счета, вводить до начала счета исходное число, останавливать счет по команде, наращивать число разрядов. С помощью готовых счетчиков можно решать большинство практических задач.

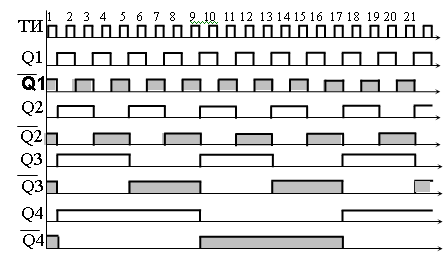

17.2 Вычитающие двоичные счетчики

Для перевода двоичного суммирующего счетчика в режим вычитания достаточно сигнал переноса взять с инверсного выхода каждого предыдущего триггера, а информацию о состоянии счетчика по-прежнему снимать с прямых выходов триггеров (рисунок 17.3). Как и в суммирующем счетчике, сигнал начальной установки подается на входы R всех триггеров, счетные импульсы ТИ поступают на вход первого триггера.

Таблица 17.3

ai |

Pi |

Qi |

Pi+1 |

0 0 1 1 |

0 1 0 1 |

0 1 1 0 |

0 1 0 0 |

Микрооперация, выполняемая счетчиком Y1, CЧ(4) = CЧ(4) – 1; функционирование i-го разряда вычитающего счетчика можно описать логическими выражениями переноса Рi+1 и разности Si из таблицы 17.3.

Из таблицы 17.3 следует, что разность Qi формируется в соответствии с логическим выражением:

![]() ,

,

где аi – исходный код триггера, Рi – сигнал заема, приходящий на вход триггера.

Рисунок 17.3 – Функциональная схема вычитающего счетчика

Формула для получения разности совпадает с выражением, полученным ранее для суммы, поэтому перенос должен подаваться на счетный вход триггера Т, сигнал заема описывается выражением Pi+1 = ai Pi. Диаграммы напряжений вычитающего счетчика приведены на рисунке 17.4.

После первого тактового импульса включается первый триггер. Перепад 1/0 возникающий на выходе Q1, поступает на вход второго триггера и включает его. Аналогично происходит перенос из второго триггера в третий и далее в четвертый (таблица 17.4), в результате чего после первого импульса счетчик оказывается в состоянии а0а3а2а1=1111 (N=15). С приходом каждого очередного импульса сумма в счетчике уменьшается на единицу. После 16-го импульса счетчик обнуляется. На выходе Q4 формируется сигнал переноса.

Рисунок 17.4 – Временные диаграммы двоичного

вычитающего счетчика

Основным недостатком двоичных счетчиков с последовательным переносом является то, что в худшем случае новое состояние n-разрядного счетчика устанавливается с задержкой nt3, где t3 –время переключения триггера. Для уменьшения времени распространения могут использоваться счетчики с параллельным переносом. На рисунке 17.5 представлена схема синхронного двоичного счетчика с параллельным переносом информации. В ее основу положены JK-триггеры со встроенной логикой (J1-J2-J3, К1-К2-КЗ). Тактовый импульс поступает на счетные входы триггеров параллельно (синхронно), т. е. одновременно. Входы начальной установки триггеров объединены и управляются сигналами нулевого уровня. Первый триггер счетчика работает в обычном режиме деления на два, и на его управляющих входах J, K стоят уровни лог. 1.

Таблица 17.4 Таблица иистинности двоичного

вычитающего счетчика

-

N

Q4

Q3

Q2

Ql

0

0

0

0

0

1

1

1

1

1

2

1

1

1

0

3

1

1

0

1

4

1

1

0

0

5

1

0

1

1

6

1

0

1

0

7

1

0

0

1

8

1

0

0

0

9

0

1

1

1

10

0

1

1

0

11

0

1

0

1

12

0

1

0

0

13

0

0

1

1

14

0

0

1

0

15

0

0

0

1