- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

16.2 Сдвигающие регистры

Сдвигающие регистры представляют собой цепочку последовательно стоящих триггеров, логически определенным образом связанных между собой. Сдвигающие регистры могут выполнять следующие операции: сдвиг информации вправо; сдвиг информации влево; прием и выдача информации последовательным или параллельным кодом; хранение.

Сдвиг информации заключается в том, что цифра, хранившаяся в i-ом разряде регистра до сдвига, после каждого тактового импульса передается в (i+1)-й разряд при сдвиге вправо или в соседний (i–1)-й разряд при сдвиге влево. На функциональных схемах регистры обозначаются буквенным символом RG. Под символом ставится стрелка, указывающая направление сдвига: вправо, влево, двунаправленный (реверсивный). Выше указывалось, что понятие «весовых коэффициентов» к разрядам регистра не применяется и вес каждого разряда считается равным единице или определяется записанной в регистр информацией.

16.2.1 Последовательный регистр сдвига вправо

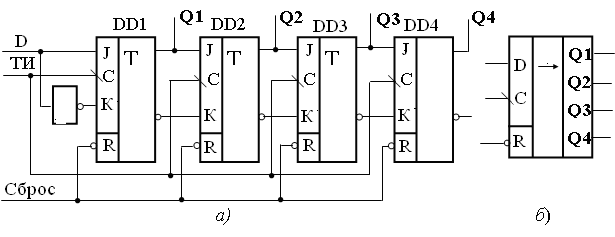

Принципиальными особенностями такого регистра являются следующие: информационные входы каждого последующего триггера соединены с выходами предыдущего, синхронизирующие входы триггеров объединены, вход начальной установки регистров общий. На рисунке 16.5 приведена схема четырехразрядного сдвигающего регистра с последовательным вводом, выполненного на универсальных JK-триггерах, например, K555TB6. Первый триггер при помощи инвертора включен по схеме D-триггера и служит для приема входной информации по входу D. К исходному состоянию, когда все триггеры регистра включены, регистр приводится с помощью импульса начальной установки нулевого уровня У0, подаваемого на вход R. Пусть на вход D первого триггера установлен уровень лог. 1. С приходом первого после У0 тактирующего импульса ТИ произойдет запись единицы в первый триггер.

а − функциональная схема; б − условное изображение

Рисунок 16.5 – Четырехразрядный сдвигающий регистр с последовательным вводом

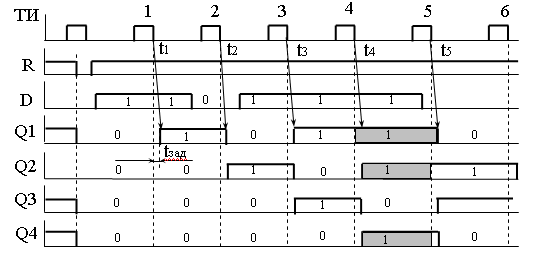

Уровень 1 на прямом выходе Q1 этого триггера устанавливается после прохождения заднего фронта ТИ (перепад 1/0) через время tзад (рисунок 16.6), определяемое быстродействием данного типа триггера. Содержимое второго, третьего и четвертого триггеров при этом не изменится, т.к. во время прохождения среза первого ТИ на выходах первого, второго и третьего триггеров был нулевой уровень. Допустим, к приходу второго тактового импульса ТИ2 на входе первого триггера был установлен нуль, тогда после окончания второго импульса на выходе Q1 будет нуль, на выходе Q2 – лог. 1, на выходах Q3, Q4 будут по прежнему низкие уровни напряжения. Пусть в третьем и четвертом тактах (t3 и t4 соответственно) на вход первого триггера поступает высокий уровень напряжения – единица. Третий тактирующий импульс запишет эту единицу в первый триггер, а нуль с выхода Q1 запишется во второй триггер. Единица с выхода Q2 перепишется в третий триггер, а четвертый триггер останется в нулевом состоянии. Четвертый ТИ запишет входную единицу в первый триггер, включит второй триггер и выключит третий, единицу с выхода Q3 перепишет в четвертый триггер.

Рисунок 16.6 – Временные диаграммы последовательного