- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

16 Регистры

Регистры – это цифровые устройства, служащие для приема, хранения, преобразования и выдачи информации, представленной в виде многоразрядных двоичных слов. Они представляют собой цифровые автоматы Мили, выполненные на синхронных триггерах того или иного типа, со схемами управления входными и выходными сигналами. Элементами структуры регистров являются синхронные триггеры D-типа или SR (JK)-типа со статическим либо динамическим управлением. Одна триггерная ячейка может принять и хранить один двоичный бит информации. Количество разрядов в регистре определяется длиной многоразрядного двоичного слова, подлежащего обработке. При этом «вес», «весовой коэффициент» каждого разряда определяется только содержанием записанной в регистр информации. Занесение информации в регистр обычно называют операцией «ввода» или «записи», а выдачу информации именуют «выводом» или «считыванием». Основные функции, выполняемые регистрами, сводятся к следующим:

– установка триггеров регистра в исходное состояние «0» или «1»;

– прием информации в параллельном или последовательном кодах;

– хранение n-разрядного кода в течение заданного времени;

– сдвиг информации на определенное число разрядов влево или вправо;

– преобразование двоичного параллельного кода в последовательный и наоборот;

– поразрядные логические операции.

В зависимости от функциональных свойств регистры делятся на две категории: накопительные (регистры памяти и хранения) и сдвигающие (сдвиговые). Сдвигающие регистры обладают большими функциональными возможностями по сравнению с простейшими накопительными регистрами. По способу ввода и вывода информации они делятся на параллельные, последовательные и комбинированные.По направлению передачи информации они подразделяются на однонаправленные и реверсивные.

16.1 Параллельные регистры

Двоичное n-разрядное число, предназначенное для хранения, поступает на вход регистра памяти в параллельной форме, т.е. все разряды подаются одновременно. Рационально в качестве регистра использовать простейшие триггеры типа D, управляемые потенциалом или фронтом. В одном корпусе может быть размещено четыре, шесть или восемь отдельных триггеров, связанных общими цепями синхронизации и управления.

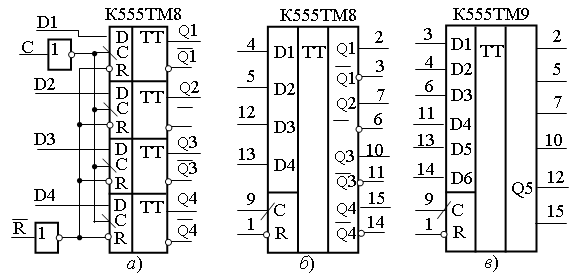

Микросхемы К555ТМ8 и К555ТМ9 представляют собой соответственно четыре и шесть D-триггеров, соответственно, с общим входом синхронизации и общим входом сброса (рисунок 16.1). ИС К555ТМ8 имеет внешние выводы с прямого и инверсного выхода, а ИС К555ТМ9 – только прямой выход.

Схемы выполнены на двухступенчатых, синхронных, динамических D-триггерах. Вход сброса управляется инверсным сигналом, а вход синхронизации – прямым сигналом.

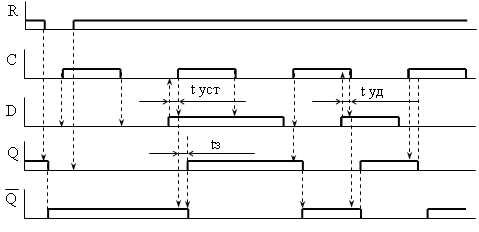

Регистры характеризуются минимальной длительностью импульса для записи информации и определенными временными соотношениями по времени установления tуст и времени удержания tуд на входах управления регистров относительно входов информации. Время установления сигнала – это интервал времени, который необходим для установки сигнала информации с опережением сигнала синхронизации (разрешения) при записи информации.

а − функциональная схема К555ТМ8; б − условное обозначение ИС К555ТМ8; в − функциональное обозначение ИС К555ТМ9

Рисунок 16.1 − D-триггер

Время удержания сигнала – интервал времени, который необходим для завершения записи при удержании сигнала информации на заданном уровне после воздействия сигнала синхронизации. Следует обратить внимание на то, что информационный сигнал единичного или нулевого уровня на входе D должен установиться до прихода переднего фронта импульса за время, превышающее минимальное значение tуст, и должен сохранять свой уровень в течение некоторого времени, превышающего минимальное значение tуд. Следовательно, для обеспечения надежной работы регистра памяти необходимо, чтобы длительность импульса синхронизации Ти превышала tуд минимум в 23 раза. Длительность паузы Тп между импульсами синхронизации также должна существенно превышать минимальное значение tуст. Необходимо отметить, что для записи информации в регистр нет необходимости в очистке регистра, т.е. в его обнулении с помощью сигнала начальной установки.

Временные диаграммы, поясняющие работу триггерной ячейки регистра памяти, приведены на рисунке 16.2. Значительный интерес для разработчиков радиоэлектронной аппаратуры представляют восьмиразрядные регистры памяти серий К555, К531, 1533: ИР22, ИР23, ИР27, ИР33, ИР34, ИР35, ИР37.

Рисунок 16.2 – Временные диаграммы

Все упомянутые регистры имеют достаточно сходную логическую структуру и различаются лишь некоторыми частностями в организации ввода и вывода информации.

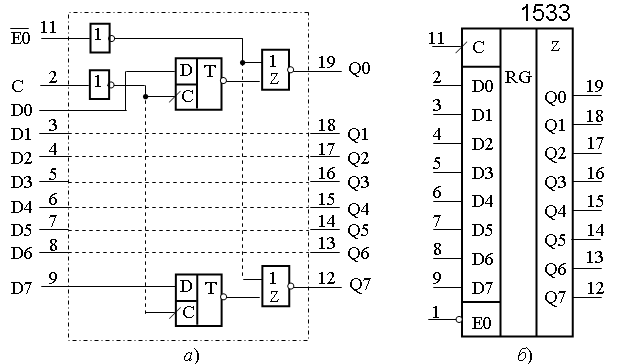

Микросхема

1533ИР37

представляет собой восьмиразрядный

буферный регистр. Логическая структура

и условное обозначение приведены на

рисунке 16.3, а,

б.

Регистр построен на D-триггерах

с импульсным управлением, вход прямой

динамический, переключение производится

положительным фронтом тактового

импульса. Регистр имеет восемь входов

данных D0

– D7

и восемь выходов Q0

– Q7.

Когда на специальный вход

![]() подается низкий уровень, то после

поступления положительного перепада

на тактовый вход С входная информация

появляется на выходах Q.

Если на

установлен высокий уровень, то выходные

буферные каскады переводятся в

высокоимпедансное состояние (состояние

Z).

При низком уровне тактового сигнала С

триггеры регистра находятся в режиме

хранения информации, зафиксированной

при прохождении предыдущего положительного

фронта импульса С.

подается низкий уровень, то после

поступления положительного перепада

на тактовый вход С входная информация

появляется на выходах Q.

Если на

установлен высокий уровень, то выходные

буферные каскады переводятся в

высокоимпедансное состояние (состояние

Z).

При низком уровне тактового сигнала С

триггеры регистра находятся в режиме

хранения информации, зафиксированной

при прохождении предыдущего положительного

фронта импульса С.

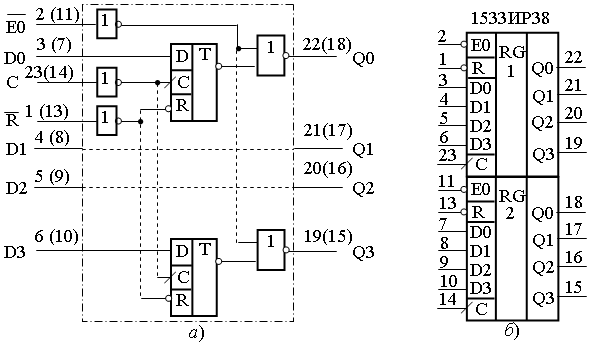

Микросхема 1533ИР38 содержит два одинаковых четырехразрядных регистра, построенных на синхронных D-триггерах с тремя состояниями выхода. Логическая структура одного регистра и условное графическое обозначение ИР38 приведены на рисунке 16.4. Каждый регистр имеет четыре входа и выхода, вход , тактовый вход С и вывод для управления Z-состоянием выходов. Если на вывод подать уровень лог. 1, то выходные буферы окажутся в третьем (разомкнутом) состоянии. Обнуление регистров происходит при подаче на вход низкого уровня напряжения.

Рисунок 16.3 – Регистр: а − структура 1533ИР37; б− уловное обозначение

Данные со входов Di поступят на выходы Qi при поступлении переднего фронта (перепад 0/1) тактового импульса на вход С.

Рисунок 16.4 – Структура и условное обозначение регистра 1533ИР38