- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

15.9 Универсальные jk-триггеры

Особенностью универсального JK-триггера является способность работать в любом из известных режимов.

Асинхронный режим управления по входам S, R заключается в том, что независимо от состояний входов J, K, C на выходе триггера может быть установлен уровень «0» ( = 1, = 0), либо «1» ( = 0, = 1). Пассивное состояние обеспечивается при = = 1, а «запрещенная» комбинация – при = = 0.

В счетный режим триггер переходит при J = K = = = 1, переключение триггера в противоположное состояние при этом осуществляется по перепаду 1/0 на тактовом входе С.

При J= 0, K= 1 первый тактовый импульс по срезу (перепад 1/0 ) установит на выходе Q низкое напряжение (Q = 0) – режим управления нулем.

При J= 1, K= 0 перепад 1/0 на входе С установит на выходе Q единичное напряжение(Q = 1) – режим управления единицей.

При J = 0, K = 0 триггер переходит в режим хранения информации (Qn+1= Qn ) и не реагирует на тактовые импульсы.

Полное функционирование триггера описано в таблице 15.8.

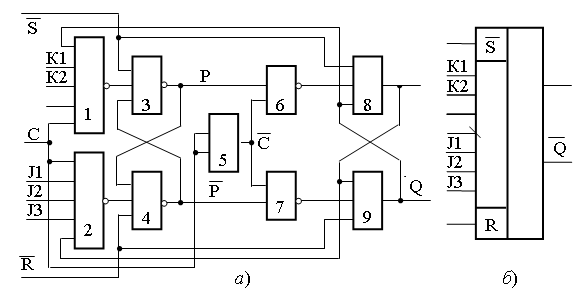

Рисунок 15.18 – Логическая схема:

А − jk − триггера; б − функциональное обозначение

При анализе таблицы 15.8 можно заметить, что переход триггера из состояния «0» в состояние «1» происходит при J = 1 и любом состоянии входа К (строки 1, 3), при этом сигнал на входе К обозначается символом Ф или X. Переключение триггера из «1» в «0» произойдет при К = 1 и любом уровне на входе J (строки 6 и 7). Триггер сохраняет единичное напряжение на выходе при К = 0 и безразличном состоянии входа J (строки 4, 5), а нулевое – при J = 0, К = 0 (строки 0, 2). Это позволяет перейти к минимизированной таблице переходов универсального JK-триггера (таблица 15.8 – сокращенная форма).

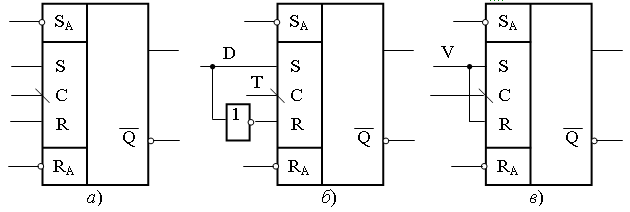

Синхронный режим работы JK-триггера в режиме RS осуществляется при использовании входа J в качестве входа S, входа К в качестве входа R (рисунок 15.19, а). Как и в одноступенчатом синхронном RS-триггере при S=1, R=0, по срезу тактового импульса С на выходе Q будет установлена «1», при S=0, R=1 на выходе установится «0», при S=0 – режим хранения предыдущей информации. В отличие от одноступенчатого триггера управляющая комбинация S=R=1 является не незапрещенной: она переводит универсальный триггер в счетный режим.

Универсальный JK-триггер можно перевести в режим работы триггера типа D. Для этого необходимо информацию (данные D) подать на один из входов J, ее инверсное значение – на вход К, как показано на рисунке 15.19, б.

Таблица 15.8 – Таблица истинности универсального

JK-триггера

tn |

tn+1 |

tn |

tn+1 |

tn |

tn+1 |

||||||||||||||||

N |

Jn |

Kn |

Qn |

Qn+1 |

N |

Jn |

Kn |

Qn |

Qn+1 |

N |

Jn |

Kn |

Qn |

Qn+1 |

|||||||

0 |

0 |

0 |

0 |

0 |

4 |

0 |

0 |

1 |

1 |

0 |

1 |

X |

0 |

1 |

|||||||

1 |

1 |

0 |

0 |

1 |

5 |

1 |

0 |

1 |

1 |

1 |

X |

1 |

1 |

|

|||||||

22 |

0 |

|

0 |

0 |

6 |

0 |

1 |

1 |

0 |

2 |

X |

0 |

1 |

|

|||||||

3 |

1 |

1 |

0 |

1 |

7 |

1 |

1 |

1 |

0 |

3 |

0 |

X |

0 |

|

|||||||

JK-триггер можно перевести в любой из известных режимов с дополнительным управлением по входу V (V – разрешающий, управляющий вход). Для этого объединяются J и К и на них подается разрешающее управляющее напряжение V (рисунок 15.19, в). Входы V и Т являются равноценными, их можно менять местами.

Триггеры JK-типа имеются во многих интегральных сериях микросхем ТТЛ, ТТЛШ, КМОП. В серии К155 триггер ТВ1 со входной логикой на 3И по входам J и К, со входами асинхронной установки , , как изображено на рисунке 15.18. В корпусе размещен один триггер, он имеет максимальную скорость переключения 15 МГц, потребляет ток 15 мА при питающем напряжении +5В.

В быстродействующей серии ТТЛШ К531 имеются триггеры ТВ9, ТВ10, ТВ11. Микросхема ТВ9 – два JK-триггера со сбросом и установкой, ТВ10 – два JK-триггера с установкой, ТВ11 – два JK-триггера со сбросом и установкой, причем входы синхронизации и установки сдвоены.

а − синхронный RS-триггер; б − D-триггер; в − VT-триггер

Рисунок 15.19 – Варианты схем включения JK-триггеров

Усовершенствованная серия ТТЛШ КР1531 имеет микросхему ТВ15, содержащую два JK-триггера со сбросом и установкой, причем вход К проинвертирован. Вход С прямой динамический, информация на выходе появляется в момент действия положительного фронта импульса синхронизации. Поскольку К вход проинвертирован, то такие триггеры легко превращать в D-триггеры.

Частота переключения данных триггеров 100 МГц, средний ток потребления 6,5 мА, напряжение питания + 5 В.