- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

15.8 Счетные триггеры

Счетный триггер или триггер типа Т имеет один счетный (информационный) вход Т и один или два входа начальной установки. Триггер переходит в состояние противоположное исходному с приходом каждого импульса на счетный вход Т (от англ. Toggle – релаксатор). Строятся счетные триггеры на основе триггеров типа D с динамическим управлением или двухступенчатых синхронных триггеров.

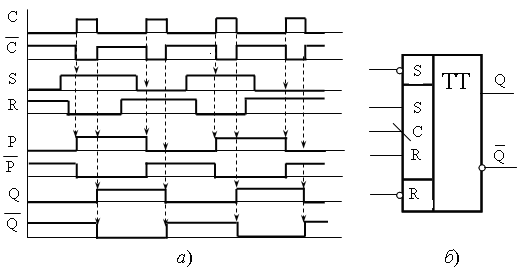

Двухступенчатый триггер строится на основе двух одноступенчатых синхронных триггеров, включенных последовательно. Такая схема построения триггера получила название «M-S» (master-slave = хозяин-раб) или в русской интерпретации ведущий – ведомый. Логическая схема двухступенчатого триггера SR-типа, построенного по схеме M-S, и его структурное изображение приведено на рисунке 15.14. Причем на первый триггер синхронизирующие импульсы C поступают в прямой форме, на вход второго – в инверсной форме.

Когда

на вход синхронизации С приходит

положительный импульс, происходит

запись информации в ведущий триггер. В

это время на входе ведомого триггера

действует нулевой уровень сигнала

![]() ,

триггер находится в неактивном состоянии

и не воспринимает информацию с выходов

P

и

,

триггер находится в неактивном состоянии

и не воспринимает информацию с выходов

P

и

![]() ведущего триггера. В момент перехода

импульса C

с единицы на нуль (1/0) ведущий триггер

переходит в пассивное состояние,

зафиксировав на своих выходах Р,

принятую информацию. Спустя время t31,

равное времени задержки переключения

инвертора 5, единичное напряжение

установится на выходных логических

ячейках ведомого триггера. Последний

перейдет в активный режим записи входной

информации, имеющейся на выходах ведущего

триггера. Сигналы на выходах Q

и

ведущего триггера. В момент перехода

импульса C

с единицы на нуль (1/0) ведущий триггер

переходит в пассивное состояние,

зафиксировав на своих выходах Р,

принятую информацию. Спустя время t31,

равное времени задержки переключения

инвертора 5, единичное напряжение

установится на выходных логических

ячейках ведомого триггера. Последний

перейдет в активный режим записи входной

информации, имеющейся на выходах ведущего

триггера. Сигналы на выходах Q

и

![]() триггера появятся еще через 2t31,

поэтому суммарная задержка составит

3t31

после

поступления отрицательного фронта

тактирующего импульса С. Временные

диаграммы работы двухступенчатого

триггера приведены на рисунке 15.15.

триггера появятся еще через 2t31,

поэтому суммарная задержка составит

3t31

после

поступления отрицательного фронта

тактирующего импульса С. Временные

диаграммы работы двухступенчатого

триггера приведены на рисунке 15.15.

На функциональной схеме синхронизирующий вход С обозначен как инверсный динамический, принадлежность триггера к классу двухступенчатых отмечено сдвоенной буквой Т. Кроме того, показаны асинхронные входы начальной установки триггера (SA, RA), которые могут быть заведены непосредственно на входы ячеек ведущего и ведомого триггеров.

Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

Рисунок 15.4 – Логическая схема:

а − JK-триггера; б − Функциональное обозначение

Рисунок 15.15 – Синхронный двухступенчатый триггер:

а − временные диаграммы; б − функциональное значение

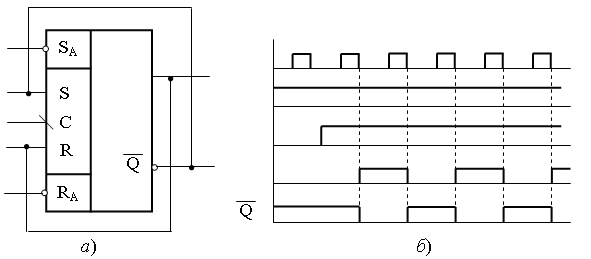

Счетный

триггер

на базе синхронного двухступенчатого

триггера строится следующим образом:

выход

![]() соединяется

со входом S,

а выход Q

– со входом R.

Пусть на выходах триггера Q

= 0,

= 1. После прохождения первого тактирующего

импульса (по его срезу) на входе Q

установится высокий уровень, на входе

– уровень лог.

0.

соединяется

со входом S,

а выход Q

– со входом R.

Пусть на выходах триггера Q

= 0,

= 1. После прохождения первого тактирующего

импульса (по его срезу) на входе Q

установится высокий уровень, на входе

– уровень лог.

0.

После второго импульса триггер вновь возвратится к исходному состоянию, потому что нулевое напряжение с выхода по входу S запишется на прямой выход триггера. Следовательно, текущее состояние триггера определяется его состоянием на предыдущем такте и информацией на входе:

Qn+1

= Qn

![]()

n

Tn.

n

Tn.

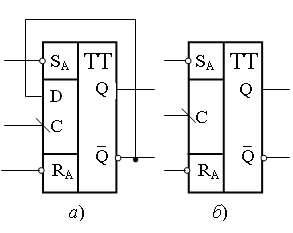

Это выражение соответствует функции «исключающее ИЛИ» или «сумма по mod 2», отчего он получил название «счетный». Его второе название – «делитель частоты на 2», т.к. на два входных положительных синхроимпульса на выходе Q формируется один положительный импульс, как показано на рисунке 15.16, б. В счетный режим можно перевести триггер типа-D, тактируемый фронтом. Для этого достаточно инверсный вход триггера соединить с его информационным входом D (рисунок 15.17, а). С приходом каждого тактирующего импульса триггер переключается в противоположное состояние. Функциональное обозначение триггера Т-типа приведено на рисунке 18.17, б.

а − функциональная схема; б − временные диаграммы

Рисунок15.16 –Т-триггер на основе двухступенчатого триггера

Универсальный синхронный JK-триггер, как правило, строится на основе триггера MS-типа, переведенного в счетный режим. На входы управляющей ячейки 1 ведущего триггера М вводятся дополнительные логически связанные входы J (J = J1 = J2 = J3), аналогичные входам S синхронного триггера, а на вход ячейки 2 – входы К (К = К1 = К2 = К3) подобные входам R (рисунок 15.18).

Рисунок 15.17 – Счетный триггер:

а − на базе D-триггера; б − Функциональное обозначение