- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

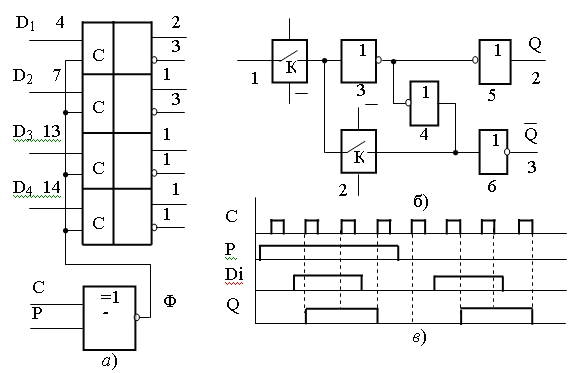

Микросхема к564 тм3

МСХ состоит из четырех D-триггеров со статическим управлением записью. Синхронизация осуществляется единым для всех триггеров управляющим устройством, что показано на функциональной схеме (рисунок 15.11, а). Запись информации по входам D1 – D4 возможна только в случае равенства уровней сигналов синхронизации С (Сlock) и полярности Р (Рolarity), т.е. при С = Р= 1 или С = Р= 0. В случае неравенства уровней С ≠ Р – режим хранения записанной информации. Такая организация управления применяется широко в устройствах КМОП, придавая им дополнительные функциональные возможности.

Функциональные схема одной триггерной ячейки приведена на рисунке 15.11, б. Ее основу составляют два двунаправленных ключа (ячейки 1, 5) и четыре инвертора D3 – D6.

Собственно бистабильную ячейку, которая хранит одно из двух стабильных состояний, образуют инверторы D3, D4. При этом ключ 2 открыт, а ключ 1 заперт. В режиме записи открыт входной ключ 1, а заперт ключ 2, и цепь положительной обратной связи между ячейками D3, D4 разорвана. Эти ячейки работают как два последовательно включенных инвертора. При переходе от режима записи к режиму хранения ключ 2 в цепи обратной связи замыкается быстрее, чем запирается ключ 1 во входной цепи, что обеспечивает режим запоминания информационного сигнала. Временные диаграммы, поясняющие работу триггера, приведены на рисунке 15.11, в.

Следует обратить внимание на то, что с помощью входа Р переключается полярность действия синхроимпульса и запись информации производится как единичными, так и нулевыми уровнями сигналов C и P. Если на входе Р присутствует лог.1, то запись происходит по положительному перепаду синхроимпульса. При нулевом уровне на входе Р запись информации с входов D1 – D4 будет производиться по срезу (отрицательному перепаду положительного импульса) синхроимпульса.

а − функциональная схема; б − функциональная схема одного триггера; в − временные диаграммы работы триггера

Рисунок 15.11 – Микросхема К564ТМ3

15.7 D-триггеры, тактируемые фронтом

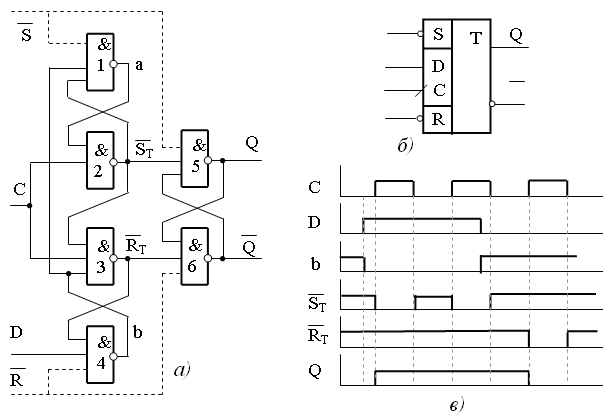

Синхронные триггеры типа D c динамическим управлением по входу C воспринимают входную иинформацию лишь в моменты перехода сигнала на C-входе с уровня лог. 0 на высокий уровень, что существенно улучшает функциональные характеристики триггера. Один из вариантов построения такого триггера на шести логических ячейках И-НЕ приведен на рисунке 15.12.

Собственно

запоминающая ячейка собрана на логических

элементах 5, 6. В цепях управления триггером

![]() ,

RT

стоят бистабильные ячейки 1, 2, 3, 4.

Синхроимпульсы положительной полярности

поступают на входы ячеек 2, 3. В отсутствие

синхроимпульса

,

RT

стоят бистабильные ячейки 1, 2, 3, 4.

Синхроимпульсы положительной полярности

поступают на входы ячеек 2, 3. В отсутствие

синхроимпульса

![]() и выходной триггер находится в режиме

хранения информации.

и выходной триггер находится в режиме

хранения информации.

Пусть

на входе D

установлен логический уровень 1. На

выходе b

ячейки 4 установится лог.

0, поскольку входные сигналы D

=

![]() =

=

![]() имеют высокий уровень. Далее сигнал b

поступает на вход ячейки 1, что приводит

к установлению уровня «1» на ее выходе

(а = 1), так как b

имеют высокий уровень. Далее сигнал b

поступает на вход ячейки 1, что приводит

к установлению уровня «1» на ее выходе

(а = 1), так как b![]() = 0. С приходом положительного фронта

синхроимпульса на выходе ячейки 2

установится нулевой уровень:

= 0. С приходом положительного фронта

синхроимпульса на выходе ячейки 2

установится нулевой уровень:

![]() ,

в результате чего на выходе появится

уровень лог.1:

,

в результате чего на выходе появится

уровень лог.1:

D n+1 = Dn .

На выходе ячейки 3 будет удерживаться уровень лог. 1:

![]() ,

,

где

![]() ,

а C = 1.

,

а C = 1.

Такая ситуация будет сохраняться до конца действия синхроимпульса. При этом любые возможные изменения информации на входе D не проходят далее выхода ячейки 4, потому что на входах ячеек 1 и 3 стоит уровень 0 сигнала . Подобным образом происходит запись уровня 0 на вход D с приходом очередного фронта тактирующего импульса.

Таким образом, время записи информации в триггер D с динамическим управлением определяется длительностью фронта тактирующего импульса и временем задержки распространения на двух логических элементах 2tЗ1.

Триггер

оснащается дополнительными входами

асинхронной установки

![]() (на рисунке 15.12, а

показаны пунктиром). Сигналы заводятся

на основной триггер и входы бистабильных

управляющих ячеек.

(на рисунке 15.12, а

показаны пунктиром). Сигналы заводятся

на основной триггер и входы бистабильных

управляющих ячеек.

Способ

записи информации в D-триггеры

фронтом импульса реализован в триггерах

ТМ2 в любой из выпускаемых серий, например,

ТТЛШ 1531ТМ2, КМОП – К564ТМ2, ЭСТЛ – К500ТМ2.

В каждом корпусе МСХ размещены два

D-триггера

с динамическим управлением и со входами

асинхронной установки

![]() .

.

Способы обозначения динамических входов триггеров показаны на рисунке 15.13.

Рисунок 15.12 – D-триггер с динамическим управлением:

а − логическая структура; б − функциональное обозначение;

в − временные диаграммы

Рисунок 15.13 − Обозначения динамических входов триггеров:

а − при управлении положительным фронтом; б − при управлении отрицательным фронтом