- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

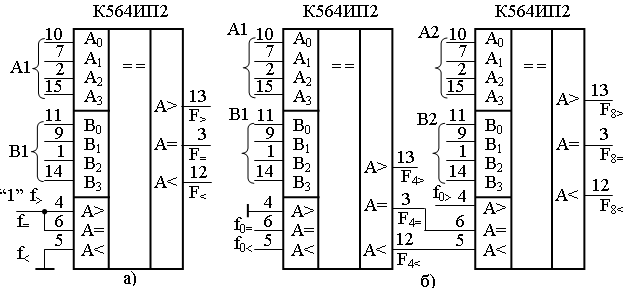

13.2 Цифровые компараторы и их применение

Цифровые компараторы 555, 531, 561, 564 серий в функциональном отношении близки друг к другу. Они определяют равенство или неравенство сравниваемых четырехразрядных чисел, имеют дополнительные входы для наращивания разрядности. На рисунке 13.2 приведено условное графическое обозначение ИС 564ИП2. Числа, подлежащие сравнению, подаются на входы А0 – А3 и В0 – В3 (А3 и В3 – старшие разряды). Результаты сравнения появляются на выходах А > В, А = В, А < В. Микросхема имеет расширяющие входы А < В, А = В, А > В, что позволяет наращивать разрядность сравниваемых чисел без привлечения дополнительных элементов. Если используется только один корпус ИП2, то на вход А = В необходимо подать высокий уровень, а на вход А В и А В – низкие уровни.

При каскадировании микросхем входы расширения можно использовать для программирования выполняемых функций (таблица 13.1). Для удобства описания выполняемых функций введем следующие обозначения:

A = A3A2A1A0, B = B3B2B1B0 – входные двоичные слова;

f, f, f – двоичный код на входах наращивания разрядности, соответственно, , , .;

F, F , F – сигналы на выходах микросхемы, соответственно, , , .

Функции, реализуемые МСХ К564ИП2, запишутся в следующем виде:

F= = f= F(A = B), F = F(A < B) f F(A = B),

F

= f

F(A>B)

![]() .

.

Функции программируются с помощью входов А > В, А = В, А < В (4, 6, 5) и соответствуют таблице программирования (таблица 13.1).

Таблица 13.1 – Таблица истинности К564ИП2

ВХОДЫ |

ВЫХОДЫ |

||||

f(A>) |

f=(A) |

f(A<) |

F (A >В) |

F =(A = B) |

F(A<B) |

0 |

0 |

0 |

0 |

0 |

F(A <B) |

0 |

0 |

1 |

0 |

0 |

F(A B) |

0 |

1 |

0 |

0 |

F (A = B) |

F(A< B) |

0 |

1 |

1 |

0 |

F (A = B) |

F(A B) |

1 |

0 |

0 |

F (A B) |

0 |

F(A <B) |

1 |

0 |

1 |

F (A > B) |

0 |

F (AB) |

1 |

1 |

0 |

F (A > B) |

F (A = B) |

F (A<B) |

1 |

1 |

1 |

F(A > B) |

F (A = B) |

F(A B) |

На рисунке 13.3, а в качестве примера приведена схема преобразования разрядности сравниваемых чисел. На приведенном рисунке f = 1, f= = 1, f = 0. Подставив эти значения в вышеприведенные формулы, получим:

F= = F(А = В), F = F(А > В), F = F(А < В), F F = 0.

Отсюда видно, что при таком управлении МСХ соотношения «меньше», «больше» и «равно» входных четырехразрядных чисел полностью переносятся на выходные функции F и F, которые можно рассматривать как выходные одноразрядные числа.

На рисунке 13.3 показана 8-ми разрядная схема сравнения двоичных чисел, построенная их двух 4-х разрядных ИС 561ИП2. На вход А> первой МСХ (сравнение младших разрядов числа) можно подавать либо низкий, либо высокий уровень напряжения. Сигнал переноса f0 необходимо подать на вход А> второго компаратора. Из рисунка 13.3 следует, что

F8= = F4=F(A2 = B2),

F8 = F(A2 < B2) V f4 F(A2 = B2),

F8

= f0

![]() ,

,

A2 = A7 A6 A5 A4, B2 = B7 B6 B5 B4.

Таблица 13.1 – Таблица истинности К564ИП2

ВХОДЫ |

ВЫХОДЫ |

||||

f(A>) |

f=(A) |

f(A<) |

F (A >В) |

F =(A = B) |

F(A<B) |

0 |

0 |

0 |

0 |

0 |

F(A <B) |

0 |

0 |

1 |

0 |

0 |

F(A B) |

0 |

1 |

0 |

0 |

F (A = B) |

F(A< B) |

0 |

1 |

1 |

0 |

F (A = B) |

F(A B) |

1 |

0 |

0 |

F (A B) |

0 |

F(A <B) |

1 |

0 |

1 |

F (A > B) |

0 |

F (AB) |

1 |

1 |

0 |

F (A > B) |

F (A = B) |

F (A<B) |

1 |

1 |

1 |

F(A > B) |

F (A = B) |

F(A B) |

Следовательно, функции, выполняемые схемой, соответствуют таблице 13.1.Можно построить схему последовательного включения большего числа ИС К561ИП2 для сравнения 4m-разрядных чисел, где m – число ИС. Сигналы f и f= всегда подаются на младшую ИС, а сигнал f – на старшую ИС (деление на младшие и старшие ИС производится в соответствии с младшими и старшими разрядами сравниваемых чисел). Входы A < B, A = B всех остальных МСХ следует соединить с одноименными выходами предыдущих, а на входы A > B подать лог. 1.

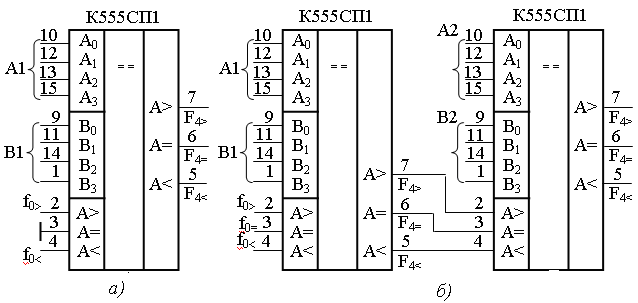

При последовательном включении ИС снижается быстродействие схем сравнения многоразрядных чисел (увеличивается задержка распространения сигнала), поэтому предпочтительнее параллельное (пирамидальное) соединение МСХ (рисунок 13.5). Интегральная МСХ К555СП1 (рисунок 13.4) выполняет функции сравнения 4-х разрядных двоичных чисел, но ее переключательные функции отличаются от ранее рассмотренных для К564ИП2.

а − четырехразрядных; б − восьмиразрядных

Рисунок 13.3 – Схемы сравнения разрядности чисел

Рисунок 13.4 − Цифровой компаратор двоичных чисел:

а − четырехразрядный компаратор ИС К555СП1; б − восьмиразрядный компаратор на двух ИС К555СП1

Переключательные функции описываются следующими выражениями: F4= = f= F(А1 = В1),

![]() ,

,

![]() .

.

На рисунке 13.4 приведена 4-х разрядная схема и 8-ми разрядная схема сравнения двоичных чисел.

Нетрудно заметить, что наблюдается полная симметрия по отношению к операциям больше и меньше при каскадном наращивании разрядов. Функции, выполняемые ИС К555СП1, могут программироваться сигналами f0, f0=, f0 (таблица 13.2).

Таблица 13.2 – Таблица истинности восьми разрядного