- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

13 Схемы сравнения цифровых кодов

13.1 Общие положения

Схемы сравнения кодов довольно часто встречаются в промышленных цифровых приборах, устройствах вычислительной техники, измерительных системах и служат для выявления соответствия некоторого значения цифрового кода заданному уровню. Схемы сравнения кодов условно можно разделить на две группы:

– выявляющие совпадение кодов;

– выявляющие большее число.

Схемы, выявляющие совпадения кодов, должны обеспечить выходной сигнал, равный единице, только в случае полного совпадения сравниваемых кодов. Сравниваться могут числа, заданные в двоичном и двоично-десятичном коде, имеющие одинаковое количество разрядов: А = Аn…А2А1А0, В = Вn…В2В1В0. Совпадение кодов означает равенство чисел во всех разрядах:

Аn = Вn, …, А2 = В2, А1 = В1, А0 = В0.

При сравнении двух

одноразрядных кодов можно не составлять

таблицу истинности, поскольку для

совпадения кодов достаточно, чтобы оба

разряда были равны нулю либо единице.

Такую функцию реализует схема

равнозначности:

![]() =

Аi

Вi,

а ее инверсивное

значение имеет функция неравнозначности

(«исключающее ИЛИ»):

=

Аi

Вi,

а ее инверсивное

значение имеет функция неравнозначности

(«исключающее ИЛИ»):

![]() ,

т.е. сумма по модулю два.

,

т.е. сумма по модулю два.

При

равенстве кодов реализуется функция

![]() …

…![]() ,

преобразуя которую по правилу де Моргана

(отрицания), получим

,

преобразуя которую по правилу де Моргана

(отрицания), получим![]()

![]()

![]() .

.

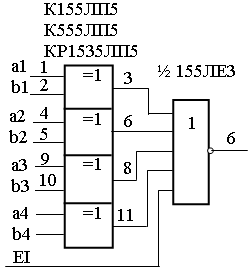

Последнее выражение можно реализовать с помощью логических схем «исключающее ИЛИ» и схемы ИЛИ (рисунок 13.1). За основу взята МСХ К133ЛП5 (555, 1531, 1533 и др.), содержащая четыре 2-х входовых элемента «исключающее ИЛИ» и 4-х входовой логический элемент ИЛИ-НЕ (половина ИС К155ЛЕ3). Логический элемент ИЛИ-НЕ имеет дополнительный вход разрешения приема сигнала EI (Enable Input). Управляющий сигнал на этом входе разрешает (или запрещает) прием сигнала по каждому входу ЛЭ.

Построение

схемы, выявляющей большее (или меньшее)

из двух сравниваемых чисел, рассмотрим

на примере сравнения двух двоичных

чисел А = Аn…А2А1А0,

В = Вn…В2В1В0.

Схема должна обеспечить на выходе сигнал

N,

равный единице в случае,

когда A

> B.

Если же А

В, то сигнал на выходе такой цепи должен

быть равен нулю. Для получения логической

функции, которую должна реализовать

схема, нужно взять за основу ячейку,

сравнивающую одноразрядные коды. При

этом очевидно что Ai

> Bi,

если Ai

=1 и Bi

= 0, т.е.

![]() .

.

Многоразрядные

числа следует

сравнивать следующим образом. Вначале

сравнивают коды в первом, старшем

разряде. Если Аn

> Bn,

следовательно,

![]() ,

и сразу можно

сделать вывод, что независимо от

содержания младших разрядов

,

и сразу можно

сделать вывод, что независимо от

содержания младших разрядов

АВ.

Если же в первом разряде коды совпадают,

то

![]() и нужно перейти к анализу следующего

разряда. Если в следующем разряде

An–1>Bn–1,

тогда

и нужно перейти к анализу следующего

разряда. Если в следующем разряде

An–1>Bn–1,

тогда

![]() 1

и, следовательно, А>B.

Если же в этом разряде An-1

= Bn-1,

то с учетом равенства бит старшего

разряда получим промежуточный результат:

1

и, следовательно, А>B.

Если же в этом разряде An-1

= Bn-1,

то с учетом равенства бит старшего

разряда получим промежуточный результат:

![]() .

.

Рассуждая таким образом, получим:

![]() ;

;

![]() ;

…

;

…

![]() ;

;

![]() .

.

Рисунок 13.1 – Cхема cравнения кодов на равенство

Если

хотя бы одно значение

![]() окажется равным единице, то на выходе

дизьюнктора

окажется равным единице, то на выходе

дизьюнктора

![]() установится высокий уровень, указывающий

на то, что А>В.

установится высокий уровень, указывающий

на то, что А>В.

Сигналы

Ri,

полученные

по ходу решения задачи,

можно

использовать для реализации функции

R,

указывающей на равенство кодов. Если

буквой Мi

обозначить функцию, принимающую уровень

лог.1

при Аi

< Вi

(![]() ),

то формулу для Ri

можно записать в следующем виде:

),

то формулу для Ri

можно записать в следующем виде:

![]() .

.

Это означает, что Ri = 1 в том случае, когда ai = bi.

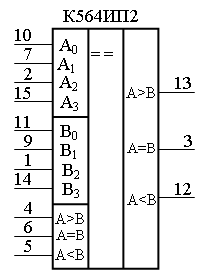

Реализовать устройство, выявляющее большее число, можно на ЛЭ низкой степени интеграции, хотя в этом нет необходимости, поскольку в разных сериях имеются цифровые четырехразрядные компараторы. Примером могут служить микросхемы К564ИП2, К555СП1, К531СП1 (ТТЛШ), выпускаемые отечественной промышленностью.

Рисунок 13.2 – Условное графическое обозначение

ИС К564ИП2