- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

11 Мультиплексоры

11.1 Назначение и принцип работы

Назначение

мультиплексоров (от англ. Multiplexer

– MUX – многократный) – коммутировать

в нужном порядке входную информацию,

поступающую с нескольких шин, на одну

выходную. Мультиплексор имеет несколько

информационных входов D0,

D1,…,DN

- 1, адресные

входы A0,

A1,…

AN - 1,

вход для подачи стробирующего сигнала

C и один выход D0 (![]() ).

Причем количество входов N и число

адресных шин n

связаны соотношением N

= 2n.

Входные информационные сигналы DI

– Data

Input

– будем сокращенно именовать D.

Стробирующий сигнал мультиплексора

выбирает один из входов и подключает

его к входу (селектирует входную шину).

Основу мультиплексора составляет

линейный дешифратор, выходы которого

объединены по ИЛИ. Логическая функция,

которую реализует мультиплексор:

).

Причем количество входов N и число

адресных шин n

связаны соотношением N

= 2n.

Входные информационные сигналы DI

– Data

Input

– будем сокращенно именовать D.

Стробирующий сигнал мультиплексора

выбирает один из входов и подключает

его к входу (селектирует входную шину).

Основу мультиплексора составляет

линейный дешифратор, выходы которого

объединены по ИЛИ. Логическая функция,

которую реализует мультиплексор:

![]()

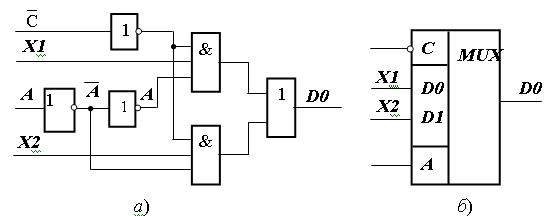

На рисунке 11.1, а приведена принципиальная схема простейшего мультиплексора-селектора вида «две линии к одной» (2:1).

Собственно

мультиплексор выполнен на двух логических

ячейках И, выполняющих роль дешифратора,

и одной ячейки ИЛИ, логически суммирующих

выходные сигналы дешифратора. Адрес

выбранного направления определяется

сигналом А: при А = 0 работает верхняя

ячейка И и входной сигнал Х1 появляется

на выходе D0, при А = 1 включена нижняя

ячейка И и на выходе появляется сигнал

Х2. Синхросигнал

![]() управляет работой ячеек в дешифраторе.

При

=

1 работа дешифратора запрещена, на выходе

D0 устновлен лог

0.

При

= 0 ячейки дешифратора активизированы.

Информация проходит на выход с того

входа, двоичный код которого указан на

адресных входах. Кроме того, вход

позволяет наращивать разрядность

дешифратора по числу входов. Условное

графическое изображение простейшего

мультиплексора приведено на рисунке

11.1, б.

управляет работой ячеек в дешифраторе.

При

=

1 работа дешифратора запрещена, на выходе

D0 устновлен лог

0.

При

= 0 ячейки дешифратора активизированы.

Информация проходит на выход с того

входа, двоичный код которого указан на

адресных входах. Кроме того, вход

позволяет наращивать разрядность

дешифратора по числу входов. Условное

графическое изображение простейшего

мультиплексора приведено на рисунке

11.1, б.

а − принципиальная схема; б − условное изображение

Рисунок 11.1 – Мультиплексор – селектор вида 2:1

11.2 Мультиплексоры ттл

Мультиплексоры ТТЛ, как самостоятельные изделия, широко представлены во многих сериях (К155, К133, К555, К531, К1533 и др.). Строятся они на основе линейных дешифраторов, как было показано выше, и отличаются по числу информационных и адресных входов, наличием или отсутствием стробирующего входа, характером выходных сигналов (прямые, инверсные или парные).

Микросхема

К555КП11

(КП14,

КП16)

–

четыре

мульти-плексора,организованных

для мультиплексирования двух каналов

в один (![]() )

с общим

дешифратором адреса.

)

с общим

дешифратором адреса.

Рисунок 11.2 –Условное графическое обозначение ИС:

а − К555КП11; б − функциональная схема

На

рисунке 11.2, а,

б

представлены

функциональная схема и условное

графическое обозначение ИС К555 КП11.

Всостав микросхемы входит четыре

мультиплексора

![]() ,

аналогичных

показанному на рисунке

11.1.

Отличие состоит в том, что разрешающий

вход

,

аналогичных

показанному на рисунке

11.1.

Отличие состоит в том, что разрешающий

вход

![]() здесь заменен входом

Е,

обеспечи-вающим

перевод

выходов мультиплексора в высокоимпедансное

состояние Z. Когда на входе Е уровень

лог.1

все выходы находятся в третьем состоянии,

рабочий режим обеспечивается уровнем

лог.

0 на этом входе. Выбор канала производится

с помощью адресной шины А. При нулевом

уровне адреса подключены шины D0,

при уровне лог.

1 на выход поступают сигналы с шин D1.

здесь заменен входом

Е,

обеспечи-вающим

перевод

выходов мультиплексора в высокоимпедансное

состояние Z. Когда на входе Е уровень

лог.1

все выходы находятся в третьем состоянии,

рабочий режим обеспечивается уровнем

лог.

0 на этом входе. Выбор канала производится

с помощью адресной шины А. При нулевом

уровне адреса подключены шины D0,

при уровне лог.

1 на выход поступают сигналы с шин D1.

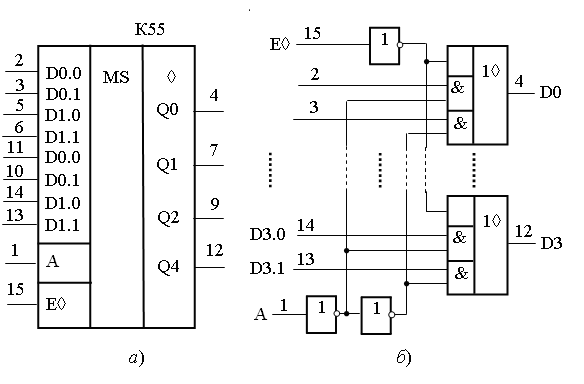

МикросхемаК555КП13

– четыре

мультиплексора,

органи-зованных

для мультиплексирования двух каналов

в один (![]() ,

с общим дешифратором адреса. В

отличие от ИС

К555 КП11, она имеет

на выходе регистр хранения информации,

выполненный на двухтактных синхронных

триггерах типа «M-S»

(«ведущий-ведомый»). Запись информации

в выходной регистр производится в момент

среза тактирующего импульса на входе

С (перепад 1/0).

,

с общим дешифратором адреса. В

отличие от ИС

К555 КП11, она имеет

на выходе регистр хранения информации,

выполненный на двухтактных синхронных

триггерах типа «M-S»

(«ведущий-ведомый»). Запись информации

в выходной регистр производится в момент

среза тактирующего импульса на входе

С (перепад 1/0).

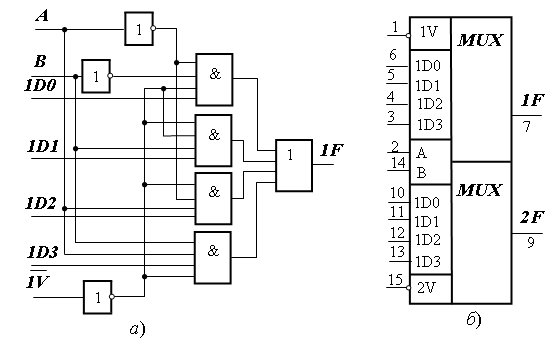

Микросхема

К555 КП2

– это два мультиплексора

![]() с общими адресными входами А, В выбора

канала и раздельными входами выбора

одного из мультиплексоров 1

с общими адресными входами А, В выбора

канала и раздельными входами выбора

одного из мультиплексоров 1![]() и 2

(рисунок 11.3). Каждый мультиплексор

реализует следующую функцию:

и 2

(рисунок 11.3). Каждый мультиплексор

реализует следующую функцию:

![]() .

.

Двоичный код, который набран на адресных входах, разрешающий работу одного из информационных входов каждого мультиплексора. Сигнал с выбранного информационного входа появляется на выходе только при наличии на стробирующем входе данного мультиплексора сигнала низкого уровня.

Рисунок 11.3 – Логическая структура ½ мултиплексора

а −К555КП2; б − условное графическое изображение

Микросхемы

К555КП7 и

К555КП15–

имеют

организацию мультиплексирования восьми

каналов в один. Они имеют восемь

информационных входов D0

– D7,

три адресных входа A,

B,

C,

разрешающий вход Е, и прямой D

и инверсный выход

![]() .

Функциональная схема и условное

графическое обозначение ИС К555КП15

приведено на рисунке 11.4, б.

В отличие от К555 КП7, этот мультиплексор

имеет три состояния выхода. Закон

функционирования мультиплексора:

.

Функциональная схема и условное

графическое обозначение ИС К555КП15

приведено на рисунке 11.4, б.

В отличие от К555 КП7, этот мультиплексор

имеет три состояния выхода. Закон

функционирования мультиплексора:

![]()

Сигнал

с выбранного информационного входа

появится на выходе при низком уровне

разрешающего сигнала

![]() ,

при высоком уровне сигнала

на обоих выходах установится состояние

Z.

,

при высоком уровне сигнала

на обоих выходах установится состояние

Z.

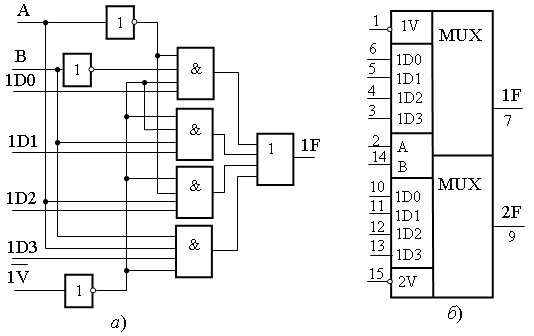

Микросхема

К155КП1

имеет 16 информационных входов D0

D15

и четыре управляющихвхода А, B,

C,

D,

разрешающий вход V

и один инверсный выход

![]() (рисунок 11.4, а).

В зависимости от цифровой комбинации

на управляющих входах сигналы с

соответствующего информационного входа

проходят в инвертированном виде на

выход микросхемы. Передача информации

возможна, если на разрешающий вход

действует напряжение низкого уровня.

(рисунок 11.4, а).

В зависимости от цифровой комбинации

на управляющих входах сигналы с

соответствующего информационного входа

проходят в инвертированном виде на

выход микросхемы. Передача информации

возможна, если на разрешающий вход

действует напряжение низкого уровня.

Рисунок 11.4 – Условное графическое изображение:

а − ИС К155КП1; б − ИС К555КП15

При высоком уровне на разрешающем входе схема блокируется и на выходе микросхемы возникает напряжение высокого уровня.