- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

Реализация функции

Управляющие сигналы

![]() связаны между собой конъюнктивно, и

дешифратор переходит в активное состояние

при Е1

= 0, Е2

= 0, Е3

= 1. При любых других сочетаниях этих

сигналов выходы дешифраторов переходят

в неактивное состояние с высокими

выходными уровнями напряжения. В том

случае, когда число единиц в выходной

функции меньше числа нулей, на выходе

дешифратора предпочтительнее использовать

логическую схему ИЛИ.

связаны между собой конъюнктивно, и

дешифратор переходит в активное состояние

при Е1

= 0, Е2

= 0, Е3

= 1. При любых других сочетаниях этих

сигналов выходы дешифраторов переходят

в неактивное состояние с высокими

выходными уровнями напряжения. В том

случае, когда число единиц в выходной

функции меньше числа нулей, на выходе

дешифратора предпочтительнее использовать

логическую схему ИЛИ.

10.3 Дешифраторы-демультиплексоры ттл

Устройства типа дешифратор-демультиплексор достаточно широко представлены во многих сериях ТТЛ и ТТЛШ (К155, К133, К555, К1530…). Они отличаются по количеству адресных входов, набору управляющих сигналов, организации выхода, потребляемой мощности и способны решать многие задачи, выдвигаемые практикой. Дешифраторы выпускаются на два, три и четыре входа.

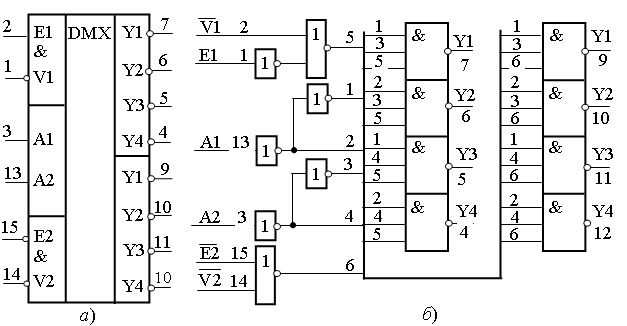

Микросхема

К155ИД4

– сдвоенный дешифратор-демуль-типлексор

2![]() 4

с общими входами дешифрируемого кода

и раздельным управлением шинами

разрешения E1,

V1

и E2

и V2

(рисунок 10.4).

4

с общими входами дешифрируемого кода

и раздельным управлением шинами

разрешения E1,

V1

и E2

и V2

(рисунок 10.4).

Активным уровнем выходных сигналов является лог. 0. В зависимости от схемы включения микросхема может быть использована в следующих режимах: два дешифратора с двух каналов на четыре; два демультиплексора с одного канала на четыре; дешифратор с трех каналов на восемь; демультиплексор с одного канала на восемь.

а − дешифратор К155ИД4; б − функциональная схема

Рисунок 10.4 –Условное графическое изображение

Два дешифратора

24

получаются, когда входы А1 и А2 служат

как адресные, на разрешающих входах

первого дешифратора устанавливают Е1

– лог. 1,

![]()

лог. 0,

на разрешающих входах второго дешифратора

лог. 0,

на разрешающих входах второго дешифратора

![]() и

и

![]() – лог. 0.

При построении двух демультиплексоров

с одного канала на четыре можно подать

разрешающие сигналы Е1 – лог.

0,

лог. 0,

а входы

и

– лог. 0.

При построении двух демультиплексоров

с одного канала на четыре можно подать

разрешающие сигналы Е1 – лог.

0,

лог. 0,

а входы

и

![]() использовать в качестве информационных.

В этом случае фаза (полярность) входных

и выходных сигналов будет совпадать.

Микросхему можно использовать в качестве

дешифратора трехразрядного кода на

восемь выходов и как демультиплексор

от одного входа на восемь выходов. Для

получения третьего адресного входа А3

соединим входы

и Е1 и на объединенный вход подадим

старший разряд (А3) адреса (рисунок 10.5).

использовать в качестве информационных.

В этом случае фаза (полярность) входных

и выходных сигналов будет совпадать.

Микросхему можно использовать в качестве

дешифратора трехразрядного кода на

восемь выходов и как демультиплексор

от одного входа на восемь выходов. Для

получения третьего адресного входа А3

соединим входы

и Е1 и на объединенный вход подадим

старший разряд (А3) адреса (рисунок 10.5).

При нулевом значении

А3 работает верхний канал дешифратора

(![]() ),

т. к. на входе Е1 устанавливается высокий

уровень напряжения. При высоком уровне

третьего адреса активизируются выходы

нижнего канала (

),

т. к. на входе Е1 устанавливается высокий

уровень напряжения. При высоком уровне

третьего адреса активизируются выходы

нижнего канала (![]() ),

поскольку на

),

поскольку на

![]() – активный нулевой уровень. При

использовании дешифратора как

демультиплексора 1: 8 информацию (D

–Data)

следует подавать одновременно на входы

и

.

– активный нулевой уровень. При

использовании дешифратора как

демультиплексора 1: 8 информацию (D

–Data)

следует подавать одновременно на входы

и

.

Рисунок 10.5 – Дешифратор 3:8 на К155ИД4

Активные уровни информационных сигналов при этом будут совпадать с активными уровнями выходных сигналов дешифратора. Структура микросхемы позволяет производить дальнейшее наращивание разрядности демультиплексора.

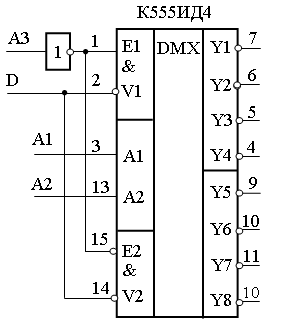

Микросхема

К555ИД19 служит

для преобразования двоичного

четырехразрядного кода в унитарный

16-разрядный код. Микросхема имеет четыре

адресных входа А3А2А1А0

два входа управления

![]() ,

,

![]() и 16 выходов 0,1,…,15 с активными низкими

уровнями напряжения (рисунок 10.6, а).

и 16 выходов 0,1,…,15 с активными низкими

уровнями напряжения (рисунок 10.6, а).

Для создания режима

демультиплексора 1:16 один из входов V

заземляют (создают уровень лог.

0), а другой используют в качестве

информационного. Кодовая комбинация

на адресных входах переводит один из

шестнадцати выходов в активное состояние,

которому соответствует

![]() .

Остальные пятнадцать выходов при этом

сохраняют уровень лог.

1. Сигналы

на активном выходе повторяют в прямом

виде сигналы, поступающие на информационный

вход (

.

Остальные пятнадцать выходов при этом

сохраняют уровень лог.

1. Сигналы

на активном выходе повторяют в прямом

виде сигналы, поступающие на информационный

вход (![]() или

или

![]() ).

).

Рисунок 10.6 – Условное изображение микросхемы:

а − К555ИД19; б − схема дешифратора 5:32

Если на обоих разрешающих входах поддерживать уровень

V0 = V1 = 0 микросхема работает как дешифратор четыре входа – шестнадцать выходов. Потенциал U1 на любом разрешающем входе установит уровень лог. 1 на всех выходах независимо от состояния адресных входов.

Микросхемы К555ИД19 можно применять для преобразования входных сигналов, разрядность которых больше четырех.

На рисунке 10.6, б показана схема демультиплексора (дешифратора) пятиразрядного двоичного кода, собранного на двух микросхемах.

Шины младших

четырех разрядов соединяют с входами

А0

А4 обоих приборов, а сигналы старшего

разряда подают в прямом виде на один из

разрешающих входов первой микросхемы

и в инверсном – на разрешающий вход

другой. Вторые разрешающие входы

![]() заземляются (режим дешифратора), либо

на них подают информационные сигналы

(режим демультиплексора). Пирамидальная

система на 17 микросхемах позволяет

получить устройство с 256 выходами.

заземляются (режим дешифратора), либо

на них подают информационные сигналы

(режим демультиплексора). Пирамидальная

система на 17 микросхемах позволяет

получить устройство с 256 выходами.

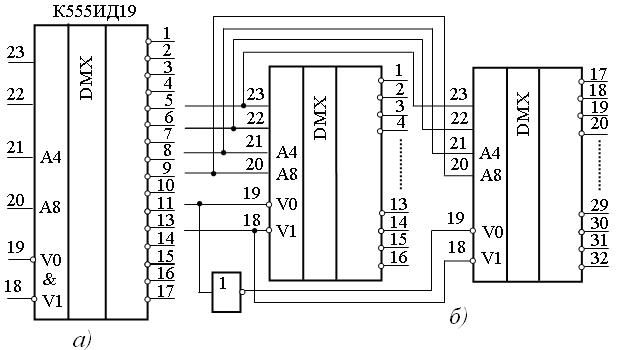

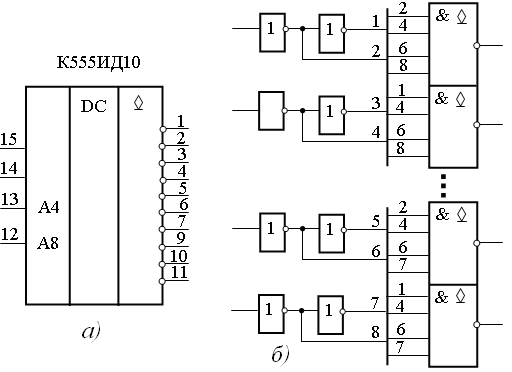

Микросхема К555ИД10 – дешифратор классического типа, преобразующий четырехразрядный двоично-десятичный код в десятичный. На рисунке 10.7 приведена функциональная схема дешифратора. Все выходы микросхемы выполнены с открытым коллектором (Ucc до 15 В), и логическая функция выполняется при подключении нагрузки между выходом микросхемы и источником питания.

Рисунок 10.7 − Дешифратор К155ИД10:

а − условное обозначение; б − структурная схема

Если десятичный эквивалент входного кода превышает 9, то на всех выходах дешифратора установится напряжение высоких уровней. Эти устройства могут дешифрировать числа 0 8, тогда вход А8 можно использовать как разрешающий с низким активным уровнем. На этот вход можно подавать данные, если использовать ИД10 как демультиплексор на восемь выходов.

В функциональный состав цифровых маломощных КМОП-структур (564, 1564) также включены ряд дешифраторов.

Микросхема К564ИД1 служит для преобразования двоично-десятичного кода в десятичный или двоичного в восьмеричный, как и К555ИД10, но, в отличие, от нее имеет прямые выходы.

Микросхема К564ИД4 – дешифратор возбуждения одноразрядного семисегментного жидкокристаллического индикатора, микросхема К1564ИД3 – дешифратор на четыре входа – шестнадцать выходов.