- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

8.3 Логические элементы, регистры, счетчики

Цифровые микросхемы К6500 предназначены для обработки цифровых сигналов с тактовой частотой до 1000 МГц в контрольно-измерительных приборах, аппаратуре связи и ЭВМ. При эксплуатации ИС К6500 имеют предельно допустимые режимы, приведенные ниже. В состав серии 6500 входят: два логических элемента ЛР1 и ЛР2, счетный триггер ТТ1, 4-разрядный ИР1 и 8-разрядный ИР2 сдвигающие регистры и два двоичных счетчика – ИЕ2 (4-разрядный), ИЕ3 (8-разрядный).

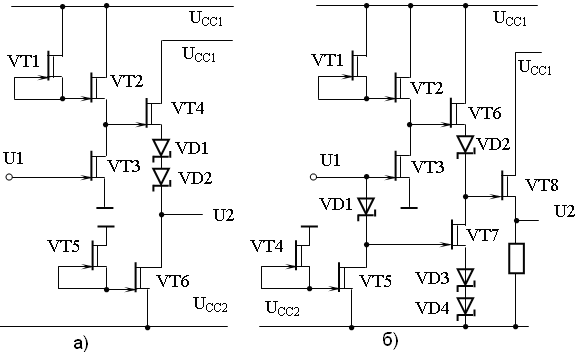

Логические элементы. Логические элементы и выходные каскады, которые лежат в основе построения элементов типа ЛР, триггеров и регистров показаны на рисунке 8.2.

а − ЛР1, ЛР2 ТТ1, ИР1; б − ИР2

Рисунок 8.2 – Логический элемент и выходной каскад ИС 6500

Простейший логический элемент выполнен на основе инвертора на транзисторе VT1 и истоковом повторителе на транзисторе VT4, в истоке которого стоят два последовательно включенных диода, понижающих уровень лог. 1.

Основой

второго логического элемента является

фазорасщепляющий каскад на VT3

и сложный истоковый повторитель на VT6

и VT7,

работающий на простой истоковый

повторитель на VT8.

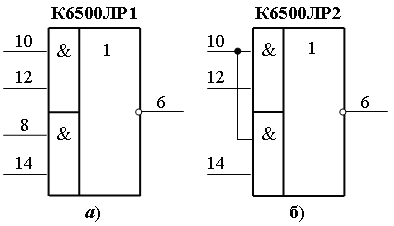

Условные графические обозначения

четырехвходового 2И-ИЛИ-НЕ ИС К6500ЛР1 и

трехвходового ЛЭ 2И-ИЛИ-НЕ ИС К6500ЛР2

приведены на рисунке 8.3. Микросхема

К6500 ЛР1 реализует функцию

![]() ,

где a,

b,

c,

d

– входные переменные. В зависимости от

входных аргументов микросхема может

реализовать разнообразные функции,

включая

,

где a,

b,

c,

d

– входные переменные. В зависимости от

входных аргументов микросхема может

реализовать разнообразные функции,

включая

![]() ,

,![]() ,

равнозначности и неравнозначности.

Задержка распространения сигнала 0,42

нс,

потребляемая мощность – 0,55 Вт.

Микросхема К6500 ЛР2 реализует функцию

,

равнозначности и неравнозначности.

Задержка распространения сигнала 0,42

нс,

потребляемая мощность – 0,55 Вт.

Микросхема К6500 ЛР2 реализует функцию

![]() .

Ее функциональные возможности несколько

меньше, чем у ЛР1.

.

Ее функциональные возможности несколько

меньше, чем у ЛР1.

а −ИС К6500ЛР1; б −К6500ЛР2

Рисунок 8.3 – Условное графическое обозначение

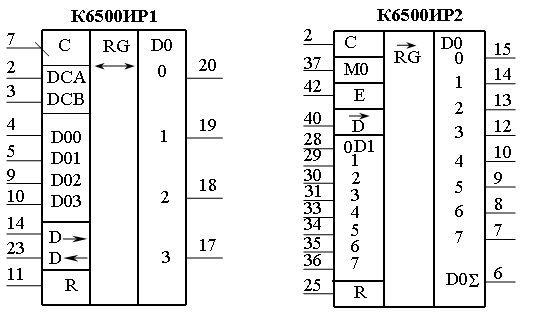

Регистры. Условное графическое обозначение и функциональная схема универсального сдвигового регистра К6500 ИР1 приведены на рисунке 8.4. Регистр имеет следующие режимы работы: сдвиг вправо (в сторону старших разрядов); сдвиг влево (в сторону младших разрядов); параллельная загрузка; режим хранения информации; установка низкого напряжения на выходах (сброс).

При установке микросхемы необходимо подключать сопротивление нагрузки к выводам 18 и 19 со значением 50 Ом, а к выводам 17 и 20–25 Ом. Тактирование (сдвиг) информации происходит по спаду синхронизирующего импульса на входе С.

Восьмиразрядный сдвиговый регистр (ИС К6500ИР2 – рисунок 8.4) может работать в режиме последовательной записи информации, синхронизированной по срезу тактового сигнала, имеет режимы сброса и установки, а также обеспечивает режим циклирования (кольцевого сдвига).

Микросхема имеет выход полусумматора, позволяющий формировать псевдослучайную последовательность длиной 27 – 1. Микросхема может управляться от ТТЛШ ИС, для этого значения напряжений логических уровней по входам 25, 28 – 31, 33 – 37 соответствуют ТТЛ и ТТЛШ.

Рисунок 8.4 −Условное графическое обозначение ИС

Счетчики. В серии ИС 6500 выпускаются два двоичных счетчика: ИЕ2 и ИЕ3. Микросхема 6500 ИЕ2 - четырехразрядный синхронный двоичный счетчик имеет следующие основные режимы работы: преобразование времени в цифровой код (ПВК), преобразование длительности в цифровой код (ПДК), деление частоты с коэффициентами 2, 4, 8, 16.

Задержка распространения сигнала не более 1,5 нс.

Микросхема ИС 6500ИЕ3 – восьмиразрядный двоичный счетчик, который может быть использован в качестве счетчика, делителя и преобразователя, длительность – код.