- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

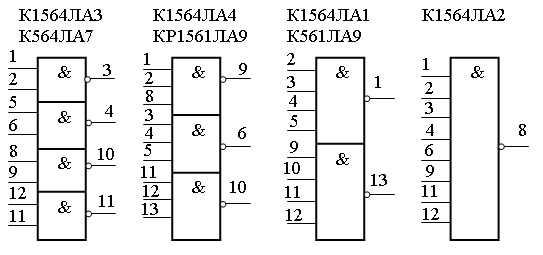

6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

В

состав КМОП ИС входят простейшие ЛЭ,

реализующие функции И-НЕ (ИС типа ЛА),

ИЛИ-НЕ (ИС типа ЛЕ), И (ИС типа ЛИ), НЕ (ИС

типа ЛН), комбинированные (ИС типа ЛП,

ЛС), триггеры Шмитта (ИС типа ТЛ), ключи

(ИС типа КТ). Микросхемы типа И-НЕ являются

наиболее распространенными ЛЭ и

выпускаются в виде набора 2-3-4-8 -входовых

ячеек в корпусе одной микросхемы. На

рисунке 6.7 приведены условные изображения

микросхем такого типа. Микросхемы типа

ЛА реализуют функцию m

И-НЕ, где m

– количество входов. Поскольку в ИС

типа ЛА необходимо последовательное

соединение МОП-транзисторов, выходные

напряжения

![]() ,

в условиях номинальной нагрузки и

наличия помех, имеют несколько отличные

значения выходных уровней от простейшего

МОП-инвертора (отличия выражаются в

более высоком уровне

,

в условиях номинальной нагрузки и

наличия помех, имеют несколько отличные

значения выходных уровней от простейшего

МОП-инвертора (отличия выражаются в

более высоком уровне

![]() ,

и более низком уровне

,

и более низком уровне

![]() ).

).

Рисунок 6.7 – Микросхемы типа К1564ЛА

Для

того чтобы при последовательном

соединении m

транзисторов напряжение

![]() не превышало допустимого уровня, ширина

каналов этих транзисторов увеличена в

m

раз. МОП-транзисторы с большей шириной

канала имеют более высокую крутизну

характеристик и обеспечивают меньшее

сопротивление открытого канала.

Логические элементы И-НЕ с открытым

стоком. Микросхема 564ЛА10 имеет особенность,

состоящую в том, что на ее выходе включен

не КМОП-ннвертор, а МОП-транзистор с

каналом п-типа, сток которого соединен

с ЛЭ (рисунок 6.8 ). Эта логическая схема

называется «с открытым стоком» (по

аналогии с ТТЛ ИС с открытым коллектором).

Она может использоваться для подключения

любой нагрузки между выходом и

положительным источником питания с

номинальным током 16 – 34 мА при Un = 5

– 10 В (например, элементов индикации и

др.). Выходной транзистор открыт только

при высоком напряжении на его затворе,

т.е. когда на вход ЛЭ И-НЕ поступят две

лог. 1.

не превышало допустимого уровня, ширина

каналов этих транзисторов увеличена в

m

раз. МОП-транзисторы с большей шириной

канала имеют более высокую крутизну

характеристик и обеспечивают меньшее

сопротивление открытого канала.

Логические элементы И-НЕ с открытым

стоком. Микросхема 564ЛА10 имеет особенность,

состоящую в том, что на ее выходе включен

не КМОП-ннвертор, а МОП-транзистор с

каналом п-типа, сток которого соединен

с ЛЭ (рисунок 6.8 ). Эта логическая схема

называется «с открытым стоком» (по

аналогии с ТТЛ ИС с открытым коллектором).

Она может использоваться для подключения

любой нагрузки между выходом и

положительным источником питания с

номинальным током 16 – 34 мА при Un = 5

– 10 В (например, элементов индикации и

др.). Выходной транзистор открыт только

при высоком напряжении на его затворе,

т.е. когда на вход ЛЭ И-НЕ поступят две

лог. 1.

а − функциональная схема; б − условное изображение

Рисунок 6.8 – Микросхема 564ЛА10

В

других случаях выходной транзистор

заперт, что соответствует высокоимпедансному

состоянию Z. Следовательно, на его выходе

можно применять монтажную логику.

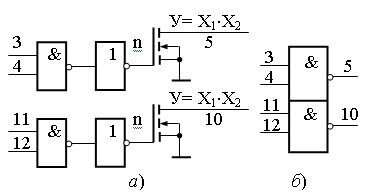

Микросхемы типа ИЛИ-НЕ представлены

2-3-4-входовыми ЛЭ типа ЛЕ (рисунок 6.9). Они

выполняют логическую функцию m ИЛИ-НЕ,

где m

– количество входов. Этот тип микросхем

также имеет более высокий уровень

![]() и более низкий уровень

и более низкий уровень

![]() ,

по сравнению с простейшими КМОП-

инверторами. Чтобы величина

,

по сравнению с простейшими КМОП-

инверторами. Чтобы величина

![]() не была ниже предельного уровня, ширина

каналов МОП-транзисторов с каналом

р-типа больше в m

раз, чем у МОП-транзисторов с каналом

n-типа.

Микросхемы типа ЛИ являются неинвертирующим

ЛЭ.

не была ниже предельного уровня, ширина

каналов МОП-транзисторов с каналом

р-типа больше в m

раз, чем у МОП-транзисторов с каналом

n-типа.

Микросхемы типа ЛИ являются неинвертирующим

ЛЭ.

Рисунок 6.9 − Микросхемы типа К561ЛЕ

В

качестве примера на рисунке 6.9 показана

микросхема 1564ЛИ1 (КР1561ЛИ2), содержащая

4 ЛЭ 2И. Прямой выходной сигнал получают

путем дополнительного инвертирования

выходного сигнала элемента 2И-НЕ.

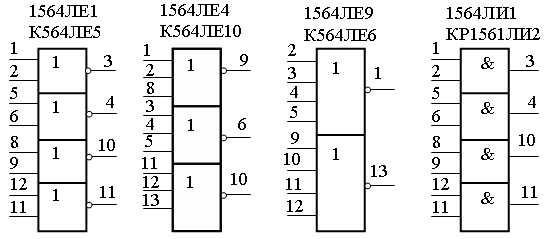

Микросхемы типа ЛН являются либо

инверторами, либо повторителями входного

сигнала и могут иметь дополнительные

управляющие входы. Микросхема 564ЛН2

содержит 6 буферных инверторов (рисунок

6.10, а). Для микросхемы необходимо только

одно напряжение питания, поэтому она

используется, как транслятор логических

уровней от КМОП к ТТЛ. Если на вывод 14

подать напряжение питания 5 В, то можно

передавать уровни от КМОП к ТТЛ, причем

нагрузочная способность инвертора –

2 ТТЛ входа (т.е.

![]()

3,2 мА при выходном напряжении низкого

уровня не менее 0,4 В). Время задержки

распространения не более 80 нс.

3,2 мА при выходном напряжении низкого

уровня не менее 0,4 В). Время задержки

распространения не более 80 нс.

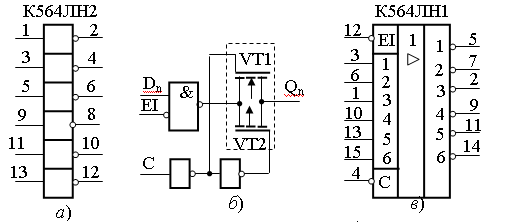

Микросхема 564ЛН1 содержит шесть стробируемых инверторов (рисунок 6.10, в). Каждый инвертор (точнее, двухвходовой элемент ИЛИ-НЕ) имеет вход Dn и выход Qn (рисунок 6.10, б). Кроме того, на вторые входы всех шести инверторов от общего выхода EI (разрешение по входу) подается разрешающий сигнал с активным низким уровнем. Если Е1 = 1, то входы Dn запрещаются, а все выходы Qn имеют низкий уровень. Второй общий вход управления ЕО (разрешение по выходу) при высоком входном уровне переводит все выходы в состояние Z (выходное сопротивление более 10 МОм).

Рисунок 6.10 – Условное графическое изображение: а − К564ЛН2; в − К564ЛН1; б − принципиальная схема одного ЛЭ

Третье состояние упрощает работу выходов на шину данных. Нагрузочная способность каждого инвертора – 2 ТТЛ входа. Напряжение питания микросхем от 5 до 15 В. Максимальное быстродействие обеспечивается при Un = 15 В: время задержки распространения составляет 65 нс, время перехода от Z-состояния к высокому выходному уровню 40 нс. При напряжении питания Un = 5 В все переходные процессы затягиваются в 3 раза.