- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

6.3 Буферный каскад

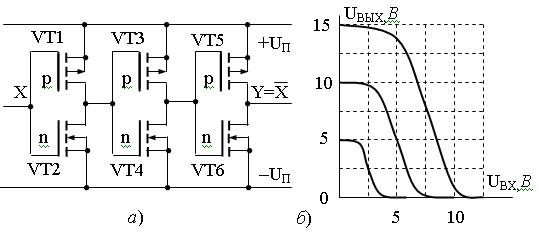

Путем подключения к выходу инвертора последовательно включенных одного или двух инверторов (буферов) можно улучшить переключательные свойства КМОП (рисунок 6.2, а).

В микросхемах с буферными выходными каскадами, транзисторы VT1 и VT2, выполняющие логические функции – маломощные, а выходные транзисторы обладают повышенной мощностью.

Рисунок 6.2 – Принципиальная схема инвертора КМОП:

а − с буферным выходом; б − передаточные характеристики инвертора

Повышение крутизны переходного участка передаточной характеристики обеспечивается за счет значительного усиления сигналов. Большое усиление позволяет формировать импульсы с крутыми фронтами независимо от формы входных импульсов, чем исключается постепенное ухудшение импульсных характеристик системы сигналами с пологими фронтами. Особенность идеальных передаточных характеристик КМОП-структур – это симметричность относительно точки переключения схемы из одного логического состояния в другое, причем центр симметрии лежит на уровне 0,5 UП (рисунок 6.2, б). Это указывает на высокую помехозащищенность схемы – до 45% UП. Сопротивление каналов КМОП-транзисторов у типовых микросхем: (0,75 – 2,5) кОм для маломощных транзисторов и (0,5 – 1,5 ) кОМ – для буферных каскадов. Поскольку выходные сопротивления инверторов КМОП большие, то в схему не вводят токоограничивающие резисторы.

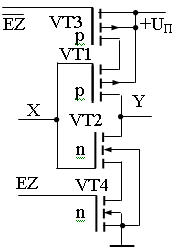

Инверторы КМОП с тремя выходными состояниями.

Такой

инвертор можно получить, если

последовательно с транзисторами логики

включить дополнительные ключевые

транзисторы VT3,

VT4

(рисунок 6.3). С помощью этих транзисторов

можно отключать транзисторы ключа VT1

и VT2

от источника питания или от общей шины

(земли). При высоком напряжении на входе

![]() транзистор р-типа

VT3

заперт и оба транзистора VT1

и VT2

отключены от источника питания. Каналы

этих транзисторов оказываются в

непроводящем состоянии, а выход – в

состоянии Z.

При

транзистор р-типа

VT3

заперт и оба транзистора VT1

и VT2

отключены от источника питания. Каналы

этих транзисторов оказываются в

непроводящем состоянии, а выход – в

состоянии Z.

При

![]() = 0 транзистор VT3

подключает транзисторы логики к источнику

питания (на входе EZ

должен быть высокий уровень напряжения)

и инвертор переходит в обычный режим

работы. Управление третьим состоянием

можно осуществлять по входу EZ.

На входе

устанавливается лог.0,

при EZ

= 1 транзистор VT4

открыт и ключ VT1,

VT2

находится в рабочем состоянии. При EZ

= 0 транзистор VT4

запирается и выход отключается от земли

(переводится в третье состояние).

= 0 транзистор VT3

подключает транзисторы логики к источнику

питания (на входе EZ

должен быть высокий уровень напряжения)

и инвертор переходит в обычный режим

работы. Управление третьим состоянием

можно осуществлять по входу EZ.

На входе

устанавливается лог.0,

при EZ

= 1 транзистор VT4

открыт и ключ VT1,

VT2

находится в рабочем состоянии. При EZ

= 0 транзистор VT4

запирается и выход отключается от земли

(переводится в третье состояние).

Рисунок 6.3 – Схема инвертора

КМОП-инверторы с тремя состояниями выхода используются в качестве самостоятельных элементов или в составе некоторых типов логических элементов и более сложных устройств.

6.4 Основные характеристики инвертора

Энергитические характеристики. Одной из основных характеристик КМОП ИС является мощность потребления. Суммарная мощность потребления складывается из статической и динамической. Статическая мощность потребления:

PC = (IC + IУ) UП,

где UП – напряжение питания; IС – сквозной ток транзисторов; IУ – токи утечки обратно смещенных p-n – переходов.

Динамическая составляющая мощности потребления присуща микросхемам при функционировании на рабочей частоте F и определяется тремя факторами: емкостью нагрузки СН, внутренней емкостью схемы СВН. и токами переключения (сквозными токами):

PД = СД U 2П F + Σ (CН U 2П FО),

где СД – средняя эффективная емкость, устанавливаемая для расчета мощности потребления суммарной нагрузки, обусловленной внутренними емкостями и переходными токами переключения, F0 – частота переключения каждого выхода МСХ (частота сигналов на выходе может отличаться от входной для схем отличных от инвертора).

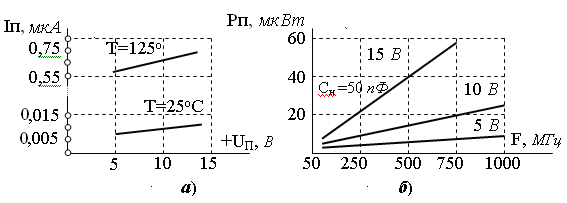

В статическом состоянии один из транзисторов КМОП-структуры, р-или n-МОП, закрыт и теоретически существует непроводящий канал между питанием и «землей». Однако наблюдается тепловое движение неосновных носителей заряда через обратно смещенные переходы, которое создает очень малый ток утечки между шиной питания и «землей». На статический ток потребления оказывают влияние три фактора: температура, сложность схемотехники, напряжение питания (рисунок 6.4, а).

Динамическая составляющая мощности потребления растет с увеличением частоты в основном за счет перезарядки емкости нагрузки. С ростом частоты увеличивается влияние внутренних паразитных емкостей схемы. Токи переключения или сквозные токи возникают в период перехода микросхем из одного логического состояния в другое, когда оба транзистора выходного каскада открыты, т.е. во время нарастания и спада импульса. Среднее значение этих токов растет линейно с увеличением частоты переключения. Типовая зависимость динамической мощности потребления от частоты переключения при разных напряжениях питания и емкости нагрузки СН = 50 пФ для ИС К564ЛЕ5 приведена на рисунке 6.4, б.

Рисунок 6.4 – Типовые зависимости для ИС К564ЛЕ5:

а – статического тока потребления от напряжения питания и температуры; б − динамической мощности потребления от частоты переключения

С увеличением тактовой частоты до предельных значений резко возрастает потребляемая мощность, что приводит к увеличению выделяемого тепла и ухудшению условий эксплуатации. Быстродействие схемы ограничивается временами заряда (разряда) входных емкостей Свх логического элемента, а также временами нарастания (спада) напряжения на емкости нагрузки. Значение емкости одного входного элемента обычно 515 пФ. Следовательно, длительность фронта и среза входного импульса ЛЭ: t0,1 = t1,0 = 2,2 Rpk Cвх = 2,2 Rnk Свх,

где. Rpk, Rnk – сопротивления каналов выходных транзисторов типа р и n, которые полагаем равными.

При Rk = 2.5 кОм длительность нарастания и спада будет, примерно 25-75 нс. Длительность фронтов выходного сигнала будет определяться емкостью нагрузки:

t0,1 = t1,0 = 2,2 Rрk Cн = 2,2 Rnk Сн,

Кроме

того, временные параметры ИС КМОП

характеризуются задержкой распространения

сигнала от входа к выходу. При включении,

когда входной сигнал приводит к изменению

состояния на выходе с 0/1, задержка

появления сигнала

![]() .

При обратном переключении 1/0 задержка

распространения

.

При обратном переключении 1/0 задержка

распространения

![]() .

Задержки

и

.

Задержки

и

![]() в общем случае даже для ИС одного типа

оказываются различными в виду различия

параметров открытых р-

и n-

канальных транзисторов. При напряжении

питания UП

= 5 В

и СН

= 15 пФ

задержка распространения у простых

инверторов при включении и выключении

одинакова и равна примерно 60 нс.

При СН

= 100 пФ

задержка распространения при включении

возрастает до 200 нс,

а при выключении – 300 нс.

в общем случае даже для ИС одного типа

оказываются различными в виду различия

параметров открытых р-

и n-

канальных транзисторов. При напряжении

питания UП

= 5 В

и СН

= 15 пФ

задержка распространения у простых

инверторов при включении и выключении

одинакова и равна примерно 60 нс.

При СН

= 100 пФ

задержка распространения при включении

возрастает до 200 нс,

а при выключении – 300 нс.

Помехоустойчивость для высокого уровня сигнала и низкого примерно одинакова и составляет почти 50% от Uп. Пропорциональность сохраняется для напряжений питания 5 – 15 В.

Температурная стабильность ИС КМОП очень высокая колебания температуры в диапазоне от – 550 до + 1250С весьма слабо влияют на передаточные характеристики. В подобных же условиях пороговое напряжение биполярных приборов может измениться на 40%. Однако, с точки зрения надежности следует ограничивать верхний диапазон температуры + 650С.

Входной ток КМОП ИС весьма мал. Основное влияние на входной ток оказывает диодная схема защиты, стоящая на входе ИС. Максимальное значение входного тока для всех интегральных микросхем не превышает 0.05 мкА при температуре t = + 250 С и 1 мкА при t = + 1250 С.

Выходной

ток

характеризует нагрузочную способность

ИС по постоянному току. Ток

![]() представляет собой ток, входящий в ИС

при открытом n-

канальном и закрытом р-канальном

транзисторе выходного каскада.

представляет собой ток, входящий в ИС

при открытом n-

канальном и закрытом р-канальном

транзисторе выходного каскада.

![]() – ток выходящий из ИС при закрытом

n-канальном

и открытом р-канальном

транзисторе выходного каскада. Для раз

личных типов ИС токи

– ток выходящий из ИС при закрытом

n-канальном

и открытом р-канальном

транзисторе выходного каскада. Для раз

личных типов ИС токи

![]() и

и

![]() могут отличаться в десятки раз из-за

сильного различия каналов транзисторов

выходного каскада. Для микросхем общего

назначения выходные токи I0вых

и I1вых

не превышают 1 мА.

Лишь инверторы с повышенной нагрузочной

способностью имеют величину выходных

токов несколько мА.

Например, ИС 564ЛН2 имеет I0вых

= 1,25 мА

и I1вых

= 8 мА.

могут отличаться в десятки раз из-за

сильного различия каналов транзисторов

выходного каскада. Для микросхем общего

назначения выходные токи I0вых

и I1вых

не превышают 1 мА.

Лишь инверторы с повышенной нагрузочной

способностью имеют величину выходных

токов несколько мА.

Например, ИС 564ЛН2 имеет I0вых

= 1,25 мА

и I1вых

= 8 мА.