- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

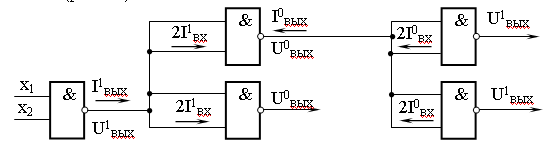

4.4 Разветвление и объединение выходов и входов

логических схем

Для обеспечения работоспособности логических микросхем различных серий друг от друга при условии сохранения параметров MCX, оговоренных в технических условиях на них, следует выполнять требования по уровням выходных напряжений и токов при формирования уровней лог.0 и лог.1, а также по значения суммарной емкостной нагрузки.

Выходные напряжения ЛЭ – источников сигналов в открытом и закрытом состоянии при определенной нагрузке должны соответствовать входным пороговым напряжениям закрытого и открытого состояния ЛЭ – нагрузки с учетом величины напряжения помехи:

![]()

где U0вых, U1вых – выходные напряжения ЛЭ в открытом и закрытом состоянии; U0пор, U1пор – порог отпирания и запирания ЛЭ соответственно; U0n, U1n – допустимое напряжение помехи на отпирание и запирание ЛЭ нагрузки.

Уровень помехи, как правило, заранее неизвестен и может быть определен лишь на этапе экспериментального макетирования.Значение суммарных токов всех ЛЭ – нагрузок не должно превышать значений выходных токов MCX – источника в открытом и закрытом состояниях (рисунок 4.9):

Рисунок 4.9 – Разветвление выходов ЛЭ

![]()

где I0вых, I1вых – соответственно выходные токи в открытом и закрытом состоянии; I0вх, I1вх – входные токи для одного элемента нагрузки при U0вх, U1вх соответственно; Kраз – число логических входов, подключаемых к выходу MCX – источника.

Суммарная емкость, подключаемая к источнику сигнала, не должна превышать емкость ЛЭ – источника Cн, при которой гарантируются временные параметры, т.е.

![]()

где

![]() – максимальная емкость входа ЛЭ (примерно

3пФ);

– максимальная емкость входа ЛЭ (примерно

3пФ);

![]() –

емкость монтажных соединений одного

входа нагрузки.

–

емкость монтажных соединений одного

входа нагрузки.

Коэффициент разветвления по выходу определяется следующими выражениями:

K0раз = I0вых / I0вх, н ; K1раз = I1вых / I1вх, н ; Kс = (Сн –См ) / Свх, н ,

где K0раз, K1раз – нагрузочная способность ЛЭ – источника сигнала в открытом состоянии, соответственно; Kс – емкостная нагрузочная способность ЛЭ источника. Наименьший из вычисленных коэффициентов принимается за Kраз для нагружаемой MCX. Если требуется определить допустимое значение единичных нагрузок ИС других серий, расчет ведут аналогичным образом, подставляя значения входных токов I0вх I1вх соответствующей серии. Ниже приводятся таблицы входных и выходных токов различных серий (таблица 4.1). Отметим, что токи I0вых и I1вых в таблице имеют те значения, при которых ТУ гарантируются значения логических уровней U0вых. Превышение выходных токов допустимых значений приводит к изменению U0вых ,U1вых, что в целом снижается помехоустойчивость ИС.

При использовании ИС различных серий в одном устройстве следует учитывать взаимную нагрузочную способность (таблица 4.2). Все серии ИС содержат, кроме элементов со стандартным выходом, элементы с повышенной нагрузочной способностью (буферы). В таблице первое число указывает нагрузочную способность для элемента со стандартным выходом, а второе – для буфера Шоттки.

Таблица 4.1 − Входные и выходные токи ЛЭ различных серий

Серия |

I0вх, мА |

I1вх, мА |

I0вых, мА |

I1вых, мА |

155 |

– 1,6 |

0,04 |

16 |

– 0,4 |

531 |

– 2 |

0,05 |

20 |

– 1 |

555 |

– 0,36 |

0,02 |

8 |

– 0,4 |

1533 |

– 0,2 |

0,02 |

4 |

– 0,4 |

При объединении выходов с открытым коллектором необходимо обеспечить логические уровни выходных напряжений, соответствующие уровням устройств со сложным выходом: U1вых 2,4 В и U0вых 0,4 В. Для этого надо рассчитать величину нагрузочного сопротивления Rн при выбранном Uн, обеспечить заданные уровни лог.0 и лог.1 при данной конфигурации схемы и используемых серий ЛЭ.

Таблица 4.2 −Нагрузочную способность ИС различных серий

Серии ИС |

Вход ИС серий |

||||||

SN 74 |

SN 74LS |

SN 74S |

SN74ALS |

SN 74AS |

SN 74F |

||

155 |

SN74

|

10/30 |

40/120 |

8/24 |

80/24

|

30/240 |

26/80 |

555 |

SN 74LS |

5/15 |

20/60 |

4/12 |

40/120 |

40/120 |

13/40 |

531 |

SN74S

|

12/30 |

50/120 |

10/24 |

100/240 |

100/240 |

30/100

|

КР 1533 |

SN74ALS

|

5/15 |

20/60 |

4/12 |

40/120 |

40/120 |

13/40 |

|

SN 74AS |

12/35 |

50/150 |

10/30 |

100/300 |

100/300 |

30/80 |

КР 1531 |

SN 74F |

12/40 |

50/150 |

10/25 |

100/250 |

100/250 |

30/100 |

При выборе сопротивления нагрузки, следует учитывать, что максимальное быстродействие обеспечивается при минимальном сопротивлении, однако при этом возрастает потребление мощности. При увеличении RH увеличивается время заряда паразитных емкостей.