- •Основы теории цифровых устройств и цифровые интегральные схемы

- •Содержание

- •1 Основы теории цифровых устройств…………………….…11

- •4 Цифровые интегральные микросхемы….…………….……63

- •22 Жидкокристаллические знакосинтезирующие

- •Сокращения и мнемонические обозначения

- •Предисловие

- •1 Основы теории цифровых устройств

- •1.1 Классификация

- •1.2 Система обозначений ис

- •1.3 Основные характеристики логических элементов

- •2 Арифметические оcновы цифровых устройств

- •2.1 Позиционная система счисления

- •Метод деления / умножения

- •Метод вычитания

- •2.3 Формы представления чисел в цифровых устройствах

- •Представление чисел с плавающей точкой

- •2.4 Двоичная арифметика

- •Сложение и вычитание двоично-десятичных чисел

- •2.5 Кодирование отрицательных чисел

- •2.6 Умножение и деление двоичных чисел

- •3 Логические основы цифровых устройств

- •3.2 Основные законы алгебры логики

- •3.3 Элементарные логические функции

- •3.4 Представление переключательных функций

- •3.5 Функционально полные системы переключательных

- •3.6 Минимизация переключательных функций

- •3.6.1 Минимизация логических функций методом Квайна

- •3.6.2 Минимизация логических функций с помощью карт Карно

- •4 Цифровые интегральные микросхемы

- •4.1 Базовый логический элемент ттл

- •4.2 Логические элементы или-не

- •4.3 Логические элементы с открытым коллектором и

- •4.4 Разветвление и объединение выходов и входов

- •4.5 Триггер Шмитта

- •4.6 Рекомендации по применению логических элементов ттл

- •5 Микросхемы ттл с транзисторами шоттки

- •5.1 Введение

- •5.2 Транзисторы с диодами Шоттки

- •5.3 Базовый логический элемент ис к533

- •5.4 Быстродействующие ттлш ис к530

- •5.5 Базовый логический элемент ис к1533

- •6 Цифровые микросхемы с кмоп-транзисторами

- •6.1 Общие сведения

- •6.2 Инвертор кмоп

- •А − упрощенная схема; б − полная схема с защитными и паразитными диодами

- •6.3 Буферный каскад

- •6.4 Основные характеристики инвертора

- •6.5 Тактируемый двунаправленный ключ

- •6.6 Логические элементы кмоп типа и-не, или-не

- •6.7 Разновидности простых лэ кмоп На основе базовых лэ спроектированы все микросхемы, входящие в состав серий кмоп: 561, к561, 564, 564в, к564, н564, кр1561, 1564.

- •6.8 Рекомендации по применению ис кмоп

- •7 Интегральные схемы эсл

- •7.1 Общие сведения

- •7.2 Базовый логический элемент ис к1500

- •7.3 Особенности применения эсл

- •8 Интегральные схемы на основе арсенида галия

- •8.1 Общие сведения

- •8.2 Базовый лэ сверхбыстродействующих ис к6500

- •8.3 Логические элементы, регистры, счетчики

- •9 Шифраторы

- •10 Дешифраторы

- •10.1 Линейные дешифраторы

- •10.2 Ступенчатые дешифраторы

- •Реализация функции

- •10.3 Дешифраторы-демультиплексоры ттл

- •11 Мультиплексоры

- •11.1 Назначение и принцип работы

- •11.2 Мультиплексоры ттл

- •11.3 Наращивание разрядности мультиплексоров

- •11.5 Синтез комбинационных схем на мультиплексорах

- •12 Арифметические устройства

- •12.1 Комбинационные двоичные сумматоры

- •13 Схемы сравнения цифровых кодов

- •13.1 Общие положения

- •13.2 Цифровые компараторы и их применение

- •Компаратора

- •14 Преобразователи кодов

- •14.2 Преобразователи кода для неполных матричных

- •15 Триггеры

- •15.1 Общие положения

- •15.2 Классификация триггеров

- •15.3 Триггерная ячейка r-s -типа

- •15.4 Асинхронные rs-триггеры на логических элементах и-не

- •15.5 Синхронные одноступенчатые триггеры

- •Микросхема к564 тм3

- •15.8 Счетные триггеры

- •Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных т-триггеров и универсальных jk - триггеров.

- •15.9 Универсальные jk-триггеры

- •А − jk − триггера; б − функциональное обозначение

- •16 Регистры

- •16.1 Параллельные регистры

- •16.2 Сдвигающие регистры

- •16.2.1 Последовательный регистр сдвига вправо

- •Регистра при сдвиге вправо

- •16.2.2 Реверсивный регистр

- •16.3 Кольцевые регистры-счетчики

- •16.3.1 Кольцевой регистр сдвига единицы

- •16.3.2 Кольцевой счетчик

- •17 Счетчики

- •17.1 Двоичные суммирующие счетчики с последовательным

- •17.3 Двоичные счетчики с параллельным переносом

- •17.4 Реверсивный двоичный счетчик

- •17.5 Десятичный счетчик

- •Счетчика

- •17.6 Типовые счетчики

- •17.6.2 Синхронные счетчики

- •17.6.3 Реверсивные счетчики

- •18 Программируемые делители

- •18.1 Программируемые делители с предварительной установкой

- •18.2 Программируемый делитель на к561ие15

- •19 Газоразрядные индикаторы

- •Напряжение зажигания, в…...............................170

- •20 Полупроводниковые индикаторы

- •20.1 Общие сведения

- •20.2 Управление единичными и шкальными индикаторами

- •А − ис155ид12; б − условное изображение

- •20.3 Одноразрядные знакосинтезирующие индикаторы

- •20.4 Полупроводниковые многоразрядные индикаторы

- •Индикаторов

- •20.4.1 Мультиплексная индикация

- •20.5 Матричные индикаторы

- •20.5.1 Управление матричными индикаторами Управление неполными матричными индикаторами

- •Управление матричными индикаторами

- •20.5.2 Блок формирования символов

- •21 Вакуумные люминцентные индикаторы

- •21.1 Введение

- •21.2 Одноразрядные вли

- •21.3 Многоразрядные индикаторы

- •Управление многоразрядными ивл

- •21.4 Шкальные индикаторы

- •21.5 Матричные индикаторы вли

- •22 Жидкокристаллические знакосинтезирующие индикаторы

- •22.1Общие сведения

- •22.2 Разновидности жки

- •Заключение

- •Библиографический список

- •Основы теории цифровых устройств и цифровые интегральные схемы

- •654007, Г. Новокузнецк, ул. Кирова, 42.

3.5 Функционально полные системы переключательных

функций

Система элементарных булевых функций φ 1, φ 2,…., φ m называется функционально полной, или базисом, если любую функцию алгебры логики можно представить в виде их суперпозиции функций. Имея логические элементы, осуществляющие операции f 0 – f 15 , можно выполнить любую сложную функцию. Однако условие наличия 16 различных типов логических элементов, каждый из которых реализует одну из 16 элементарных операций, является условием, достаточным для синтеза логического устройства любой сложности, но не необходимым, т.е. при синтезе можно ограничиваться меньшим набором элементарных функций, взятых из f 0 – f 15. Последовательно исключая из базиса избыточные функции, можно получить минимальный базис. Под минимальным базисом понимают такой набор функций, исключение из которого любой функций превращает этот набор в неполную систему функций.

Возможны различные базисы и минимальные базисы, различающиеся числом входящих в них функций и видом этих функций. Выбор того или иного базиса для синтеза логического устройства связан с тем, насколько просто, удобно и экономично технически выполнять узлы, реализующие элементарные функции, которые входят в выбранный базис, и в целом все логическое устройство.

Функционально полными системами являются базисы:

И, ИЛИ, НЕ – базис 1, И-НЕ – базис 4, ИЛИ, НЕ – базис 3,

И, НЕ – базис 2, ИЛИ-НЕ – базис 5, И-ИЛИ, НЕ – базис 6.

Базис И, ИЛИ, НЕ принято называть основным, так как любая сложная переключательная функция может быть записана в СДНФ или СКНФ. Базис И, ИЛИ, НЕ является избыточной системой, так как возможно исключение из него некоторых функций. Например, используя правило Де Моргана, можно исключить либо функцию И (получим базис 3), заменяя ее ИЛИ и НЕ, либо ИЛИ (получим базис 2), заменяя ее на И и НЕ.

Базисы И, НЕ и ИЛИ, НЕ называют универсальными. Эти базисы приобрели важное значение в связи с широким использованием интегральных логических элементов при построении логических устройств.

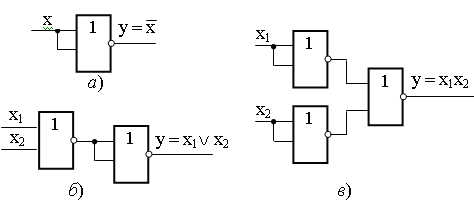

Структуры логических элементов НЕ, И, ИЛИ, состоящие из элементов Шеффера, приведены на рисунке 3.3.

Схема

отрицания

НЕ реализована

на использовании следующего соотношения:

![]() .

.

Схема логического умножения использует принцип двойной инверсии:

![]() .

.

Схема логического сложения двух двух сигналов базируется на использовании закона отрицания:

![]() .

.

а − элемент НЕ ; б − элемент И; в − элемент ИЛИ

Рисунок 3.3 − Реализация схем

Cтруктуры

логических элементов НЕ, ИЛИ, И, выполненные

на логических элементах ИЛИ – НЕ

приведены на рисунке 3.4. Схема логической

инверсии

(рисунок 3.4, а)

−![]() ,

,

логического

сложения (рисунок

3.4, б)

–

![]() ,

,

логического

умножения

(рисунок 3.4, в)

–![]() .

.

Связующим звеном между реальным элементом и его переключательной функцией служит полярность логики. Различают положительную и отрицательную логику. При положительной логике в качестве логической единицы принят высокий уровень сигнала, при отрицательной логике – низкий уровень сигнала.

а − элемент НЕ; б − элемент ИЛИ; в − элемент И

Рисунок 3.4 − Реализация схем

Из принципа дуальности следует, что одно и то же логическое выражение может быть представлено двояко, например,

y

= x 1 x

2 и

![]() .

.

Это значит, что один и тот же элемент будет реализовывать с точки зрения положительной логики функцию конъюнкции, а с точки зрения отрицательой логики – дизъюнкцию.

В дальнейшем в качестве единицы будет принят высокий уровень напряжения (положительная логика).