- •Микропроцессор, основные определения и современные технологии

- •Мп выпускаются в 3 видах:

- •3. Информационные микропроцессорные системы

- •4. Scada – системы

- •8. Микропроцессорные комплекты общего назначения

- •9. Микропроцессоры на основе микропроцессорных секций

- •10. Регистровая архитектура

- •Для использования языков высокого уровня требуется 2 функции:

- •Стек в мп-ре может быть реализован 3 способами:

- •13 Архитектура мп, ориентированная на память

- •14 Язык ассемблера для программирования мпс

- •15 Структура программируемого параллельного адаптера (ппа)

- •17 Назначение сигналов ппа

- •18 Режимы работы ппа

- •19 Структура управляющего слова ппа

- •20 Принцип программирования ппа

- •21. Структурная схема программируемого интегрального таймера (пит)

- •22. Управляющее слово пит

- •24. Процедура инициализации пит

- •Задача: запрограммировать пит

- •26. Режим 1 пит, назначение, примеры применения

- •27. Режим 2 пит, назначение, примеры применения

- •28. Режим 3 пит, назначение, примеры применения

- •29. Принцип формирования шим на основе пит

- •Обращение к ячейкам памяти данных возможно двумя способами:

- •33 Способы адресации в mcs-51

- •34. Группа команд пересылки данных mcs-51

- •Группа команда сдвига:

- •37. Группа команд передачи управления mcs-51

- •38. Группа команд битового процессора mcs-51

- •Структурная схема:

- •Реализация на основе цпоас цф первого порядка ких.

- •Реализация на основе цпоас цф первого порядка бих.

- •43. Реализация на основе цпоас цф второго порядка с ких

- •44. Реализация на основе цпоас цф второго порядка с бих

- •45. Самообучающаяся микропроцессорная система

- •46. Программно-управляемая передача данных (управление по командам (int, out, вв/выв))

- •47. Одношинная (Принстонская) архитектура

- •49. Двухшинная (Гарвардская) архитектура

- •50. Каноническая форма цифрового фильтра

- •Алгоритм реализации:

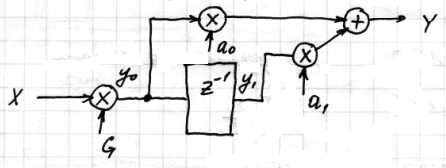

Реализация на основе цпоас цф первого порядка ких.

КИХ – Фильтр с конечной импульсной характеристикой.

Для реализации цифровой обработки сигналов и систем управления в реальном времени применяются цифровые процессоры обработки сигналов (ЦПОС).

Фильтр – это устройство, которое реализует функцию свертки входного сигнала с импульсной переходной характеристикой фильтра (это реакция объекта на воздействие дельта-функции (производная от единичной функции)).

Принцип работы фильтра:

Входной сигнал умножается на требуемый коэффициент передачи, далее поступает на последовательные задержки на 1 такт, в качестве которых в МП используются ячейки памяти. Количество этих ячеек памяти определяет порядок фильтра.

С выходов задержки сигналы поступают на сумматор B после умножения на постоянные коэффициенты b (коэффициенты БИХ-фильтра), а через другие множители значений сигналов умножаются на коэффициенты a (коэффициенты КИХ-фильтра), и выходной сигнал получается на сумматоре A.

Алгоритм: Uвых=Y0*A0+Y1*A1

Программа:

ADD U, Y0, R1, NOP;

ADD U, Y1, R2, NOP;

Если необходимо реализовать фильтр большего порядка, необходимо добавить задержку и коэффициенты находятся по специальным программам.

Реализация на основе цпоас цф первого порядка бих.

БИХ – Фильтр с бесконечной импульсной характеристикой.

Ограничения на устойчивость БИХ-фильтра: B=1-G

Чем ближе B к единице, тем больше постоянная времени: B->1; T->бесконечности (B<1)

Программа, реализующая БИХ-фильтр первого порядка: G=0.5, B=0.5

Алгоритм:

Y1=Y0; задержка на Т

Y0=Y1*B+X*G

Программа:

LDA Y1, Y0, R0, NOP; задержка на Т

ADD Y0, Y1, R0(*0.5), NOP; сумма Y1/2

ADD Y0, X, R1, NOP; сумма X/2

Если необходимо реализовать фильтр большего порядка, необходимо добавить задержку и коэффициенты находятся по специальным программам.

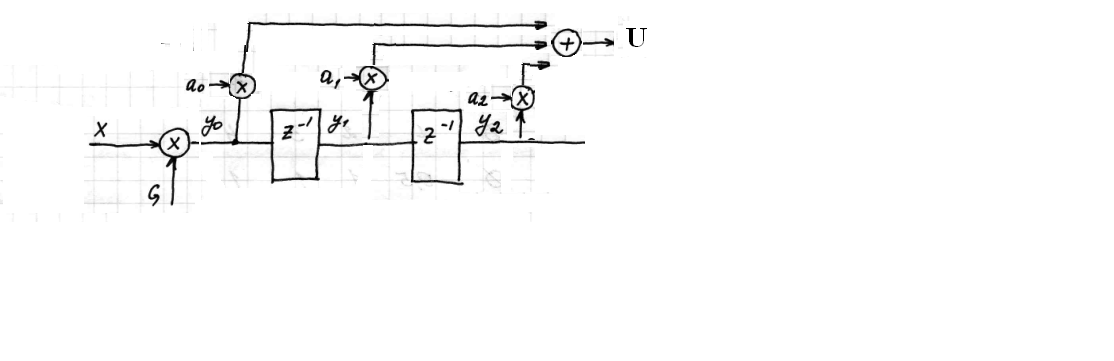

43. Реализация на основе цпоас цф второго порядка с ких

Для реализации цифровой обработки сигналов и систем управления в реальном времени применяются цифровые процессоры обработки сигналов (ЦПОС).

Фильтр – это устройство, которое реализует функцию свертки входного сигнала с импульсной переходной характеристикой фильтра (это реакция объекта на воздействие дельта-функции (производная от единичной функции)).

КИХ – Фильтр с конечной импульсной характеристикой.

Принцип работы фильтра:

Входной сигнал умножается на требуемый коэффициент передачи, далее поступает на последовательные задержки на 1 такт, в качестве которых в МП используются ячейки памяти. Количество этих ячеек памяти определяет порядок фильтра.

С выходов задержки сигналы поступают на сумматор B после умножения на постоянные коэффициенты b (коэффициенты БИХ-фильтра (Фильтр с бесконечной импульсной характеристикой)), а через другие множители значений сигналов умножаются на коэффициенты a (коэффициенты КИХ-фильтра), и выходной сигнал получается на сумматоре A.

Алгоритм: Uвых=Y0*A0+Y1*A1+ Y2*A2

Программа:

ADD U, Y0, R1, NOP;

ADD U, Y1, R2, NOP;

ADD U, Y2, R3, NOP;

Если необходимо реализовать фильтр большего порядка, необходимо добавить задержку и коэффициенты находятся по специальным программам.

Общий коэффициент передачи фильтра определяется коэффициентом G, хоть и он равен 4, переполнение разрядной сетки не происходит, т.к. входные значения X находятся в младших разрядах МП.

Для реализации фильтра более высокого порядка обычно принимают последовательное включение большого числа фильтров первого или второго порядка.