- •Математическое моделирование цифровых электронных устройств в сапр micro-cap 8.0

- •Математическое моделирование цифровых электронных устройств в сапр micro-cap 8.0

- •Содержание

- •Основные сведения о сапр Micro-Cap 8.0

- •1.1Возможности сапр Micro-Cap 8.0

- •1.2Особенности сапр Micro-Cap 8.0

- •1.3Назначение функциональных клавиш

- •Моделирование смешанных аналого-цифровых устройств

- •Основные понятия

- •Устройства интерфейса

- •Аналого-цифровой интерфейс

- •Цифро-аналоговый интерфейс

- •Модель вход/выход

- •Устройства питания

- •Генераторы цифровых сигналов

- •Цифровые компоненты

- •Триггеры

- •Прочие устройства

- •Функциональное описание цифровых устройств

- •Логические выражения

- •Задание задержек распространения

- •Контроль временных соотношений

- •Общие методические рекомендации по выполнению моделирования

- •Моделирование цифровых устройств

- •Лабораторная работа №1. Система схемотехнического моделирования электронных устройств Micro-Cap 8.0

- •Лабораторная работа №2. Временные параметры и характеристики цифровых микросхем

- •Лабораторная работа №3. Триггеры

- •Лабораторная работа №5. Сумматоры и вычитатели

- •Лабораторная работа №6. Счетчики

- •7.7 Лабораторная работа №7. Делители с произвольным постоянным коэффициентом деления

- •Лабораторная работа №8. Регистры

- •Список рекомендованной литературы

Аналого-цифровой интерфейс

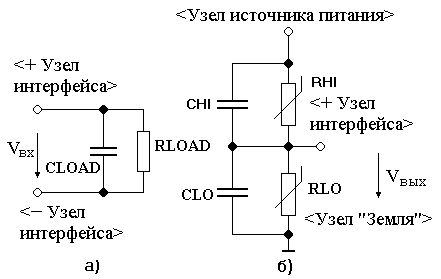

Аналого-цифровые интерфейсы предназначены для преобразования аналогового напряжения в логический уровень. Они имитируют входные каскады цифровых ИС. Их схема замещения показана на рисунке 2.3а.

Рисунок 2.3 — Аналого-цифровой (а) и цифро-аналоговый (б) интерфейсы

Формат схем:

Атрибут MODEL: <имя модели А/Ц>

Атрибут I/O MODEL: < имя модели вход/выход >

Модель аналого-цифрового интерфейса описывается предложением:

.MODEL <имя модели А/Ц> DOUTPUT [<параметры модели>]

Параметры модели аналого-цифрового интерфейса приведены в таблице 2.1.

Таблица 2.1 — Параметры аналого-цифрового интерфейса

Иденти- фикатор |

Параметр |

Значение по умолчанию |

Единица измерения |

RLOAD |

Сопротивление нагрузки |

1/GMIN |

Ом |

CLOAD |

Емкость нагрузки |

0 |

Ф |

SONAME |

Имя логического состояния "0" |

|

|

SOLVO |

Нижний уровень напряжения логического "0" |

|

В |

SOLHI |

Верхний уровень напряжения логического "0" |

|

В |

S1NAME |

Имя логического состояния "1" |

|

|

Продолжение таблицы 2.1

Иденти- фикатор |

Параметр |

Значение по умолчанию |

Единица измерения |

S1VLO |

Нижний уровень напряжения логической "1" |

|

В |

S1VHI |

Верхний уровень напряжения логической "1" |

|

В |

... |

... |

... |

... |

S19NAME |

Имя логического состояния "19" |

|

|

S19VLO |

Нижний уровень напряжения логического состояния "19" |

|

В |

S19VHI |

Верхний уровень напряжения логического состояния "19" |

|

В |

SXNAME |

Имя логического состояния, когда напряжение на узле интерфейса находится вне заданных границ |

|

|

Каждому i-му логическому состоянию соответствует определенный диапазон напряжений SiVLO...SiVHI. До тех пор пока входное напряжение интерфейса А/Ц Vвх не выходит за его границы, логическое состояние на выходе интерфейса А/Ц не изменяется. В противном случае входное напряжение будет сравниваться с пороговыми уровнями, начиная с SOVLO, пока не попадет в какой-нибудь интервал. Если оно не попадает ни в один интервал напряжений, логическому состоянию интерфейса А/Ц по умолчанию присваивается значение параметра SXNAME.

При взаимодействии с модулем логического моделирования программы МС8 имена логических состояний должны быть "0", "1", "X". "R", "F" или "Z" (однако состояние "Z" обычно не используется, так как состояние высокого импеданса не определяет уровень напряжения).

Моделирование входной цепи реального цифрового компонента с помощью линейной RC-цепи, как показано на рисунке 2.3а, не всегда обеспечивает достаточную точность расчетов. Поэтому пользователь должен иметь в своем распоряжении несколько моделей входных цепей логических компонентов, оформляя их в виде макромоделей. В качестве примера на рисунке 2.4 представлена нелинейная модель входной цепи ТТЛ — логики, к которой подключено стандартное устройство сопряжения типа Оххх.

Рисунок 2.4 — Нелинейная модель входной цепи цифрового компонента