- •Федеральное агентство по образованию

- •Пояснительная записка

- •Федеральное агентство по образованию

- •1 Литературный обзор

- •2 Разработка структурной схемы устройства функционального контроля восьмиразрядных микроконтроллеров

- •3 Разработка электрической схемы устройства функционального контроля восьмиразрядных микроконтроллеров

- •3.1 Разработка электрической схемы функционального контроля ис в сравнении с эталоном

- •3.2 Разработка электрической схемы, обеспечивающей прием данных из компьютера

- •3.2.1 Разработка электрической схемы для блока «ram 1»

- •3.2.2 Разработка электрической схемы для блока «ст 1»

- •3.2.3 Разработка электрической схемы для блока «ms 1»

- •3.2.4 Разработка электрической схемы для блоков «Буфер данных 1» и «Буфер данных 2»

- •3.2.5 Разработка электрической схемы для блока «Логика управления 1»

- •3.3 Разработка электрической схемы, обеспечивающей передачу данных в компьютер

- •3.3.1 Разработка электрических схем для блоков «ram 2», «ct 2», «ms 2», «Буфер данных 3» и «Буфер данных 4»

- •3.3.2 Разработка электрической схемы для блока «Логика управления 2»

- •4 Выбор и обоснование алгоритмов фт озу

- •4.1 Общие сведенья

- •4.1.1 Способы построения алгоритмических функциональных тестов озу

- •4.1.2 Описание неисправностей в двоичном дш адреса озу

- •4.1.3 Описание неисправностей и методы их устранения в матрице озу

- •4.2 Построение фт, проверяющего озу непосредственно после воздействия специальных факторов

- •4.3 Построение фт, проводящее полную проверку озу после всех спецвоздействий

- •5. Выбор и обоснование фт ппзу. Построение алгоритмов

- •5.1 Особенности функционального контроля зу с преимущественным считыванием информации

- •5.2 Построение фт, проверяющего ппзу непосредственно после воздействия специальных факторов

- •5.3 Построение фт, проводящее полную проверку ппзу

- •6 Выбор и обоснование фт набора команд. Построение алгоритмов

- •6.1 Общие сведенья

- •6.1.1 Общая характеристика

- •6.1.2 Типы команд

- •6.1.3 Типы операндов

- •6.1.4 Группы команд

- •6.1.5 Обозначения, используемые при описании команд.

- •6.2 Построение фт, проверяющего набор команд непосредственно после воздействия специальных факторов

- •6.3 Построение фт, проверяющего набор команд

- •7 Разработка печатной платы для схемы функционального контроля ис в сравнении с эталоном

- •7.1 Создание компонентов и ведение библиотек

- •7.2 Создание компонента кр1533тл2 с помощью программы работы с библиотеками p-cad Library Executive

- •7.3 Создание схемы электрической принципиальной с помощью программы p-cad Schematic

- •7.4 Разработка топологии печатных плат

- •7.5 Топология разработанной печатной платы

- •8 Организационно-экономическая часть

- •8.1 Предварительная оценка планируемой к выполнению проектно- конструкторской работы

- •8.2 Организация и планирование окр

- •8.2.1 Расчет трудоемкости окр

- •8.2.2 Распределение трудоемкости окр по исполнителям

- •8.2.3 Расчет договорной цены научно- технической продукции

- •8.3 Технико- экономический анализ конкурентоспособности новой конструкции рэа

- •8.3.1 Выбор и обоснование товара- конкурента

- •8.3.2 Анализ технической прогрессивности нового устройства контроля

- •8.3.3 Анализ изменений функциональных возможностей нового устройства контроля

- •8.3.4 Анализ соответствия новой конструкции рэа нормативам

- •8.3.5 Образование цен товара- конкурента и нового товара

- •8.3.6 Расчет годовых издержек потребителя в условиях эксплуатации

- •8.3.7 Расчет полезного эффекта

- •8.3.8 Расчет нижнего и верхнего пределов нового товара

- •8.3.9 Образование цены потребления и установление коммерческой конкурентоспособности

- •8.3.10 Обоснование конкурентоспособности новой конструкции рэа. Условия выхода на рынок

- •9 Безопасность жизнедеятельности и экологичность

- •9.1 Безопасность жизнедеятельности

- •9.1.1 Анализ вредных и опасных факторов труда в лаборатории нии

- •9.1.2 Обеспечение санитарно-гигиенических требований к помещениям нии и рабочим местам сотрудников

- •9.1.3 Характеристика шума и мероприятия по его снижению

- •9.1.4 Требования к освещению помещений и рабочих мест

- •9.1.5 Вредные факторы при работе с монитором

- •9.1.6 Противопожарная защита

- •9.1.7 Электробезопасность

- •9.1.8 Электормагнитные поля и их нормирование

- •9.1.9 Расчет вентиляции

- •9.2 Экологичность

- •9.3 Оценка устойчивости микроконтроллера к воздействию проникающей радиации

- •9.3.1 Влияние ионизирующего излучения на кристалл микроконтроллера

- •9.3.2 Расчет защитного экрана от нейтронного излучения

2 Разработка структурной схемы устройства функционального контроля восьмиразрядных микроконтроллеров

Функциональный контроль ИС состоит в реализации функциональных тестов и заключается в подаче на ИС входного набора сигналов, формировании выходного эталонного набора сигналов и получении результатов логического сравнения эталонного и выходного (с ИС) наборов сигналов. Контроль функции БИС осуществляется в процессе проведения низкочастотного, функционально-параметрического или предельного ФК. Низкочастотный ФК проводится без контроля статических и динамических параметров БИС для первичной оценки функционирования БИС на этапах разработки, для контроля БИС на пластине и при проведении некоторых видов испытаний БИС (например, механических).

Функционально-параметрический контроль осуществляется с одновременным контролем некоторых статических и (или) динамических параметров. Для проведения предельного ФК необходимо установить временную диаграмму входных наборов сигналов в соответствии со значениями динамических параметров при минимальном значении тактового интервала.

Для проведения ФК используются различные методы, основанные на различных способах задания входных и получения выходных сигналов. Для нашего случая выбираем схему функционального контроля сравнением с эталоном, которая приведена на рисунке 2.1.

Рисунок 2.1- Структурная схема функционального контроля ИС в сравнении с эталоном.

Метод заключается в подаче последовательности входных сигналов одновременно на контролируемую БИС и эталон (эталонная БИС, модель ИС, выполненная на дискретных компонентах и ИС, эмулированная схема программной ЭВМ). И в сравнении последовательности выходных сигналов контролируемой БИС и эталона. На вход могут быть поданы сигналы ФТ, полученные различными способами. ФК этим методом прост, но сложность состоит в выборе эталона. При выборе эталонной ИС сталкиваются с трудностью ее первичной аттестации на соответствие требованиям НТД. Процесс создания модели на дискретных элементах и ИС может быть очень трудоемким.

Метод рекомендуется применять при массовом производственном или входном контроле, в частности для контроля ПЗУ, имеющих большое разнообразие записанных кодов в матрицу ЭП.

Выбор способа генерации входных сигналов определяется наибольшей эффективностью ФК, например для ЗУ- алгоритмические сигналы; для микропроцессоров- сигналы по заданной программе, полученной путем автоматического синтеза тестов; для матричных БИС- псевдослучайные коды.

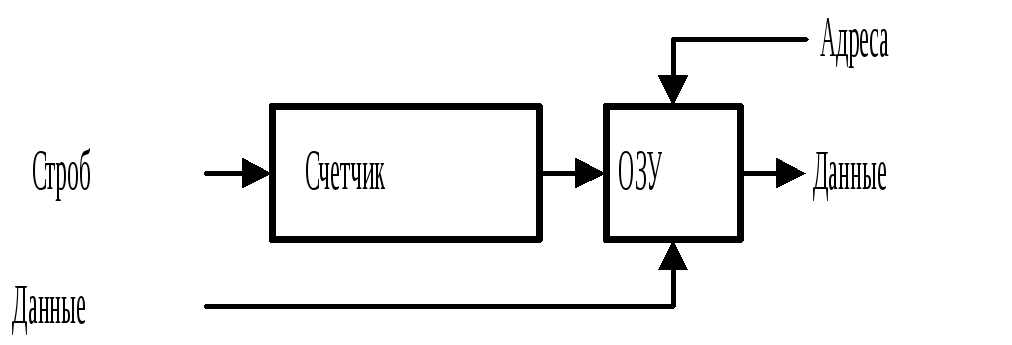

Теперь необходимо решить задачу с получением входных сигналов и с сохранением результатов ФК. В связи с тем, что входные сигналы будут поступать с внешней памяти программ и ФТ состоит из нескольких тестов, а ФК производится непосредственно после воздействия специальных факторов. При этом, в случае сбоя счетчика команд микроконтроллера, необходимо, после 100- 200 мкс выполнения программ, производить его сброс. То получается, что ОЗУ, ПЗУ и правильность выполнения команд необходимо проверять либо одновременно, либо чередовать их с воздействиями специальных факторов. Так как первый способ физически невозможен, получается, что необходимо для каждого теста «перешивать» ПЗУ. Чтобы избежать всех возникающих сложностей предлагается следующий вариант, где вместо ПЗУ используется эмулятор ПЗУ, обобщенная структурная схема которого представлена на рисунке 2.2.

Рисунок 2.2- Обобщенная структурная схема эмулятора ПЗУ.

В качестве основного элемента эмулятора ПЗУ используется статическое оперативное запоминающее устройство (ОЗУ), которое позволяет перезаписывать информацию неограниченное число раз и хранить ее при наличии питания. Доступ к данному ОЗУ возможен со стороны компьютера, в котором хранится и компилируется программа, и со стороны отлаживаемого микропроцессорного устройства в момент его работы. В качестве интерфейса для загрузки программ из компьютера в эмулятор выбран стандартный параллельный интерфейс принтера LPT.

Эмулятор подключается с одной стороны к компьютеру через параллельный порт LPT, а с другой стороны- к отлаживаемому устройству, например микроконтроллеру, вместо ПЗУ. Питание на эмулятор подается от отлаживаемого устройства через цепи питания эмулируемой микросхемы ПЗУ. По параллельному порту в эмулятор загружается программа. На время загрузки эмулятор формирует сигнал сброса для микроконтроллера, поэтому последний находится в состоянии останова и не мешает процессу загрузки программы. После завершения загрузки сигнал сброса снимается, и микроконтроллер стартует с новой загруженной программой, хранимой в эмуляторе ПЗУ.

В представленной обобщенной структурной схеме (рисунок 2.1.) не учтены некоторые факторы, поэтому на рисунке 2.3. представлена полная структурная схема ЭПЗУ.

Рисунок 2.3- Полная структурная схема ЭПЗУ.

Структурная схема, приведенная на рисунке 2.3., состоит из следующих блоков: блока счетчиков- «СТ 1», блока мультиплексоров- «MS1», блока ОЗУ- «RAM1», блока управления- «Логика управления 1» и двух блоков буферов данных- «Буфер данных 1» и «Буфер данных 2». Каждый блок выполняет свою функцию. На блок счетчиков «СТ 1» поступает, поLPTпорту с компьютера, тактовый сигнал (сигнал «Строб»). Одновременно с каждым тактовым сигналом подаются данные с шины «Шина данных 1» на блок «Буфер данных 1». Сигналы с выхода счетчика через блок мультиплексоров («MS1»), рабочий канал которых устанавливается с помощью управляющего сигнала (поступающего с блока «Логика управления 1»), подаются на блок ОЗУ («RAM1»). Одновременно на блок ОЗУ подаются данные с блока «Буфер данных 1». И по управляющему сигналу они записываются в блок «RAM1». В течении всего времени записи контролируемый микроконтроллер и микроконтроллер- эталон находятся в сброшенном состоянии.

После того, как все данные будут записаны в блок ОЗУ, сигнал «Сброс» перестает формироваться, и микроконтроллеры начинают работать. С каждым циклом происходит инкриминация внутреннего счетчика команд и выдача его значения на порты адреса. Эти значения поступают по шине «Шина адреса» через блок мультиплексоров («MS1») на блок ОЗУ. И при помощи управляющего сигнала с блока «Логика управления 1» происходит считывание данных и передача их через блок «Буфер данных 2» по шине «Шина данных 2» на микроконтроллеры.

Теперь после воздействия специальных факторов необходимо проверить двадцать ЭП ОЗУ и ПЗУ и передать результаты в компьютер. Проанализируем быстродействие порта и микроконтроллера. Один цикл микроконтроллера равняется 0,5 мкс, а скорость LPTпорта равна 128 кБайт/с. Так как для проверки одного ЭП необходимо приблизительно пять циклов, то

![]() .

.

Получается, что быстродействие порта недостаточно для считывания результатов. Поэтому необходимо осуществлять промежуточное их хранение до окончания ФТ. В качестве такого накопителя используется модифицированный эмулятор ПЗУ. Данная схема представлена на рисунке 2.4.

Рисунок 2.4- Структурная схема накопителя результатов ФК.

Приведенная структурная схема на рисунке 2.4 практически идентична схеме на рисунке 2.3. Наличие дополнительного счетчика «СТ 2» обосновывается тем, что использование одного счетчика «СТ 1» требует усложнения схемы- добавлением демультиплексора и его логики управления.

Отличие приведенной на рисунке 2.4 структурной схемы заключается в способе адресации к ОЗУ от микроконтроллера (он такой же, как и для компьютера) в связи с этим происходит дублирование управляющих сигналов. Изменилось направление движения данных.

Полная структурная схема представлена на плакате номер один.