- •1. Понятие процессора, его обобщенная структура

- •2. Многофункциональное арифметико-логическое устройство (алу)

- •3. Управляющие автоматы с жесткой логикой

- •4.Управляющие автоматы с микропрограммным управленим (мпу)

- •5. Организация модулей пзу(проверь дш)

- •6. Организация модулей статического озу

- •16-Ти разрядные модули памяти

- •7. Организация динамического модуля памяти (дозу)

- •8. Классификация вычислительных систем по Флинну

- •9. Машины, управляемые потоком данных (df-машины)

- •10.Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •11.Общие принципы построения risc-процессоров. Особенности Старнфордской архитектуры.

- •12. Кэш-память.

- •13. Виртуальная память.

- •14. Синхронный способ подключения ву к см

- •15. Асинхронный способ подключения ву к см

- •16. Требования к кодам команд и способы кодирования микрокоманд

- •17. Организация эвм типа ibm pc (at)

- •18. Процессор Pentium

- •19. Pentium II (Pentium Pro)

- •20. Процессор Pentium IV

- •21. Структуры вс с общей шиной, каждый с каждым, дублированная шина и кольцо

- •22. Структуры вс древовидные, «почтовый ящик» и многопортовое озу

- •23. Архитектуры вс типа Сммр, Сvмр

- •24. Архитектуры вс типа Сm, Blue Chip, минимакс и сумма

- •25. Понятие прерываний, виды прерываний, контроллер прерываний

- •26. Режим прямого доступа к памяти и контролер пдп (кпдп)

- •27. Параллельно программируемый интерфейс (ппи), подключение ву (организация м/о) с помощью ппи

- •28. Однокристальные микро-эвм (оэвм), обобщенная архитектура, основные функциональные узлы (можно на примере mcs-51 или Atmega32)

- •29. Подключение модулей дозу к см. Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

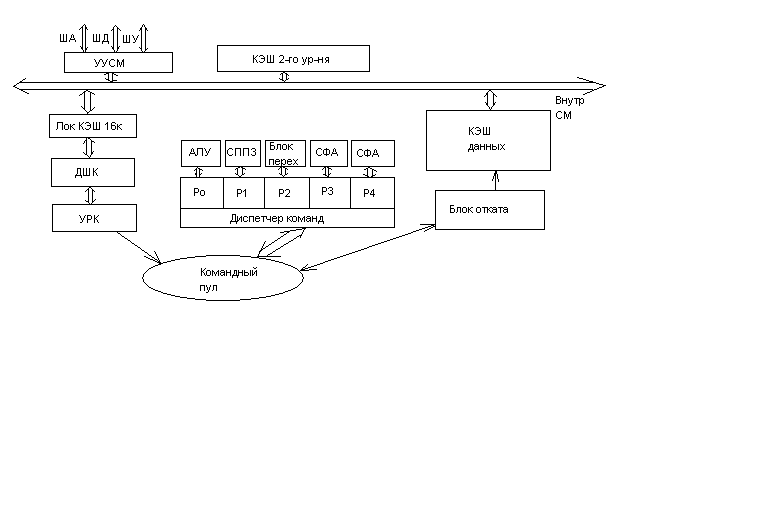

19. Pentium II (Pentium Pro)

почти

1 ммлр операций за сек. УРК- устр распред

команд.

почти

1 ммлр операций за сек. УРК- устр распред

команд.

Процессор имеет суперскалярную архитектуру и на кристалле располагается двухуровневая КЭШ, 16кб КЭШ команд и 16кб КЭШ данных. КЭШ 2-го ур-ня (общая)(128k-2Мбайт). Одновременно работают до5-ти аппаратных ресурса (5 команд может выполн одновременно). Проц имеет 11-ти ступ конвейер т.е. все команды выполняются за 11 тактов. Команда из КЭШ памяти поступает в ДШК, УРК формирует блоки из кодов команд и операндов ктр загружаются в пул команд, ДШ команд из цикла выбирает те команды которые для которых определены операнды и есть свободные аппаратные ресурсы, команды выполн аппаратными ресурсами и возвращаются обратно в пул команд. Блок отката выбирает из пула команд выполненные ком-ды и восстанавливает последовательность выполнения команд в соотв с программой. Результат отправляется в КЭШ данных 1-го уровня. УУСМ формирует распределение команд КЭШ I и II уровня.

Процессор относится к разряду машин управляемых потоком данных. Проц имеет несколько напряж питания : вычислительное ядро запитывается напряж-ем 2,3В, микросхема обвязки (внешний уровень) повышенным, мощность потребл кристаллом достигает 40Вт. Проц имеет встроенный датчик температуры и встроенный АЦП, а также требует внешней системы охлаждения. Потребляемый ток 15-20 А. Это приводит к тому, что ему требуется вентилятор.

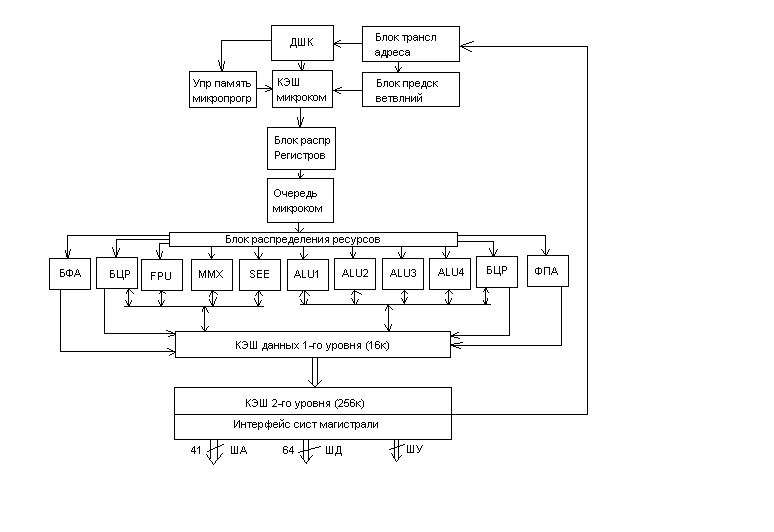

20. Процессор Pentium IV

Внутренняя архитектура гарвардского типа (раздельная память команд и память данных), наличие КЭШ 2-го уровня на одном кристалле (в P III для этого использовался отдельный кристалл и помещался на другом кристалле). Конвейерное выполнение команд(20-ти ступенчатый конвейер). Суперскалярная архитектура (одновременное выполнение нескольких команд на разных аппаратных ресурсах. Спекулятивное (опережающее) выполнение команд (машина, управляемая потоком данных)

БЦР- блок целочисленных регистров, FPU- сопроцессор с плавающей запятой, MMX-Multi Media Extraction, БФА-блок формирования адреса.

Процессор обращается к внешн модулям памяти и с СМ с мах скоростью записывает коды команд и операнды в КЭШ 2-го уровня. ИЗ КЭШ 2-го уровня блок трансляции адресов выбирает код следующей команды. Здесь же команда предварительно дешифрир и если это команда усл или безусл перехода вкл блок предсказания ветвления переходов в котором хранится 4к(4096) адресов последних переходов. Есть 2 дополн бита в адресах которые сигнализируют том как часто происх ветвление по данному адресу.

11-почти всегда

10-часто

01-редко

00-практически никогда

При обращении по предсказанному адресу код адреса автомати-чески инкрементируется (мах 11 так и остается) Если обращение по адр не произошло происх декрементация. (min 00).

ДШК дешифрирует очередную команду, из управляющей памяти микропрограмм выбир-ся последовательность МК, которая запис в КЭШ память м/команд. Блок распр регистров выбирает свободнее регистры(или те которые указаны в командах) которые требуются для выполнения данной команды. Выбранные МК ставятся в очередь МК, в очереди нах-ся до 126 МК это позволяет блоку распредел ресурсов выбирать из очереди МК те МК для которых свободны аппаратные ресурсы(спекулятивная выборка команд). 126 МК позволяют заглянуть вперед на 40 команд ассемблера.

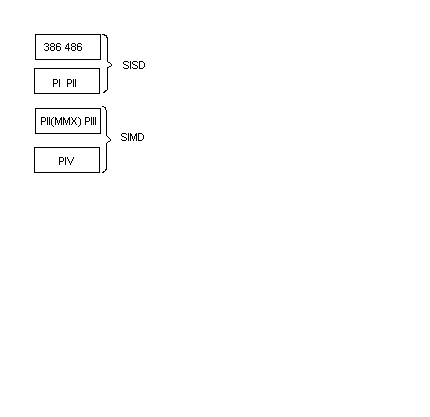

SISD - 1 команда - 1 данные(32р слова)

SIMD – 1 команда –группа данных

64 разр регистр для обного слова=1х64р/слова=2х32р/слова= =8хр/слова. В команде до 8 байтовых данных.

В БЦР содержится 128-32р регистров. Блок ММХ содержит 8ММХ (0..7) 64 разр регистров для реализации функций SIMD арифметики с фикс запятой.

Блок FPU содержит SI(0..7)-64 разр регистра.

SEE –предназначен для реализации команд SIMD арифм с плавающ запятой SEE(0..7) -128р рег-ров.

Главная задача процессора (РIV) обработка мультимедийный приложений и для интернета. М. выпол примерно 10 команд.

Результат выполненный в одном из аппар ресурсов помещ к КЭШ 1-го ур-ня. Последовательность восстановл требуемой цепочки команд осущ двумя блоками формирования адреса (БФА)(Блок отката для РII)

Характеристики бытрод-ия Pentium IV

|

Вид приложения |

Повышение производ по сравн с PIII |

|

1)Обработка целых чисел(Spec Int2000) |

Выше на 23% |

|

2)Обработка чисел с плавающ запятой (Spec fp2000) |

Рост на 79% |

|

3)Кодирование аудио сигналов MP3 Plud 1.3 |

25% |

|

4)Распознавание речи |

27% |

|

5)3D игры (Quake III) |

44% |