- •1. Понятие процессора, его обобщенная структура

- •2. Многофункциональное арифметико-логическое устройство (алу)

- •3. Управляющие автоматы с жесткой логикой

- •4.Управляющие автоматы с микропрограммным управленим (мпу)

- •5. Организация модулей пзу(проверь дш)

- •6. Организация модулей статического озу

- •16-Ти разрядные модули памяти

- •7. Организация динамического модуля памяти (дозу)

- •8. Классификация вычислительных систем по Флинну

- •9. Машины, управляемые потоком данных (df-машины)

- •10.Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •11.Общие принципы построения risc-процессоров. Особенности Старнфордской архитектуры.

- •12. Кэш-память.

- •13. Виртуальная память.

- •14. Синхронный способ подключения ву к см

- •15. Асинхронный способ подключения ву к см

- •16. Требования к кодам команд и способы кодирования микрокоманд

- •17. Организация эвм типа ibm pc (at)

- •18. Процессор Pentium

- •19. Pentium II (Pentium Pro)

- •20. Процессор Pentium IV

- •21. Структуры вс с общей шиной, каждый с каждым, дублированная шина и кольцо

- •22. Структуры вс древовидные, «почтовый ящик» и многопортовое озу

- •23. Архитектуры вс типа Сммр, Сvмр

- •24. Архитектуры вс типа Сm, Blue Chip, минимакс и сумма

- •25. Понятие прерываний, виды прерываний, контроллер прерываний

- •26. Режим прямого доступа к памяти и контролер пдп (кпдп)

- •27. Параллельно программируемый интерфейс (ппи), подключение ву (организация м/о) с помощью ппи

- •28. Однокристальные микро-эвм (оэвм), обобщенная архитектура, основные функциональные узлы (можно на примере mcs-51 или Atmega32)

- •29. Подключение модулей дозу к см. Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

11.Общие принципы построения risc-процессоров. Особенности Старнфордской архитектуры.

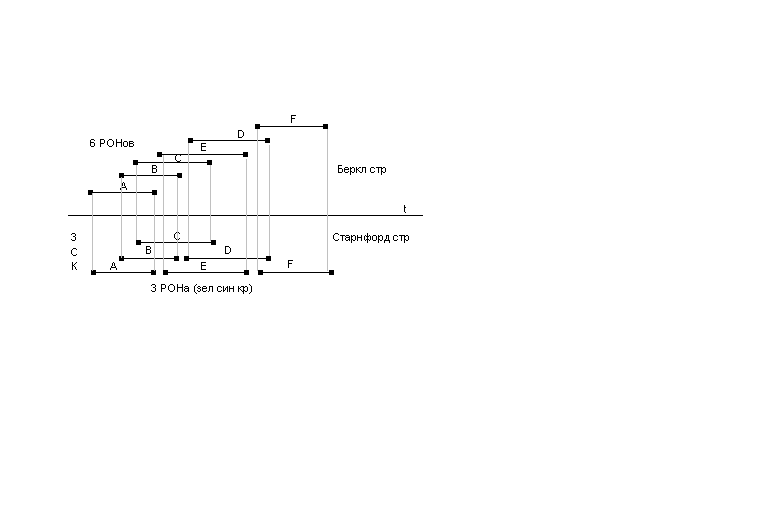

Разработчики ставили первой целью уменьшение аппаратных затрат (РОН) вследствие чего достигается увел такт частоты. При этом решали 2 задачи:

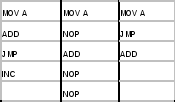

1)Построение оптимизирующего компилятора

Его функции: предотвращение (уменьшение) числа “ломок” конвейера. Конвейер «ломается» из-за неготовности результата выполнения предыдущей команды или при наличии команд условного и безусловного переходов. Конвейерная выборка команд дает выигрыш в производительности в основном не линейных участках программ. Чтобы конвейер не ломался компилятор должен загружать пустые (I)команды NOP(т.е. это лишние такты, потеря производительности), более интеллектуальный компилятор должен менять последовательности команд (II) т.к. загруженная команда в конвейер все равно выполнится. Допустим:

I II

2)Для оптимизации работы аппаратных ресурсов разработчики компилятора использовали метод (рас)окрашенных графов

(не

надо Бер Стен)

(не

надо Бер Стен)

Каждому аппаратному ресурсу присваивается определенный цвет. Использование вышеуказанного подхода позволяет резко сократить число РОНов но увеличивает сложность оптимизирующего компилятора

Достоинства:

Беркл 1)Простота программ-я 2)Min число пересылок инф 3) Min число обращений к внешн ЗУ.

Старн 1)Min аппаратн затраты 2) Max тактовая частота

Недостатки:

Беркл 1)Большие аппаратн затраты 2) Низкая тактовая частота

Старн 1) Сложность компилятора 2) Сложность прогр-я

Современные RISC проц-ры обычно испоьз от 32 до 128 РОНов. Тактовая частота 100MHz, с контроллерами по другому: 40МГц, больше уже не рабоают.

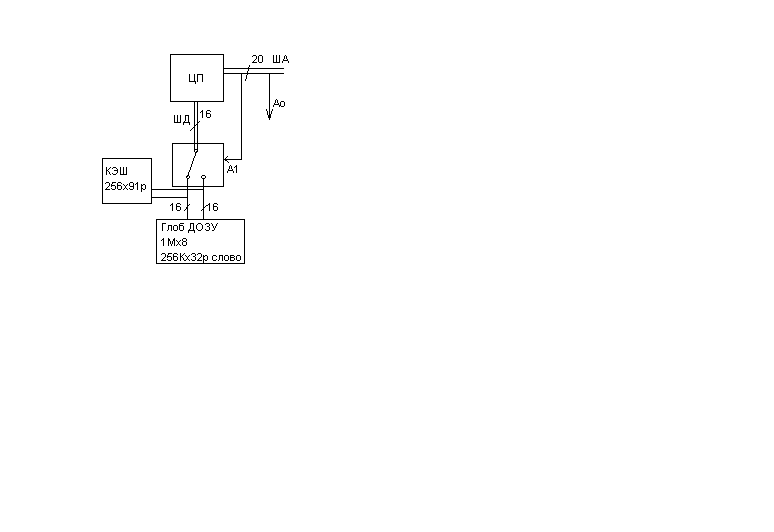

12. Кэш-память.

Увеличение объема памяти приводит к уменьш быстродействия (время на дешифрацию) .Кроме этого обращение к внешн памяти (выход за пределы кристалла) снижает быстр примерно на порядок по сравн с быстр внутри кристалла (тактовая частота 2 ГГц, тактота обращение к памяти 125-133 МГц). Подавляющее большинство программ носит циклический характер.

КЭШ память предназначена для хранения последних наиболее часто встречающихся команд. КЭШ-память располагается или внутри кристалла проц или максимально близко к нему и время обр к КЭШ-памяти не порядок быстрее чем к глобальному ДОЗУ.

|

|

Копия в КЭШ |

Инф | |

|

В КЭШ |

В гл ДОЗУ | ||

|

Чтение |

Есть Нет |

Чтение Запись+след слово |

- Чтение |

|

Запись |

Есть Нет |

-(обновление) - |

Запись Запись |

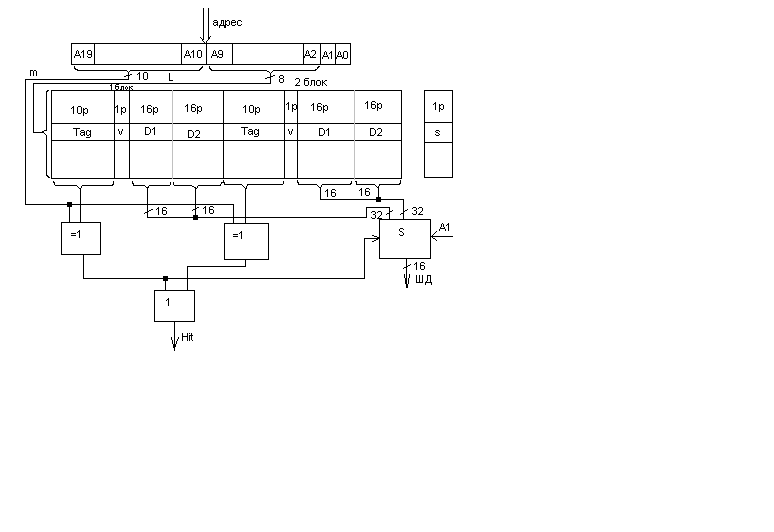

Ао-выбирает байт в 16-ти разр слове

А1-выбир какое 16-ти разр слово берем

КЭШ-память имеет структуру 256 слов на 87 разрядов. Младш часть адреса L (разряды с А2 по А9) возбуждает одну из 87-разр ячеек КЭШ-памяти (8 разрядов указыв адр одной из 256 ячеек). Старш часть адр m наз-ся тегом и сопровождает данные записываясь в один из банков КЭШ-памяти. Проц обращаясь к памяти выставляет на ША адр , младшая часть адр возбуждает одну из 256 ячеек КЭШ-памяти, старшая часть адр сравнивается с тэгами записанными в 1 и 2 блоках КЭШ-памяти если m≠Tэги это значит копии в КЭШ памяти нет и необх обращаться к гл. ДОЗУ (Hit=1), если mсовпало с одним из тегов это означает что такой адрес уже выставлялся и инф нах-ся в КЭШ-памяти (Hit=0) и сигнал А1 ч/з мультиплексор S вы-дает на ШД 16-ти разр данные одного из банков КЭШ-памяти. V-признак истинности инф,по сбросу сбрасывается в 0 при созд копии в КЭШ устанавл в 1. S-признак старости или выборки банка.