- •1. Понятие процессора, его обобщенная структура

- •2. Многофункциональное арифметико-логическое устройство (алу)

- •3. Управляющие автоматы с жесткой логикой

- •4.Управляющие автоматы с микропрограммным управленим (мпу)

- •5. Организация модулей пзу(проверь дш)

- •6. Организация модулей статического озу

- •16-Ти разрядные модули памяти

- •7. Организация динамического модуля памяти (дозу)

- •8. Классификация вычислительных систем по Флинну

- •9. Машины, управляемые потоком данных (df-машины)

- •10.Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •11.Общие принципы построения risc-процессоров. Особенности Старнфордской архитектуры.

- •12. Кэш-память.

- •13. Виртуальная память.

- •14. Синхронный способ подключения ву к см

- •15. Асинхронный способ подключения ву к см

- •16. Требования к кодам команд и способы кодирования микрокоманд

- •17. Организация эвм типа ibm pc (at)

- •18. Процессор Pentium

- •19. Pentium II (Pentium Pro)

- •20. Процессор Pentium IV

- •21. Структуры вс с общей шиной, каждый с каждым, дублированная шина и кольцо

- •22. Структуры вс древовидные, «почтовый ящик» и многопортовое озу

- •23. Архитектуры вс типа Сммр, Сvмр

- •24. Архитектуры вс типа Сm, Blue Chip, минимакс и сумма

- •25. Понятие прерываний, виды прерываний, контроллер прерываний

- •26. Режим прямого доступа к памяти и контролер пдп (кпдп)

- •27. Параллельно программируемый интерфейс (ппи), подключение ву (организация м/о) с помощью ппи

- •28. Однокристальные микро-эвм (оэвм), обобщенная архитектура, основные функциональные узлы (можно на примере mcs-51 или Atmega32)

- •29. Подключение модулей дозу к см. Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

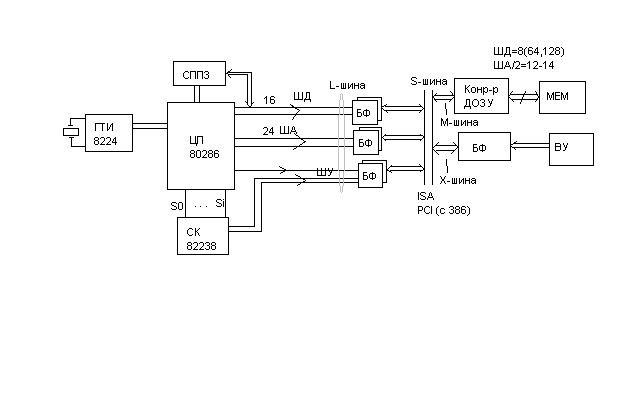

17. Организация эвм типа ibm pc (at)

Процессоры: 8086, 80186, 802861810 ВМ 86

80386, 80486 -->PCI-I, 80586, … PCI-II

ССПЗ-сопроцессор

с плав запят. L-шина

обладает пониженным напряж питания(напр

пит ЦП) S-шина

нормальная магистраль 5В. Первое

поколение- ISA

шины следующее PCI.

Как вариант PCI

была шина VESA.

М-шина (шина подкл памяти) Разрядность

М шины ША/2-потому что динамич память –

КДОЗУ формирует адр строки, адр столбца,

Х-шина обращения к ВУ.

ССПЗ-сопроцессор

с плав запят. L-шина

обладает пониженным напряж питания(напр

пит ЦП) S-шина

нормальная магистраль 5В. Первое

поколение- ISA

шины следующее PCI.

Как вариант PCI

была шина VESA.

М-шина (шина подкл памяти) Разрядность

М шины ША/2-потому что динамич память –

КДОЗУ формирует адр строки, адр столбца,

Х-шина обращения к ВУ.

Базовый матричный кристалл VL82C100- контроллер ВУ на 84 контакта, имеется 2 контроллера ПДП 82237, 2 контрол прерываний, таймер)

VL82C101-сист контрол(генератор тактовык импульсов 8224, сист контрол 88238,СППЗ 80287) с пониженным питанием.

VL82C102-контроллер ДОЗУ

Протокол обмена по системной шине ISA (такой же как у процессора 1810ВМ86) каждый обмен выполн за 4 такта. 1 такт состояния 2 такт-командный.

Любая ЭВМ содержит: ЦП, ГТИ, модули ПЗУ, модули ОЗУ, таймер, контролер прерыв(м/б и ПДП), устр упр вв/выв (ППИ), устр последов вв/выв.

Если все эти устр-ва установить на одном кристалле то получится однокристальная ЭВМ (транспьютер).

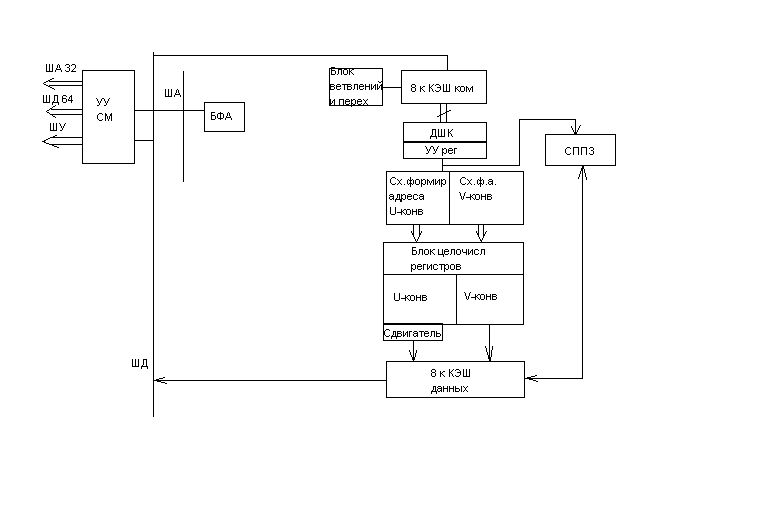

18. Процессор Pentium

С начала 486 проц а затем и проц ряда Pentuim стали использовать эл-ты RISC арх-ры (глубокий конвейер, все команды выполняются за опр промеж времени). С переходом на Pentium для обеспечения min выполнения команд арифметики с палвающ (,) потребовалось сильно переделать СПЗ(сопроцессор с плав запят) первые партии Pentuim были с ошибкой в СПЗ.

ША-32 ШД-64(внешн) ШД-32(внутр)

БФА –блок формирования адреса, СППЗ – сопроцессор с плавающей запятой, Блок ветвления и переходов, схема формирования перхода Uконвейера, блок целочисленных регистров

Процессор имеет суперскалярную архитектуру (закладывается параллелизм) и при тактовой частоте 66MHz процессор обепечивал производ-ть до 100млн опер/с. Внутр структура проц Гарвардская (раздельная память команд и память данных). Внешняя структура фон-Неймановская. Обращение в внешней памяти идет блоками по 4 64-разр слова для заполнения 256 разр КЭШ. Процессор имеет 2 параллельно работающих 5-ти ступенчатых конвейера U и V. Конв U полноразмерный и на нем может выполн любая ариф и лог команда. U имеет 64-разр сдвигатель (удобно для работы с двойными словами). Конв V упрощенный, предназначен для выполнения простых команд типа сдвига,лог опер (легких). Команда из КЭШ дешефрируется (ДШК) и УУ рег-ми и микрокомандами выбирает аппаратные ресурсы необход-е для выполн данной команды, при этом команды анализирются на возможность их одновременного выполнения в U и V конв. Схема формир адр следит за тем чтобы последовательность выполнения команд не нарушалась.

В проц-ре впервые исполз схема предсказания переходов (блок ветвл переходов).В БВ хранится до 256 адресов последних переходов. Вероятность предсказания ≈10 (90)%. Принцип такой: если переход состоялся то в след цикле наиболее вероятно , что этот переход повторится. Это позволяет не ломать “логику” конвейера.

БФА обеспечивает формир адреса при работе с внешними модулями памяти и ВУ. Адр простр памяти и ВУ раздельное.

Проц имеет возможность работать с КЭШ 2-го уровня который нах-ся на матер плате (в процессоре встр контроллер КЭШ памяти и встроенный контроллер Вирт памяти.)