- •1. Понятие процессора, его обобщенная структура

- •2. Многофункциональное арифметико-логическое устройство (алу)

- •3. Управляющие автоматы с жесткой логикой

- •4.Управляющие автоматы с микропрограммным управленим (мпу)

- •5. Организация модулей пзу(проверь дш)

- •6. Организация модулей статического озу

- •16-Ти разрядные модули памяти

- •7. Организация динамического модуля памяти (дозу)

- •8. Классификация вычислительных систем по Флинну

- •9. Машины, управляемые потоком данных (df-машины)

- •10.Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •11.Общие принципы построения risc-процессоров. Особенности Старнфордской архитектуры.

- •12. Кэш-память.

- •13. Виртуальная память.

- •14. Синхронный способ подключения ву к см

- •15. Асинхронный способ подключения ву к см

- •16. Требования к кодам команд и способы кодирования микрокоманд

- •17. Организация эвм типа ibm pc (at)

- •18. Процессор Pentium

- •19. Pentium II (Pentium Pro)

- •20. Процессор Pentium IV

- •21. Структуры вс с общей шиной, каждый с каждым, дублированная шина и кольцо

- •22. Структуры вс древовидные, «почтовый ящик» и многопортовое озу

- •23. Архитектуры вс типа Сммр, Сvмр

- •24. Архитектуры вс типа Сm, Blue Chip, минимакс и сумма

- •25. Понятие прерываний, виды прерываний, контроллер прерываний

- •26. Режим прямого доступа к памяти и контролер пдп (кпдп)

- •27. Параллельно программируемый интерфейс (ппи), подключение ву (организация м/о) с помощью ппи

- •28. Однокристальные микро-эвм (оэвм), обобщенная архитектура, основные функциональные узлы (можно на примере mcs-51 или Atmega32)

- •29. Подключение модулей дозу к см. Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

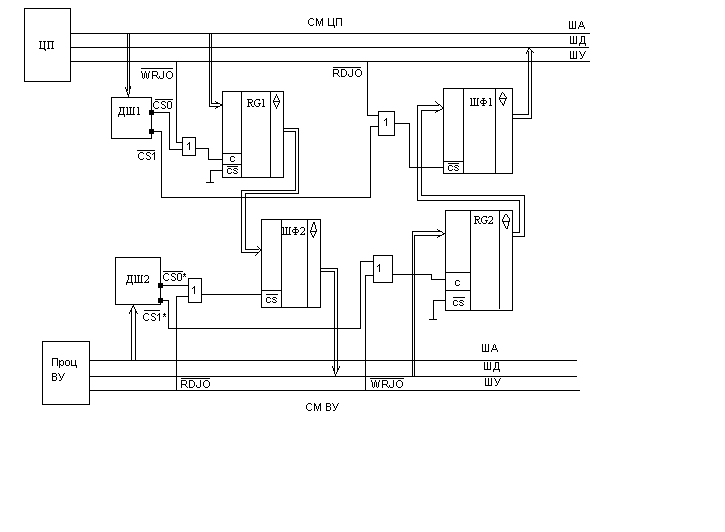

14. Синхронный способ подключения ву к см

Практически все ВУ содерж свой лок проц (обычно менее мощный чем ЦП)

При синхр способе предполагается что ВУ всегда готово к обмену инф (обычно тогда, когда быстродейств ВУ>= быстродейств ЦП). ЦП выставляет на ША адрес ВУ (возбуждается сигнал CS0 с выхода ДШ1 и в прогр доступный RG1 записывает с ШД код ком-ды предназначенной для ВУ.Если ШД многоразр или состоит из нескольких байтов || RG1 ставится еще RG, логика упр таже самая). ВУ периодически обращается по адресу СSO* и ч/з ШФ2 считывает содерж RG1, получив код ком-ды ВУ выполн ее (делает какую-то последов дейтствий (подпрогр)) и обращаясь по адр CS1* записывает в RG2 рез-тат. ЦП после записи ком-ды в RG1 выдерж паузу (дает время на выполн ком-ды ВУ) затем обр по адр CS1 и ч/з

ШФ1 считывает из RG2 результат.

Синхр способ обмена приводит к тому что ЦП может считать из RG2 неправильные данные( если ВУ не успело поместить рез-т) что приводит к потере производ ЦП из-за тог что дается избыточная пауза на ожидание рез-та ВУ. Сочетание регистра и шинного формирователя будем называть порт

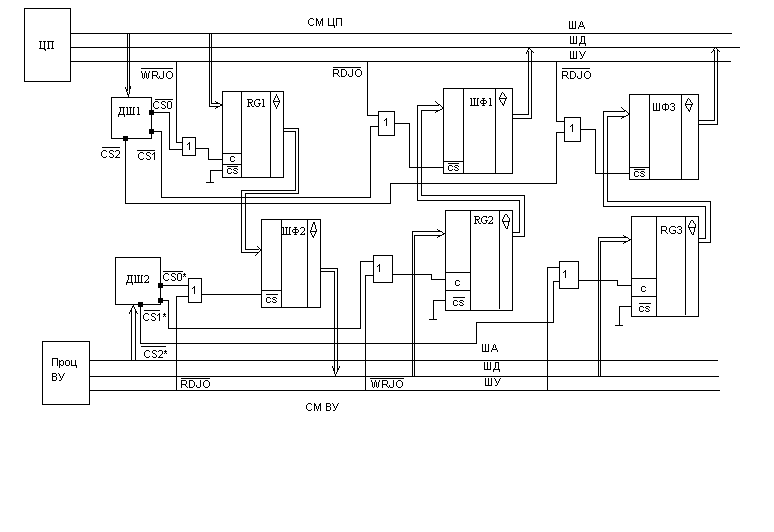

15. Асинхронный способ подключения ву к см

При асинхр способе обмена ЦП записывает в RG1 код команды для ВУ, ЦПВУ периодически обращаясь к RG1 ч/з ШФ2 считывает код ком после чего обращаясь по адр CS2* записывает в RG3 ССВУ (Слово Состояние) которым сообщает ЦП что приступило к выполнению команды и рез-тат еще не готов, после окончания выполн-я ком-ды ЦПВУ обращаясь по адр CS1* запис рез-т в RG2 а после этого обращ по адр CS2* и перезаписывает в RG3 ССВУ (сейчас это слово сообщ ЦП что рез-т в RG2). ЦП периодически обращается по адр CS2 и ч/з ШФ3 считывает ССВУ, получив код что рез-т готов, ЦП обр-ся по адр CS1 и ч/з ШФ1 считывает рез-т из RG2.

16. Требования к кодам команд и способы кодирования микрокоманд

Код команды должен соотв требованиям:

1)Указывать на код операции (кот выполняется)

2)Указывать на адрес(адреса) одного(неск) операндов участв в выполнении команды данной команды.

3)Указывать на адрес,куда помещается результат выполнения ком

4)Указывать на адрес след команды

Способы:

1)Горизонтальное кодирование.При гориз кодир каждому упр возд yi выдел-ся свой разряд в Рг.МК.

|

y1 |

y2 |

… |

. |

yn |

Каждому управляющему воздействию yi выделяется свой разряд в регистре МК. +: высокое быстродействие(в любо мом времени можно выполн любой у или несколько)

- : высокие аппаратные затраты

2)Вертикальное кодирование.

![]()

в Рг.МК. запис двоичн код или номер yi ктр необх выполн.

-: одно упр возд yi в ед времени

+:низкие аппаратные затраты и малая разрядность.

3)Вертикально-гориз микропрограмм-е.

Вся совокупность упр возд yi делится на К подгрупп наиболее часто выполняемык одновременно yi.

К

К

|

y1…………yn |

|

К – двоичный код N подгр. (задается верт) a yi в подгр – горизонт

4)Горизонтально-верикальное микропрогр

Всё множ-во упр возд yi разбив-ся на К подгр по принципу несовместных команд или встр очень редко.

N групп кодируется горизонтально, yi – вертикально

![]()

Высокое быстр и высокие аппаратные затраты.