- •1.Процессоры. Иерархия языков вт

- •Иерархия языков вт

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •4.Алу для деления чисел с фиксир(,)

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •8.Управл автоматы с мпу

- •9.Требования к кодам команди способы кодирования.

- •11.Шинные формирователи и рег-ры. Орг см 580 серии

- •Организация см процессора

- •12.Организация модулей пзу

- •13.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •14.Организация динамических модулей дозу

- •15.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •16.Синхр способ продкл ву к см

- •17.Асинхр способ продкл ву к см

- •18.Организация кэш памяти.

- •19.Организация виртуальной памяти.

- •20.Общие полож.Risc-проц.Берклинская арх.

- •21.Старнфордсая структура

- •22.Машины упр потоками данных(df-машины)

- •23.Pentium

- •24.Pentium II,Pentium Pro

- •25.Pentuim VI

- •27.М/о ч/з ппи.

- •28.Усапп

- •29.Контролер пдп.

- •30.Прогр контр прерываний.

- •31.Таймер

- •32.Орг эвм типа ibm pc at

- •33,Однокристальн эвм

- •34.Протокол обмена подкл озу/пзу mcs-51

- •35.ATmega 32

- •36.Классификация оэвм по табл

- •35.Вс классификация по Флинну

- •38.Производительность эвм и сетей.

- •38.Типовые структуры вс

- •40.Архитектура Сммр,Сvмр,См.

- •41.Сm структура.

- •42. Понятие интерфейса. Виды арбитража

- •43.Арбитраж по последовательному опросу.

- •44. Контроллер прерываний по последовательному опросу

- •45.Арбитраж по || опросу.

- •46.Синхронизация информации в интерф.

27.М/о ч/з ппи.

По сбросу проц-ры программируют ППИ в режим 0 (или 1). Каналы С1 и С2 прогр-ся на передачу слов состояния(битов квитирования => асинхр способ обиена). Каналы А и В на ввод или вывод инфы, чтобы не изменять ПО для 2-х однотипных устройств в кабеле м/у ППИ делается перекоммутация канала А на В и наоборот, тогда сохр-ся направление передачи инф-ии.

Организация м/о n-машин ч/з ППИ.

Пр-р1 – ведущий, все остальные ведомые. По вкл-ю питания пр-р1 прогр-т ППИ в режим 0, к-лы В и С настраиваются на вывод, кА на ввод – вывод. Пр-р1 записывает в кВ адрес внешнего устройства (с помощью ППИ формируется новая СМ, отдельная для внешних устройств).Если Пр-р1 надо получить инфу от внешнего уст-ва, то пр-р1 записывает в кС бит RD*. Комбинация адреса Дш1 и сигнал RD* открывает шинный формирователь N и инфа от регистра пр-ра N поступает в кА ППИ (в этом случае кА настроен на ввод).Пр-р N ч/з шинный формирователь может периодически считывать предназначенные для него инфу кА. Количество машин в этом случае ограничено загруженностью портов ППИ и длиной линии связи.

Обмен инфы последовательным кодом.

При передаче инфы на большие расстояния число линий связи ограничено(радиоканал, оптоволокно). В этом случае передача инфы идет в последовательном коде. При передаче инфы следует решить следующие задачи:

1)опр-ть сост. получ. инфы (выкл.,занят, свободен)

2)опр-ся направление передачи инфы

3)достоверность переданной инфы

4)преобр-ть парал.код в послед. и наоборот.

28.Усапп

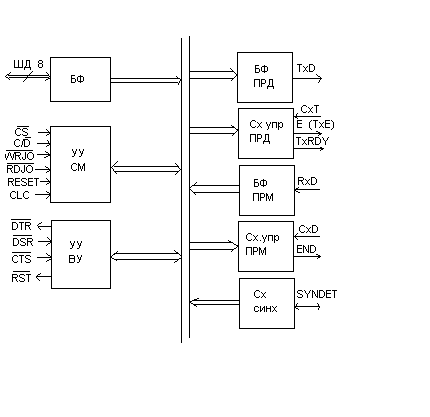

ПРД-передатчик, ПРМ-приемник сх.синхронизации,

С/D=А0-команда или данные(1 и 0), WRJ0-запись на внешнее устройство, CLC-тактовая чостота, DTR-запрос готовности передатчика ВУ, СTS-готовность приемника ВУ, DSR-готовность передатчика от ВУ, RTS- запрос готовности приемника ВУ, TxD-передатчик данных последовательным кодом, CxT-внешняя тактовая частота для асинхронизации, E- конец передачи (TxE), RDY- готовность передатчика, RxD-вход приемника последовательным кодом, CxD-внешняя синхронизация приемника, SYNDET – бит синхронизации( показывает какая синхр внешн или внутр).

В УСАПП есть режимы как синхр., так и асинхронного программирования.

После сброс (по вкл. питания) осущ-ся программирование УСАПП. Программирование осущ-ся 2 типами управляющих строк:

1)инструкция режима

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Режимы(D0D1)

00-режим синхр.

01-асинхр. 1:1

10-асинхр1:16

11-асинхр. 1:64

Формат слов(D3D2)

00-5-ти битное слово

01-6-ти битное слово

10-7-ти битное слово

11-8-ти битное слово

Контроль(D5D4)

x0-нет, 01-на нечетность, 11-на четность

Длина стоповой посылки(D7D6)

00-запретная комб-я, 01-1 бит, 10-1,5 бита, 11-2 бита

R S-232

S-232

RS-485

RS-422

Ряд

200

300

1200

2400

4800 9000 14800 49200 56000 …

1:64, 1 бит передается за 64 такта входной частоты

если стоповый бит 1,5 то при частоте 1:16 (за 24 такта), а 1:64(96)

При асинхронной передаче 1 инф-й бит передается столько периодов тактовой частоты, ск-ко задано битами D0D1 в инстр-ции режима. После стопового бита(1 выс ур-нь) передача начин стартовым битом(0 низ ур), затем идут инф-е биты, начиная с D0; по окончании инф-й посылки может быть контрольный бит9задается битами D5D4 инстр режима) после чего формируется стоповый бит ур.1.Тактовая частота задается внешними делителями по станд.ряду, соотв.интерфейсу типа RS

При синхронном режиме в паузах непрерывно передаются синхросимволы. Синхросимволы-собств. имя УСАПП. Если УСАПП настроен на прием, то он в получ. инфе отыскиваем сигналы одного или двух синхросимволов. Если УСАПП настроен на передачу в синхронном режиме перед передаваемыми данными УСАПП выдает собств.имя получателя (1 или 2 байта синхронизации). Затем выдается информационный байт о том, что байты синхронизации совпали УСАПП символ. наличием сигнала SYNDET. При синхронном режиме тактов частота также может подаваться на вход SYNDET.При сихр реж каждому периоду тактовой частоты соответствует 1 бит инфы.