- •1.Процессоры. Иерархия языков вт

- •Иерархия языков вт

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •4.Алу для деления чисел с фиксир(,)

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •8.Управл автоматы с мпу

- •9.Требования к кодам команди способы кодирования.

- •11.Шинные формирователи и рег-ры. Орг см 580 серии

- •Организация см процессора

- •12.Организация модулей пзу

- •13.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •14.Организация динамических модулей дозу

- •15.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •16.Синхр способ продкл ву к см

- •17.Асинхр способ продкл ву к см

- •18.Организация кэш памяти.

- •19.Организация виртуальной памяти.

- •20.Общие полож.Risc-проц.Берклинская арх.

- •21.Старнфордсая структура

- •22.Машины упр потоками данных(df-машины)

- •23.Pentium

- •24.Pentium II,Pentium Pro

- •25.Pentuim VI

- •27.М/о ч/з ппи.

- •28.Усапп

- •29.Контролер пдп.

- •30.Прогр контр прерываний.

- •31.Таймер

- •32.Орг эвм типа ibm pc at

- •33,Однокристальн эвм

- •34.Протокол обмена подкл озу/пзу mcs-51

- •35.ATmega 32

- •36.Классификация оэвм по табл

- •35.Вс классификация по Флинну

- •38.Производительность эвм и сетей.

- •38.Типовые структуры вс

- •40.Архитектура Сммр,Сvмр,См.

- •41.Сm структура.

- •42. Понятие интерфейса. Виды арбитража

- •43.Арбитраж по последовательному опросу.

- •44. Контроллер прерываний по последовательному опросу

- •45.Арбитраж по || опросу.

- •46.Синхронизация информации в интерф.

Организация см процессора

Команды на ШУ

__ ____ ____ ___ ____ ____ _____ ____

RD RDJO WRJO WR JNTE HLD HLDA RDY

Для увел нагр способн ЦП и формир СМ использ ШФ и объединение комбинация RG и КЛС которая выпускается в одном кристалле и наз-ся системным контроллером.Что бы обеспечить реж ПДП, ШФ и СК перев-ся в 3 сост (откл от СМ) сигн HLDA=1 (сигн разр ПДП). Напр передачи ШФ ШД задается сигн чтения (или записи для нек проц-ов).Т.к. проц имеет раздельное адресн простр для памяти и ВУ, СК формир разл сигн обращ к памяти (RD,WR) и сигн обр к ВУ (RDJO,WRJO).

12.Организация модулей пзу

Пусть требуется подкл модуль 24 kb начиная с 0 адр, состоящий из микросх 8кх8 (нужно 3 м.сх.)

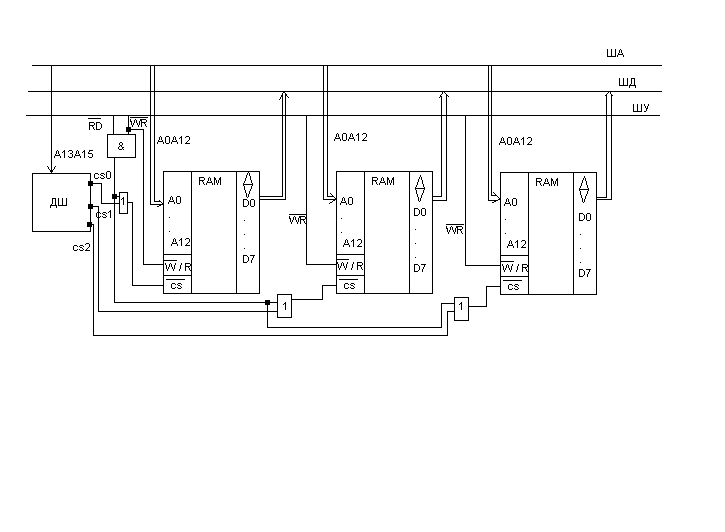

13.Организация модулей статического озу.

1![]() )Рис

карту адресного простр

)Рис

карту адресного простр

2)Опр область вкл каждой микросх на карте адр простр-ва . Для каждой микросх строится ДШ на опр комб ША (на ДШ поступают старш разр с ША,а младш поступ на микросх ОЗУ)

![]()

8-ми разрядные модули памяти

16-Ти разрядные модули памяти

ВНЕ- выборка старшего байта.

|

ВНЕ |

А0 |

|

0 |

0 |

|

0 |

1 |

|

1 |

0 |

|

1 |

1 |

16-разр слово

старший байт

младший байт

нет обр-я

П ри

обращении к 16 разр ШД в ШУ присутсвует

сигнал ВНЕ, ктр в комбина-ции с Ао

обеспеч-ивает обр-е к 16 разр слову

отдельно млад или отдельно старш

байту.Счетчик комнд после обрпо адресу

автом увел на два (слова располагаются

по четным адр т.е. Ао=0).

ри

обращении к 16 разр ШД в ШУ присутсвует

сигнал ВНЕ, ктр в комбина-ции с Ао

обеспеч-ивает обр-е к 16 разр слову

отдельно млад или отдельно старш

байту.Счетчик комнд после обрпо адресу

автом увел на два (слова располагаются

по четным адр т.е. Ао=0).

14.Организация динамических модулей дозу

В ДОЗУ одна ячейка памяти строится на

одном полевом транзисторе(в статических

ОЗУ на одну ячейку памяти прих 2 тр)

ДОЗУ одна ячейка памяти строится на

одном полевом транзисторе(в статических

ОЗУ на одну ячейку памяти прих 2 тр)

в![]() ДОЗУ хранение инф обеспечив за счет

наличия заряда на паразит-ной емкости

затвора-истока. Инф в динам ячейке ч/з

какое-то время пропадает за счет

рассеивания заряда из-за сопротивл этой

емкости. Чтобы этого не происходило инф

в ДОЗУ периодически восстанавл

(регенерируется)t

м/у интерва регенерации для совр микросх

ДОЗУ составл 8-16 мс. Регенер обычно осущ

подачей напряжения питания на транз

ячейки

(если U

есть инф восст).

ДОЗУ хранение инф обеспечив за счет

наличия заряда на паразит-ной емкости

затвора-истока. Инф в динам ячейке ч/з

какое-то время пропадает за счет

рассеивания заряда из-за сопротивл этой

емкости. Чтобы этого не происходило инф

в ДОЗУ периодически восстанавл

(регенерируется)t

м/у интерва регенерации для совр микросх

ДОЗУ составл 8-16 мс. Регенер обычно осущ

подачей напряжения питания на транз

ячейки

(если U

есть инф восст).

R![]() AS

– строк

сопровожд адр строки

AS

– строк

сопровожд адр строки

CAS – строк сопровожд адр столбца

Н а

ША конт-роллером ДО ЗУ выставл адр стр

Ах и защелкивает-ся отриц фр-онтом

сигн-ла RAS

в Рг

а

ША конт-роллером ДО ЗУ выставл адр стр

Ах и защелкивает-ся отриц фр-онтом

сигн-ла RAS

в Рг

ДОЗУ, затем контроллер ДОЗУ выставл на ША адр столбща Ау ктр защелк по отриц фронту сигн СAS, RAS=0 и CAS=0 ; вкл микр в работу и она анализир сигналы W/R и в завис от него считывает инф с ШД в себя или выдает на ШД. Появл CAS и RAS =1 переводит ее выход по ШД в 3 сост. Для того чтобы вызвать регене-рацию (в завис от типа микросх) сущ неск способов:

1)Only RAS

2![]() )Обычно

использ в встр счетчиком адреса регенер

и наз-сяCAS

before

RAS

)Обычно

использ в встр счетчиком адреса регенер

и наз-сяCAS

before

RAS

15.Покдл модулей дозу к см(прозр рег).Способы регенерации

Прозр регенер- это такая регенерация о сущ которой на процессор не догадывается. (задержек нет).

2 MHz Т=500нс

Т.к. быстродействие памяти выше в данном случае быстр проц-ра (Тпрой=500нс)(Время доступа к ДОЗУ 150-200нс),то за один период тактовой частоты проц быстрод микросх ДОЗУ позволяет провести цикл регенер.Этот цикл удобно делать тогда когда на ШД нах-ся ССП (еще нет обращения к ДОЗУ). На быстрод процессора это не сказывается

Прозр регенер возможна когда ДОЗУ быстрее проц-ра.

Регенер ДОЗУ с блокировкой сигнала готовности RDY- прим тогда когда бвстрод ДОЗУ < быстр проц. В этом случае цикл реген осущ не каждый цикл обр к памяти (как в прозр регенер), а один раз за несколько циклов бор (зависит от проц и времени хранения инф в ДОЗУ) обычно 1 цикл реген приходится на 64-128 циклов обр-я. В цикле реген происх блокирование сигнала RDY на 1-2 такта чтобы успеть провести регенер.Это снижает производительность проц-ра на доли процента что приемлимо.

3 способ регенер ДОЗУ в режиме ПДП В эстом случае один раз за 8-16мс проц перев в режим ПДП и контроллер ДОЗУ осущ группу циклов регенер для всего модуля ДОЗУ.