- •1.Процессоры. Иерархия языков вт

- •Иерархия языков вт

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •4.Алу для деления чисел с фиксир(,)

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •8.Управл автоматы с мпу

- •9.Требования к кодам команди способы кодирования.

- •11.Шинные формирователи и рег-ры. Орг см 580 серии

- •Организация см процессора

- •12.Организация модулей пзу

- •13.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •14.Организация динамических модулей дозу

- •15.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •16.Синхр способ продкл ву к см

- •17.Асинхр способ продкл ву к см

- •18.Организация кэш памяти.

- •19.Организация виртуальной памяти.

- •20.Общие полож.Risc-проц.Берклинская арх.

- •21.Старнфордсая структура

- •22.Машины упр потоками данных(df-машины)

- •23.Pentium

- •24.Pentium II,Pentium Pro

- •25.Pentuim VI

- •27.М/о ч/з ппи.

- •28.Усапп

- •29.Контролер пдп.

- •30.Прогр контр прерываний.

- •31.Таймер

- •32.Орг эвм типа ibm pc at

- •33,Однокристальн эвм

- •34.Протокол обмена подкл озу/пзу mcs-51

- •35.ATmega 32

- •36.Классификация оэвм по табл

- •35.Вс классификация по Флинну

- •38.Производительность эвм и сетей.

- •38.Типовые структуры вс

- •40.Архитектура Сммр,Сvмр,См.

- •41.Сm структура.

- •42. Понятие интерфейса. Виды арбитража

- •43.Арбитраж по последовательному опросу.

- •44. Контроллер прерываний по последовательному опросу

- •45.Арбитраж по || опросу.

- •46.Синхронизация информации в интерф.

4.Алу для деления чисел с фиксир(,)

1)Проверятся возможность деления (В=0)

2)А- представляется в виде полож числа, В- в виде отриц числа в доп коде

3)Частичный остаток=0

4)Делимое сдвигается на один разряд влево и выдвигаемый разряд заносится в част.остаток(в младш.разр)

5)Частичный остаток складыв(вычитается) с делителем

6)Если знак рез-та отриц в частное заносится 0 и выдвиг след разр

Если знак полож в частное заносится 1 и выдвиг след разр

Пункты 5,6 повторяются столько раз,какова разр сетка.

7)Если делимое и дел-ль одного знака,то частное + иначе –

На тех же аппаратных ресурсах делается *, т.е. с одними аппарат-ными затратами вып-ся + - * /.Только за счет изменения микропрограммы. Ускоренное / делается так же по табл истин-ти.

5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

С>D 10 С<D 01 С=D 00

В![]() ВМ инф представл-ся кратной байтам, в

Рг 1 и Рг 2 запис-ся опер-ды, между котор-ми

надо провести как-ю-либо лог.опер.,или

сравн.

ВМ инф представл-ся кратной байтам, в

Рг 1 и Рг 2 запис-ся опер-ды, между котор-ми

надо провести как-ю-либо лог.опер.,или

сравн.

Эти опер-ды разбив-ся на байты, ктр. помещ-ся в Рг С и D, СОЛО произв лог.обраб-ку байтов, результирующий байт помещается в Рг Е,а из него на место соотв байта Рг рез-та,опер-я повтор-ся со всеми байтами операндов.

Особенности ариф. с пливающ(,).

+ и – двух чисел.

1)Производится выравнив-е порядков для этого выбир число с большим порядком,порядки двух чисел сравн-ся, на получившуюся разность мантисса яичла с меньш порядком сдвигается врпаво на число разрядов равное разности порядков.При этом возможно 5 случаев.

1)Px-Py=k>m m-разрядность мантиссы. Рез-т число х

2)Py-Px=k> . Рез-т число у

![]() 3)Px-Py=0

3)Px-Py=0

4)Px-Py=k≤m .Порядок рез-т Px

5)Py-Px=k≤m => Py

Мантиссы обр. по правилам арифм с фиксир (,). Рез-ту присв верхн порядок затем начинается нормализация.

Умножение Мантиссы перемнож-ся по првилам ариф. с фикс (,) произвед-ю присв порядок = ∑ порядков сомножителей.

Деление Мантиссы делятся по правил ариф с фиксир (,) а частному присваивается порядок = разности порядков.

6.Многофункциональное алу

Аппаратн затраты многофукц АЛУ позволяют: 1)Выолн опер + - * / чисел с фикс(,) 2)Операции лог обр-ки ( и,или,слож по модулю два) операндов 3)Использ Рг С и D для обработки порядков позвол выполнять операции арифм с плавающ(,).

Это все достигается только за счет различных последовательностей упр возд-й (yi) разные микропрограммы управления.

7.Управляющие автоматы с жесткой логикой

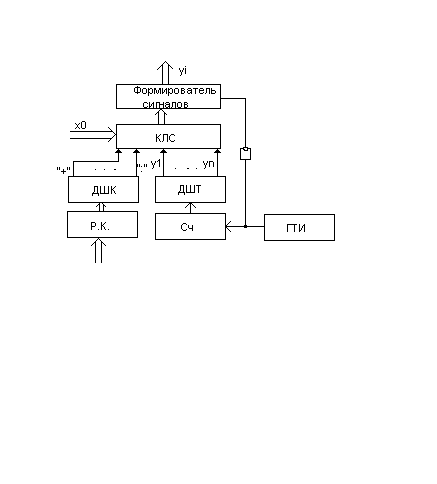

КЛС-комб.лог.схема ГТИ-генер.такт.имп ДШК-дш.команд

ДШТ-дш.тактов Р.К.-регистр ком.

Счетчик имеет коэфф пересчета = числу упр воздействий yn самой длинной ком-де,напр деление, для более коротких команд, напр + упр возд-я получаются из общего числа yn путем блокировки КЛС yi не участвующих в в выполн данной ком-ды, код ком-ды записыв в Р.К., ДШК опред тип выполн ком-ды и его выход в КЛС разрешает в КЛС прохождение только тех yi которые требуются при выполн данной ком-ды, особенность упр. авт-та с жестк лог-й все ком-ды выполн за одинаковое кол-во тактов соотв самой длинной ком-де. Если изм-ся микропрогр упр-е для выполн какой –либо одной ком-ды необходимо пересчитывать или пересинтезировать КЛС.

Условно по длительн-ти выполн все команды процессора делятся на группы (в данном случае на 2-короткие и длинные) кор=+/- лог, длинные = ком.использ.СЧ.циклов * и / итд.

Схема распр-анализир код ком и вкл Сч1 с небольшим числом упр возд yi если ком-да относится к коротким и Сч2 если ком длинная.