- •1.Процессоры. Иерархия языков вт

- •Иерархия языков вт

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •4.Алу для деления чисел с фиксир(,)

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •8.Управл автоматы с мпу

- •9.Требования к кодам команди способы кодирования.

- •11.Шинные формирователи и рег-ры. Орг см 580 серии

- •Организация см процессора

- •12.Организация модулей пзу

- •13.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •14.Организация динамических модулей дозу

- •15.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •16.Синхр способ продкл ву к см

- •17.Асинхр способ продкл ву к см

- •18.Организация кэш памяти.

- •19.Организация виртуальной памяти.

- •20.Общие полож.Risc-проц.Берклинская арх.

- •21.Старнфордсая структура

- •22.Машины упр потоками данных(df-машины)

- •23.Pentium

- •24.Pentium II,Pentium Pro

- •25.Pentuim VI

- •27.М/о ч/з ппи.

- •28.Усапп

- •29.Контролер пдп.

- •30.Прогр контр прерываний.

- •31.Таймер

- •32.Орг эвм типа ibm pc at

- •33,Однокристальн эвм

- •34.Протокол обмена подкл озу/пзу mcs-51

- •35.ATmega 32

- •36.Классификация оэвм по табл

- •35.Вс классификация по Флинну

- •38.Производительность эвм и сетей.

- •38.Типовые структуры вс

- •40.Архитектура Сммр,Сvмр,См.

- •41.Сm структура.

- •42. Понятие интерфейса. Виды арбитража

- •43.Арбитраж по последовательному опросу.

- •44. Контроллер прерываний по последовательному опросу

- •45.Арбитраж по || опросу.

- •46.Синхронизация информации в интерф.

43.Арбитраж по последовательному опросу.

Счетчик имеет коэф-т пересчета N равный числу машин, нуждающихся в общем ресурсе. ДШ подключается к параллельному выходу счетчика, который в конкретный момент имеет только 1 возбужденный выход. Счетчик считает от 0 до N, переполняется, сбрасывается в 0, и 1-ца (маркер) на выходе ДШ бегает по кругу. Пусть ЭМ1 выставила запрос, когда маркер попадает на вход элемента i1 на выходе 1-ца, которая проходит ч/з «или» и блокирует поступление тактовых импульсов на вход счетчика. Одновременно выход элемента «и» есть разрешение для ЭМ1. Получив Р1 ЭМ1 работает с СМ. В каждый мом-т времени маркер может находится только на одном элементе «и» и разрешение м.б. выдано только одной ЭМ. По окончании с СМ ЭМ убирает запрос и на выходе «и» - 0. Вход счетчика разблокируется и маркер побежал дальше.

44. Контроллер прерываний по последовательному опросу

Работа аналогична предыдущему случаю, только выход Эл-та «или» записывает в триггер сигнал INT(запрос на прерывание) для ЦП. ЦП в подпрограмме обработки прерыв обращается по адресу CS1 и считывает ч/з ШФ номер устройства, запросившего прерывание. В конце подпрограммы обработки прерываний, ЦП обращается по CS0 и сбрасывает триггер с запросом на прерывание(счетчик разблокируется и контроллер снова готов к работе)

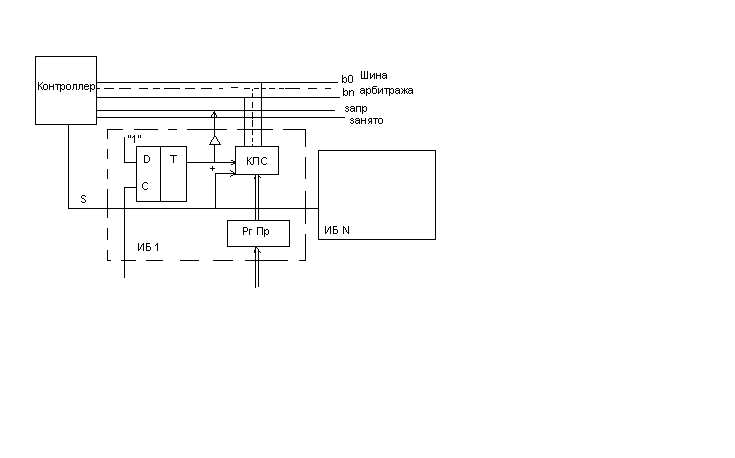

45.Арбитраж по || опросу.

Ш арбитража построена по принципу монтажного «или» любая 1 на выходе ставит bi в 1.

В регистр приоритета записывается код приоритета (max приоритет все единички).

|

ai |

bi |

ci |

|

0 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

нет |

щий разряд.

3 строка – устр-во выбыло из кон-курса.

4 строка –невозм-я комбинация

КЛС работает в соответствии с таблицей. Если после анализа старшего разряда СN =1, это означает, что устр-во имеет высший приоритет из всех уч-щих в конкурсе и подключ-х к СМ. Если в процессе сравнения приоритетов Сi =0, устройство выбывает из конкурса. Анализ всех разрядов Ai во всех интерфейсных блоках идет параллельно. Высокое быстродействие, высокие затраты, в кач-ве арбитров исп-ся обычные однокристалки.

46.Синхронизация информации в интерф.

Различают синхронизацию :

1)битов в слове при послед протоколах обмена или || шинах данных.

Разное быстродействие отдельных битов в слове.

2)Синхронизация слов

![]()

3)Синхронизация пакетов.

Синхр слов спомощью сигнала идентификации

Одноступенчатая обр связь

Двухступенчатая обр связь

Если ВУ готово принимать инф оно выставляет сигнал готовности приемника. Инициатором обмена явл ВУ. Оно выст сигнал готовности приемн, потом выставл сигнал о том что данные поступили.