- •1.4.2 Передатна характеристика

- •1.4.3 Швидкість наростання вихідного сигналу

- •2) Комутація пакетів

- •Iнтерполяцйне розділення - штучно збльшена розрізнювальна здатність сканера досягаться програмним шляхом в драйвер сканера за допомогою математичних алгоритмв.

- •1.4. Архітектура мікропроцесорних систем

- •2.5. Модель osi і реальні протоколи

- •1. Класифікація та характеристики сучасних пзп

- •2 Програмний обмін інформацією

- •3 Обмін за перериваннями

- •4 Обмін з використанням прямого доступу до пам'яті

- •2) Комутація пакетів

- •3.3.3. Формати кадрів технології Ethernet

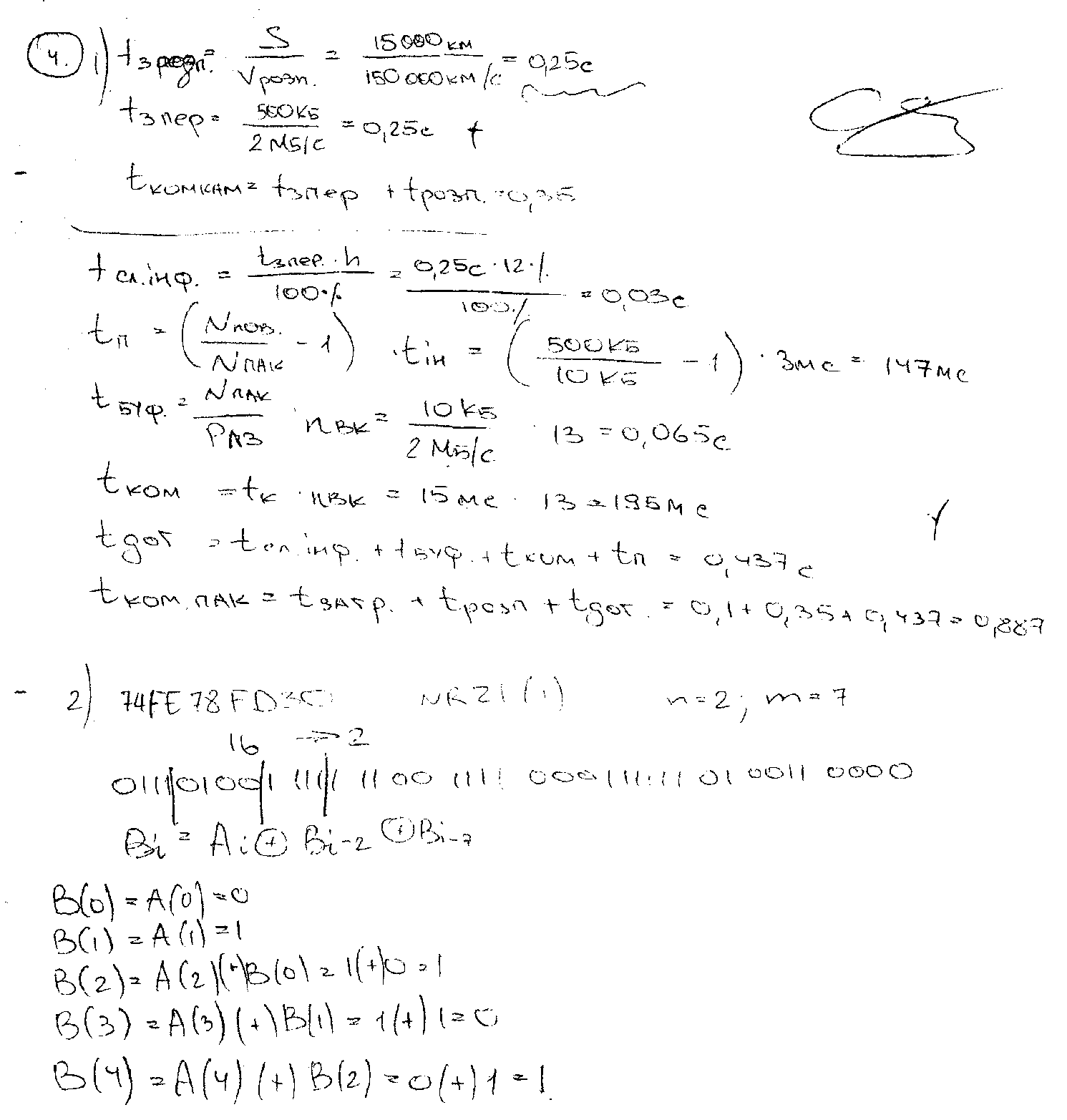

- •4. Для даних, що передаються через комп’ютерну мережу виконати такі дії:

- •3.4. Множення чисел з плаваючою комою

- •4. Для даних, що передаються через комп’ютерну мережу виконати такі дії:

- •100Base-t4 для кабелю з чотирьох пар на неекранованій кручений парі utp категорії 3, 4 чи 5;

- •100Base-t4 — 4 пари категорії 3;

- •003Ffh) і кінцеві (ffff0h-fffffh) адреси зарезервовані для системи

- •Ip; зміщення в сегменті даних і додатковому сегменті даних - ефективною

- •4. Синтезувати схему керуючого автомата для закодованої граф – схеми алгоритму:

- •4. Для даних, що передаються через комп’ютерну мережу виконати такі дії:

- •4. Для даних, що передаються через комп’ютерну мережу виконати такі дії:

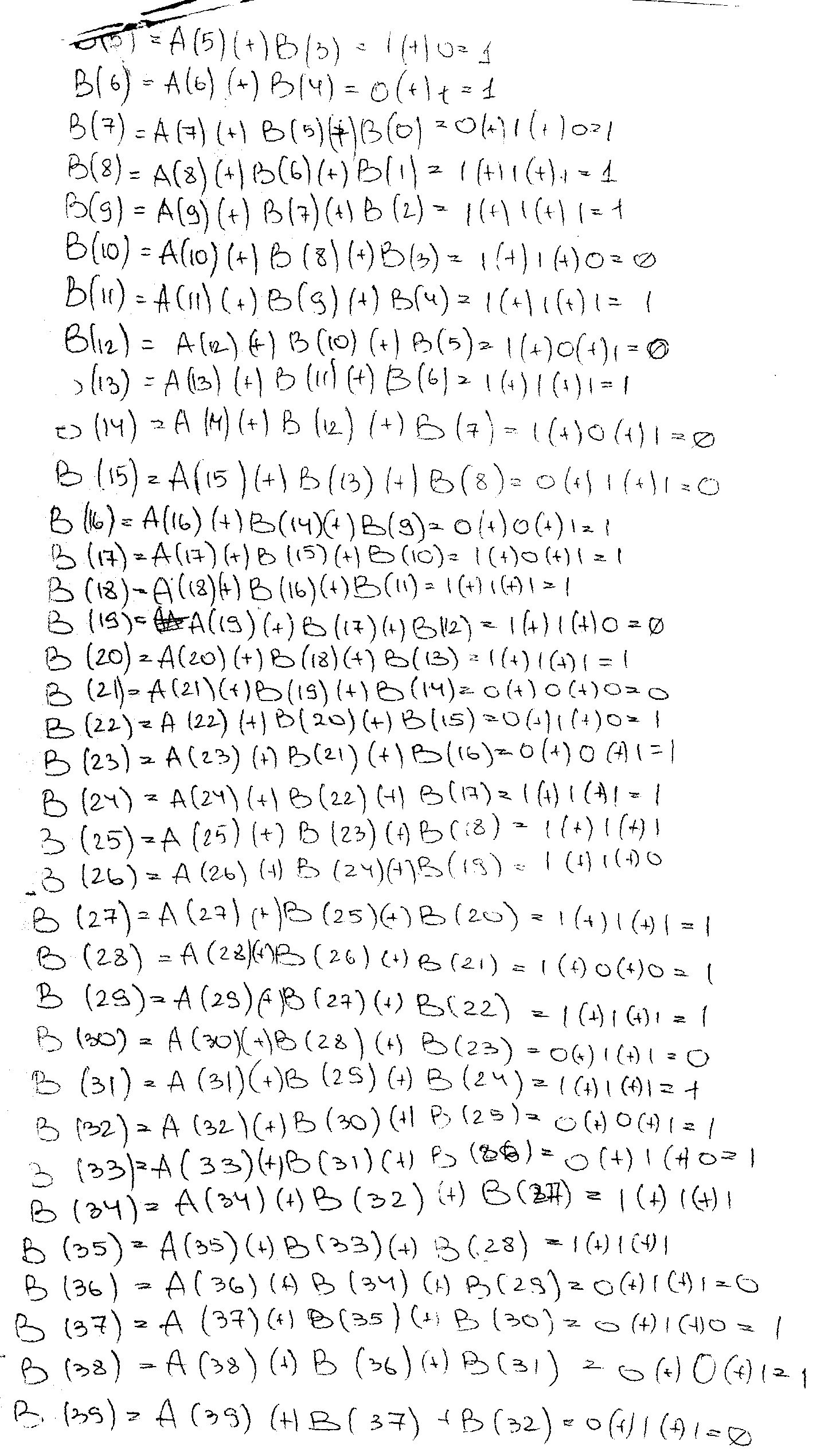

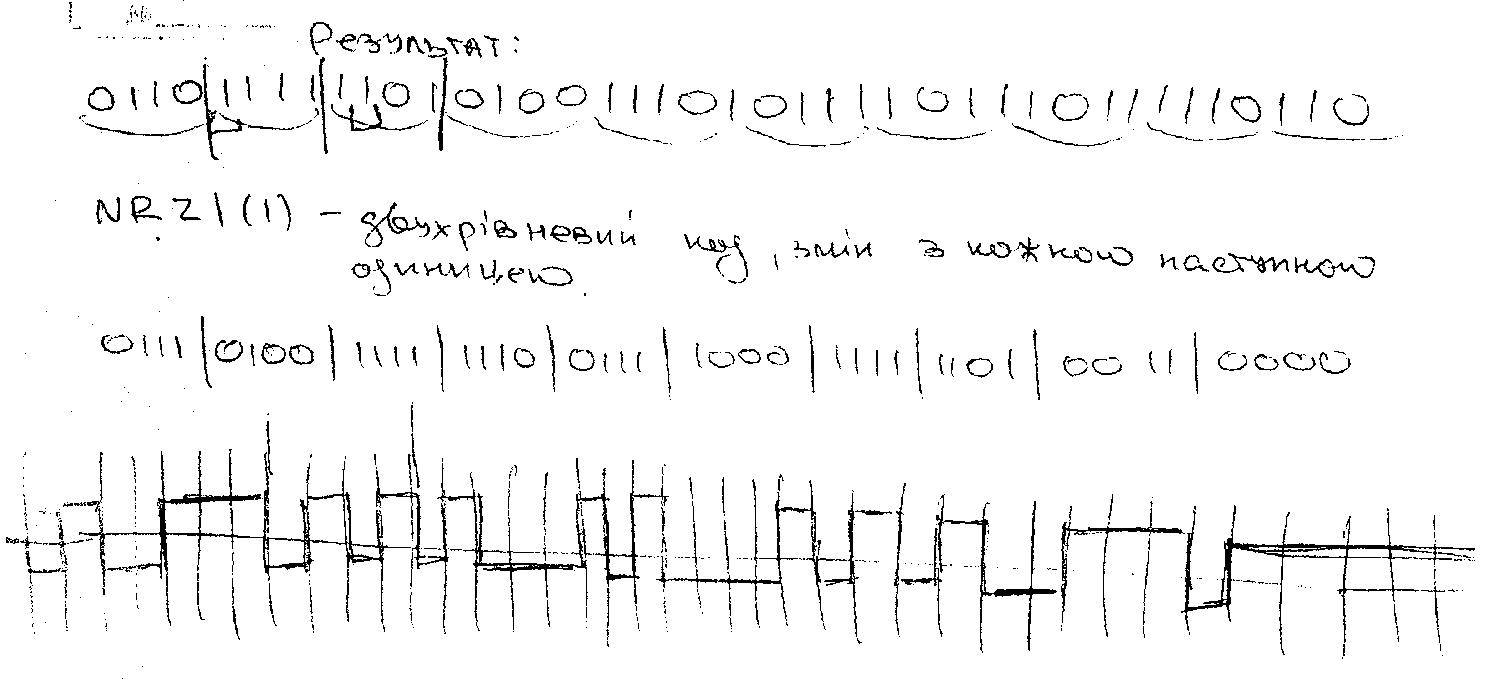

- •4. Для даних, що передаються через комп’ютерну мережу виконати такі дії:

- •4. Синтезувати схему керуючого автомата для закодованої граф – схеми алгоритму:

- •4. Синтезувати схему керуючого автомата для закодованої граф – схеми алгоритму:

3.4. Множення чисел з плаваючою комою

Для чисел

і

і

,

що представлені в формі з плаваючою

комою, добуток обчислюється за формулою:

,

що представлені в формі з плаваючою

комою, добуток обчислюється за формулою:

,

,

де

,

,

.

.

Звідси випливає, що процес множення складається з чотирьох етапів:

множення мантис;

додавання порядків;

нормалізація й округлення мантиси добутку;

корегування порядку добутку.

Перші два етапи можуть виконуватись одночасно, оскільки вони незалежні один від одного. При цьому множення мантис може бути здійснене будь-яким з розглянутих методів множення.

У загальному випадку результат множення мантис може бути одержаний в ненормалізованій формі. Причому порушення нормалізації можливо тільки зліва. Воно усувається шляхом зсуву коду мантиси на один розряд вліво і, відповідно, корегується порядок добутку шляхом віднімання одиниці від суми порядків. Округлення мантиси здійснюється додаванням одиниці до (п+1)-го розряду.

Під час виконання операції множення чисел з плаваючою комою можуть мати місце такі особливі випадки.

Якщо порядок результату є найбільшим від'ємним числом, то необхідно формувати машинний нуль.

Коли виникає переповнення додатного порядку і воно не усувається після нормалізації і корегування порядку, то необхідно формувати ознаку переповнення порядку.

Ці особливі випадки можна передбачити в алгоритмі операції множення введенням корегування добутку на підставі ознак результату.

Особливості ділення чисел з плаваючою комою

Для чисел і , що представлені в формі з плаваючою комою, частка визначається за формулою:

де

,

,

.

.

Звідси випливає, що процес ділення складається з чотирьох етапів:

ділення мантис;

віднімання порядків;

нормалізація мантиси частки;

корегування порядку частки.

Перші два етапи можуть виконуватись

одночасно, оскільки вони незалежні один

від одного. При цьому ділення мантис

повністю співпадає з діленням чисел,

що представлені в формі з фіксованою

комою. Відміна полягає лише в тому, що

мантиси операндів можуть співвідноситись

одна з одною довільно. Оскільки мантиси

діленого і дільника - нормалізовані

числа, то можливі такі випадки:

;

;

.

.

Коли мантиса діленого більше або дорівнює мантисі дільника, то на початку ділення одержується цифра частки, що дорівнює 1 і яка записується в цілу частину частки. Решта дій над мантисами аналогічні діям над числами, що представлені в формі з фіксованою комою. Одержана при цьому мантиса частки буде мати порушення нормалізації праворуч. Воно усувається шляхом зсуву коду мантиси на один розряд управо і, відповідно, корегується порядок частки шляхом додавання одиниці до різниці порядків.

Коли мантиса діленого менше мантиси дільника, то на початку ділення одержується цифра частки, що дорівнює 0 і яка записується в цілу частину частки. Далі ділення мантис продовжується за правилами ділення чисел, що представлені в формі з фіксованою комою. Одержана при цьому мантиса частки буде мати нормалізовану форму.

Під час виконання операції ділення чисел з плаваючою комою можуть мати місце такі особливі випадки.

Якщо дільник дорівнює нулю, то формується сигнал "Зупинка машини".

Оскільки в процесі ділення порядки віднімаються, то можливе переповнення розрядної сітки порядків. Коли виникає переповнення в бік від'ємних значень порядку і воно не усувається після нормалізації і корегування порядку, то мантисі результату приписується машинний нуль, а порядку - найбільше від'ємне число.

У разі переповнення додатного порядку необхідно формувати ознаку переповнення порядку.

Ці особливі випадки можна передбачити в алгоритмі операції ділення введенням аналізатора дільника на нуль і корегування частки на підставі ознак результату.

Інтерфейс RS-232C

Інтерфейс RS-232C призначений для підключення до комп'ютера стандартних зовнішніх пристроїв (принтера, сканера, модему, миші й ін.), а також для зв'язку комп'ютерів між собою. Основними перевагами використання RS-232C у порівнянні з Centronics є можливість передачі на великі відстані (за стандартом довжина кабелю може доходити до 15 метрів) і набагато більш простий кабель (з меншою кількістю проводів). У той же час працювати з RS-232C трохи складніше. Дані в інтерфейсі RS-232C передаються в послідовному коді (біт за бітом) побайтно. Кожен байт обрамляється стартовим і стоповими бітами. Дані можуть передаватися як в одну, так і в іншу сторону по різними проводами (дуплексний режим). Швидкість передачі - до 14,4 Кбайт/з (115,2 Кбит/с).

Комп'ютер має 25-контактний роз'єм (типу DB25P) чи 9-контактний роз'єм (типу DB9P) для підключення кабелю інтерфейсу RS-232C. Призначення контактів роз'єму наведене в табл. 8.8 (у таблиці застосовані позначення: I - вхідний сигнал комп'ютера, O - вихідний сигнал комп'ютера).

Табл. 8.8. Призначення контактів роз'ємів інтерфейсу RS-232C. |

|||

Сигнал |

Контакт DB25P |

Контакт DB9P |

I/O |

FG |

1 |

– |

– |

-T x D |

2 |

3 |

O |

-R x D |

3 |

2 |

I |

RTS |

4 |

7 |

O |

CTS |

5 |

8 |

I |

DSR |

6 |

6 |

I |

SG |

7 |

5 |

– |

DCD |

8 |

1 |

I |

DTR |

20 |

4 |

O |

RI |

22 |

9 |

I |

Призначення сигналів інтерфейсу RS-232C наступне:

FG - захисне заземлення (екран).

-Tx - дані, передані комп'ютером у послідовному коді (логіка негативна).

-Rx - дані, прийняті комп'ютером у послідовному коді (логіка негативна).

RTS - сигнал запиту передачі. Активний на протязі всього часу передачі.

CTS - сигнал скидання (очищення) для передачі. Активний на протязі всього часу передачі. Говорить про готовність приймача.

DSR - готовність даних. Використовується для задавання режиму модему.

SG - сигнальне заземлення, нульовий провід.

DCD - виявлення несучої даних (детектування прийнятого сигналу).

DTR - готовність вихідних даних.

RI - індикатор виклику. Говорить про прийом модемом сигналу виклику з телефонної мережі.

Найчастіше використовується трьох- чи чотирьохпровідний зв'язок (для двонапрямленої передачі). Схема з'єднання двох пристроїв при чотирьохпровідній лінії зв'язку показана на Рис. 8.8.

Рис.

8.8. Схема чотирьохпровідної лінії зв'язку

для RS-232C.

Рис.

8.8. Схема чотирьохпровідної лінії зв'язку

для RS-232C.

Для двохпровідної лінії зв'язку у випадку передачі з комп'ютера в зовнішній пристрій використовуються сигнали SG і Tx. Усі 10 сигналів інтерфейсу задіюються тільки при з'єднанні комп'ютера з модемом.

Формат переданих даних показаний на рис. 8.9. Власне дані (містять 5, 6, 7 чи 8 біт) супроводжуються стартовим бітом, бітом парності й одним чи двома стоповими бітами. Одержавши стартовий біт, приймач вибирає з лінії біти даних через визначені інтервали часу. Дуже важливо, щоб тактові частоти приймача і передавача були однаковими (допустима розбіжність - не більше 10%). Швидкість передачі по RS-232C може вибиратися з ряду: 110, 150, 300, 600, 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200 біт/с.

Усі сигнали RS-232C передаються спеціально обраними рівнями, що забезпечують високу завадостійкість зв'язку (Рис. 8.10). Відзначимо, що дані передаються в інверсному коді (логічній одиниці відповідає низький рівень, логічному нулю - високий рівень).

Обмін по RS-232C здійснюється комп'ютером за допомогою звертань за спеціально виділеними для цього портах COM1 (адреси 3F8...3FF, переривання IRQ4), COM2 (адреси 2F8...2FF, переривання IRQ3), COM3 (адреси 3E8...3EF, переривання IRQ10), COM4 (адреси 2E8...2EF, переривання IRQ11).

Рис.

8.9. Формат даних RS-232C.

Рис.

8.9. Формат даних RS-232C.

Рис.

8.10. Рівні сигналів RS-232C на передаваючому

і приймаючому кінцях лінії зв'язку.

Рис.

8.10. Рівні сигналів RS-232C на передаваючому

і приймаючому кінцях лінії зв'язку.

Для реалізації інтерфейсу застосовуються мікросхеми універсальних асинхронних прийомопередавачів (УАПП, UART - Universal Asynchronous Receiver/Transmitter) типу i8250, 16550А чи їх аналоги. Комп'ютер за допомогою посилки керуючих кодів може вибрати швидкість обміну, формат переданих посилок (кількість бітів даних, перевірка парності, використання стопових бітів), дозволити чи заборонити переривання, а також встановити чи скинути керуючі сигнали. Є також можливість прочитати слово стану UART для визначення джерела переривання чи станів прапорів.

USB (англ. Universal Serial Bus, абревіатура читається ю-ес-бі) — укр. універсальна послідовна шина, призначена для з'єднання периферійних пристроїв. Символом USB є чотири геометричні фігури: квадрат, трикутник, велике коло та мале коло.

Шина USB представляє собою послідовний інтерфейс передавання даних для середньо швидкісних та низько швидкісних периферійних пристроїв. Для високошвидкісних пристроїв на сьогодні кращим вважається FireWire.

USB-кабель представляє собою дві звиті пари: по одній парі відбувається передавання даних в кожному напрямку (диференціальне включення), а інша пара використовується для живлення периферійного пристрою (+5 В). Завдяки вбудованим лініям живлення, що забезпечують струм до 500 мА, USB часто дозволяє використовувати пристрої без власного блоку живлення (якщо ці пристрої споживають струм потужністю не більше 500 мА).

Поєднання USB-кабелями формує інтерфейс між USB-пристроями та USB-хостом. В якості хоста використовується керований з операційної системи USB-контролер, до складу якого входить USB-концентратор, або ж хаб. Цей хаб є відправною точкою у створенні ланцюжка пристроїв, що відповідають вимогами топології «зірка». Він має спеціальну назву — кореневий концентратор. До його портів під'єднується інше USB-приладдя та зовнішні хаби. Загальні їх кількість не може перевищувать 127 пристроїв, увімкнених не більш ніж у п'ять каскадів, не рахуючи рівень кореневого хаба.

Зміст [сховати] 1 Історія 2 USB пререлізи 3 USB 1.0 3.1 USB 1.1 4 USB 2.0 4.1 USB OTG 4.2 Бездротовий USB 5 USB 3.0 6 Посилання |

[ред.] Історія

Стандарт розробили сім компаній: «Compaq», «Digital Equipment», IBM, Intel, «Microsoft», NEC и «Northern Telecom». Влітку 1996 року на ринку з'явилися перші комп'ютери з портами USB.

[ред.] USB пререлізи

Починаючи з листопада 1994 до листопада 1995 року було анонсовано кілька версій протоколу (USB 0.7, 0.8, 0.9, 0.99, 1.0 Release Candidate).

[ред.] USB 1.0

Версія представлена в січні 1995 року.

Технічні характеристики:

високошвидкісне з'єднання — 12 Мбіт/с

максимальна довжина кабелю для високошвидкісного з'єднання — 3 м

низькошвидкісне з'єднання — 1,5 Мбіт/с

максимальна довжина кабелю для низькошвидкісного з'єднання — 5 м

максимальна кількість пристроїв підключення (враховуючи концентратори) — 127

можливість підключення пристроїв з різними швидкостями обміну інформацією

напруга живлення для периферійних пристроїв — 5 В

максимальний струм споживання на один пристрій — 500 мА

[ред.] USB 1.1

Випущено в вересні 1998. Виправлені проблеми виявлені у версії 1.0, в основному пов'язані з концентраторами.

[ред.] USB 2.0

![]()

Версія випущена в квітні 2000 року. USB 2.0 відрізняється від USB 1.1 лише швидкістю передачі, яка зросла та незначними змінами в протоколі передачі даних для режиму Hi-speed (480 Мбіт/сек). Існує три швидкості роботи пристроїв USB 2.0:

Low-speed 10—1500 Кбіт/c (використовується для інтерактивних пристроїв: клавіатури, мишки, джойстики)

Full-speed 0,5—12 Мбіт/с (аудіо/відео пристрої)

Hi-speed 25—480 Мбіт/с (відео пристрої, пристрої зберігання інформації)

В дійсності ж хоча швидкість USB 2.0 і може досягати 480Мбіт/с, пристрої типу жорстких дисків чи взагалі будь-які інші носії інформації ніколи не досягають її по шині USB, хоча і могли б. Це можна пояснити доволі просто, шина USB має доволі велику затримку між запитом на передачу інформацію і самою передачею даних («довгий ping»). Наприклад шина FireWire забезпечує максимальну швидкість у 400 Мбіт/с, тобто на 80Мбіт/с менше чим у USB, дозволяє досягнути більшої швидкості обміну даними з носіями інформації.

USB 3.0

В листопаді 2008 року робоча група USB 3.0 Promoter Group заявила про завершення робіт над специфікацією нового високошвидкісного інтерфейсу USB 3.0, названого SuperSpeed USB. USB 3.0 є наступним етапом еволюції добре відомою нам всім технології USB. Новий інтерфейс забезпечує максимальну швидкість передачі даних в 10 разів більшу, ніж USB 2.0 (тобто 10 × 480 Мбіт/с = 4,8 Гбіт/с). Друга важлива властивість — покращені показники енергоефективності. Крім того, розробниками заявлена зворотна сумісність USB 3.0 з ранішими версіями USB. Докладніші відомості можна черпнути з опублікованих специфікацій (редакція 1.0).

SATA (англ. Serial ATA) — послідовний інтерфейс обміну даними з накопичувачами інформації (як правило, з жорсткими дисками). SATA є розвитком інтерфейсу ATA (IDE), який після появи SATA був перейменований в PATA (Parallel ATA).

За даними аналітиків IDC, в 2008 році диски S-ATA склали 98% від всіх продажів дисків в світі[1].

Зміст [сховати] 1 SATA/150 2 SATA/300 3 SATA 3.0 4 Опис SATA 5 Роз'єми SATA 6 eSATA 7 SAS 8 Виcновки 9 Посилання |

[ред.] SATA/150

На початку стандарт SATA передбачав роботу шини на частоті 1,5 ГГц, що забезпечує пропускну здатність приблизно в 1,2 Гбіт/с (150 МБ/с). (20%-а втрата продуктивності пояснюється використанням системи кодування 8B/10B, при якій на кожні 8 біт корисної інформації припадає 2 службових біта). Пропускна здатність SATA/150 незначно вище пропускної здатності шини Ultra ATA (UDMA/133). Головною перевагою SATA перед PATA є використання послідовної шини замість паралельної. Попри те, що послідовний спосіб обміну принципово повільніше паралельного, у цьому випадку це компенсується можливістю роботи на більш високих частотах за рахунок більшої перешкодостійкості кабелю. Це досягається 1) меншим числом провідників й 2) об'єднанням інформаційних провідників в 2-і виті пари, екрановані заземленими провідниками.

[ред.] SATA/300

Стандарт SATA/300 працює на частоті 3 ГГЦ, забезпечує пропускну здатність до 2,4 Гбіт/c (300 МБ/с). Уперше був реалізований у контролері чипсету nForce 4 фірми NVIDIA. Досить часто стандарт SATA/300 називають SATA ІІ. [2] Теоретично SATA/150 й SATA/300 пристрої повинні бути сумісні (як SATA/300 контролер і SATA/150 пристрій, так і SATA/150 контролер й SATA/300 пристрій) за рахунок підтримки узгодження швидкостей (у меншу сторону), однак для деяких пристроїв і контролерів потрібне ручне виставляння режиму роботи (наприклад, на жорсткому диску фірми Seagate, що підтримують SATA/300, для примусового включення режиму SATA/150 передбачений спеціальний джампер).

Стандарт SATA передбачає можливість збільшення швидкості роботи до 600МБ/с (6 ГГц).

[ред.] SATA 3.0

Serial ATA International Organization (SATA-IO), відповідальна за розвиток послідовного інтерфейсу, в травні 2009 опублікувала специфікації стандарту SATA 3.0[3], здатного передавати дані на швидкості до 6 Гбіт/с, удвічі вище в порівнянні з SATA 2. Специфікація була обнародувана в серпні 2008 і допрацьовувалася до травня 2009. Після публікації специфікації виробники дістали можливість використовувати SATA-3 в комерційних продуктах. Новий стандарт сумісний назад з існуючими версіями SATA, але разом з цим пропонує зручніший роз'єм для підключення компактних 1,8-дюймових дисків і SSD. Покращена передача мультимедійних файлів. Істотних змін в інтерфейсі нема — максимальна довжина кабелю складає 1 метр, причому роз'єми будуть сумісні з ранніми версіями SATA. Проте крім збільшення швидкісних показників також реалізована підтримка додаткового набору команд, які призначені для підвищення ефективності при передачі відео потоку. Підвищення швидкісних показників інтерфейсу передачі даних приведе до підвищення споживаної потужності, але з іншого боку, це приведе до прискореного переходу на нові технології виготовлення управляючих мікросхем.

[ред.] Опис SATA

SATA використовує 7-контактний роз'єм замість 40-контактного роз'єму в PATA. SATA-кабель має меншу ширину, за рахунок чого зменшується опір повітрю, що обдуває компоненти комп'ютера; поліпшується охолодження системи.

SATA-кабель за рахунок своєї форми більш стійкий до багаторазового підключення. Шнур живлення SATA так само розроблений з урахуванням багаторазових підключень. Роз'єм живлення SATA подає 3 напруги: +12 В, +5 У и +3,3 В; однак сучасні пристрої можуть працювати без напруги +3,3 В, що дає можливість використати пасивний перехідник зі стандартного роз'єму IDE на SATA. Ряд SATA пристроїв поставляється із двома роз'ємами живлення: SATA й Molex.

Стандарт SATA відмовився від традиційного для PATA підключення двох пристроїв на шлейф; кожному пристрою надається окремий кабель, що знімає проблему неможливості одночасної роботи пристроїв, що перебувають на одному кабелі (і затримок, що виникали звідси), зменшує можливі проблеми при збиранні (проблема конфлікту Slave/Master пристроїв для SATA відсутній), усуває можливість помилок при використанні нетермінованих PATA-шлейфів.

Стандарт SATA передбачає гарячу заміну пристроїв і функцію черги команд (NCQ).

Таблиця 1.

Vроз (км/с) |

Pлз (Мб/с) |

S (км) |

h(%) |

t інт (мс) |

N пов (Кб) |

Nпак (Кб) |

t ком (мс) |

n |

150000 |

2 |

15000 |

12 |

3 |

500 |

10 |

15 |

13 |

Таблиця 2.

N |

A |

Цифрове кодування |

Скремблер |

6 |

74FE78FD30 |

NRZI (1) |

n=2; m=7 |

БІЛЕТ № 11

Метод доступу до середовища CDMA.

Архітектура мікропроцесорної системи AVR.

Транзисторно-транзисторна логіка з діодами Шоткі.

Використовуючи класи об’єктної бібліотеки MFC створити інтерфейсну програму в середовищі Windows, яка реалізує задану форму меню (рис.1) і функції-обробники окремих пунктів меню. Складену програму виконати на комп’ютері і перевірити правильність результату.

-

Пункт 1

Пункт 2

Пункт 3

Пункт 4

Пункт 5

Підпункт 1

Підпункт 2

Підпункт 3

CDMA (англ. Code Division Multiple Access, Множинний доступ із кодовим розподілом каналів) — одна з можливих технологій мультиплексування, тобто одночасної передачі даних у спільному діапазоні (так званому каналі) радіочастот.

Для забезпечення доступу до каналу багатьом користувачам — множинний доступ — дані кодуються спеціальним кодом, асоційованим із кожним каналом, і використовуються властивості конструктивної інтерференції спеціальних кодів, щоб здійснювати мультиплексування. Це є головною відміною методу CDMA від інших методів мультиплексування:

TDMA, де канал ділиться між користувачами за часом, чи

FDMA де розподіляються частоти.

[ред.] Використання

CDMA використовується у багатьох комунікаційних системах, наприклад:

Глобальна Система Позиціонування (GPS)

система позиціонування Galileo

супутникова система OmniTRACS для транспортної логістики.

[ред.] Подальший розвиток

На базі CDMA розроблено новий стандарт передачі даних W-CDMA для цифрових систем мобільної телефонії т.зв. 3-го покоління (3G) UMTS (подекуди вживається позначення 3GSM).

Лідером на ринку цієї технології вважається фірма Qualcomm (США), котрій належать основні патенти на технологію CDMA. Нею також розроблено стандарт CDMA2000.

Фірми Alcatel Shanghai Bell та Datang Mobile спільно розробили (з листопада 2001 по серпень 2005) третій стандарт — TD-SCDMA, котрий планують використовувати на китайському ринку.

[ред.] Технічні деталі

В основі CDMA лежить технологія передачі SST (DH-SS Direct Sequence Spread Spectrum), коли інформація ніби «розмазується» по широкому спектру частот. Послідовність інформаційних бітів множать на псевдовипадкову послідовність коротких імпульсів. Одержують сигнал у ширшому частотному діапазоні значно меншої інтенсивності. Для декодування такої послідовності потрібно знати псевдовипадкову послідовність, яку використовували під час передачі. Цей механізм кодування забезпечує:

захист сигналу від підслуховування. Треба знати псевдовипадкову послідовність-ключ. Цим пояснюють широке використання цього підходу військовими та стільниковими мережами;

захист сигналу від перешкод. Широкосмуговість сигналу дає змогу просто поновлювати сигнал, особливо якщо перешкоди вузькосмугові. Так само сигнал захищений і від тимчасового зникнення на окремих частотах (фейдинг (fading));

широкосмугове передавання та ліпший захист від завад дають змогу зменшити потужність передавачів, збільшити час дії акумуляторів та дещо зменшити шкідливий вплив цієї технології на здоров'я людини;

дві абонентські станції, які працюють у межах одної стільникової комірки на однаковій частоті з використанням різних кодових послідовностей, практично не створюють перешкод одна одній.

Тому для станцій, які працюють у межах однієї комірки, відведено спільний частотний діапазон завширшки 1,25 МГц, а також фрагменти спільної псевдовипадкової кодової послідовності (зі своїм зсувом від початку).

У мережі CDMA параметри розміру комірки, якості передавання та кількості каналів взаємозалежні. Наприклад, чим більше каналів у комірці, тим більше взаємних перешкод через неповну незалежність кодових послідовностей і тим гірша якість передачі. Чим більший розмір комірки, тим слабший корисний сигнал і тим меншим повинен бути рівень перешкод. Емпіричним шляхом визначено, що в одному частотному діапазоні 1,25 МГц можна розмістити до 18 каналів для мобільних та 30 каналів для стаціонарних користувачів. Це майже у дев'ять разів більше, ніж у мережах AMPS.

Ще однією перевагою CDMA є можливість використання у сусідніх комірках одного й того ж частотного діапазону, що полегшує планування мережі та збільшує кількість каналів. Особливістю, яка поліпшує якість передавання у CDMA-мережах, є механізм обробки переходу абонента з однієї комірки до іншої. В інших технологіях під час такого переходу спочатку розривається зв'язок з однією базовою станцією, а потім налагоджується з іншою (hard handoff, break before make). Це знижує якість передачі. У технології CDMA завдяки збереженню однієї частоти-носія у сусідніх комірках можна спочатку налагодити сполучення з новою станцією, а вже потім розірвати з попередньою. Це поліпшує якість переходу і дає змогу опрацювати передачу у «прикордонній зоні», коли передавач може багато разів переходити зі сфери діяльності однієї базової станції до іншої та назад.

Мережі технології CDMA сьогодні активно впроваджують не лише у традиційній сфері стільникового зв'язку, а й у частотному діапазоні PCS, виділеному для роботи як телефонів, так і іншого обладнання персонального зв'язку. Вони перевершують інші технології за якістю передавання та кількістю каналів. Наприклад, для CDMA потрібно на 30-40% менше базових станцій, ніж для аналогічних мереж GSM та у два-три рази менше станцій, ніж для мереж AMPS. Водночас вартість обладнання CDMA внаслідок його складності сьогодні вища, ніж аналогічного обладнання інших мереж. На вищих рівнях протоколу мережі передачі даних використовують спеціальні протоколи, орієнтовані на стільникову мережу.

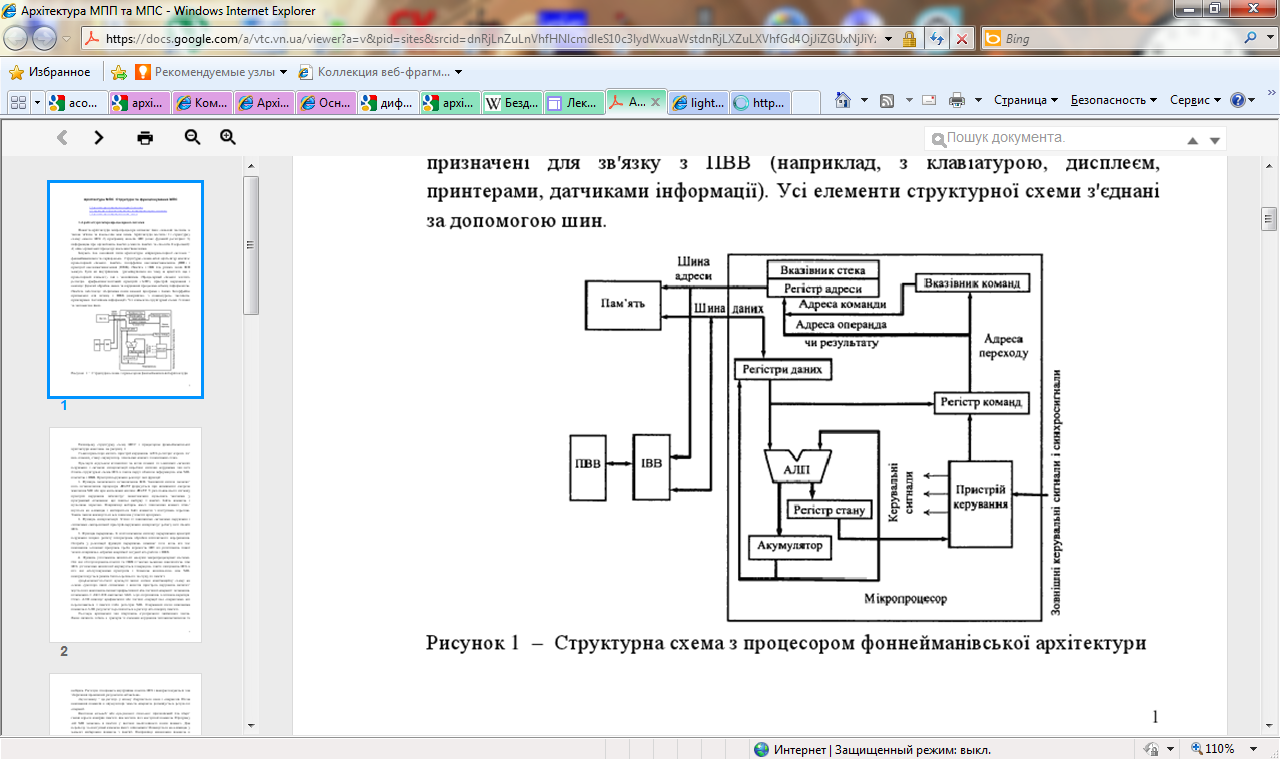

1 Архітектура мікропроцесорної системи

Поняття архітектури мікропроцесора визначає його складові частини, а

також зв'язки та взаємодію між ними. Архітектура містить: 1) структурну

схему самого МП; 2) програмну модель МП (опис функцій регістрів); 3)

інформацію про організацію пам'яті (ємність пам'яті та способи її адресації);

4) опис організації процедур введення-виведення.

Існують два основних типи архітектури мікропроцесорної системи –

фоннейманівська та гарвардська. Структурні схеми обох архітектур містять:

процесорний елемент, пам'ять, інтерфейси введення-виведення (ІВВ) і

пристрої введення-виведення (ПВВ). Пам'ять і ІВВ для різних типів МП

можуть бути як внутрішніми (розміщуватися на тому ж кристалі, що і

процесорний елемент), так і зовнішніми. Процесорний елемент містить

регістри, арифметико-логічний пристрій (АЛП), пристрій керування і

виконує функції обробки даних та керування процесами обміну інформацією.

Пам'ять забезпечує зберігання кодів команд програми і даних. Інтерфейси

призначені для зв'язку з ПВВ (наприклад, з клавіатурою, дисплеєм,

принтерами, датчиками інформації). Усі елементи структурної схеми з'єднані

за допомогою шин.

Рисунок 1 – Структурна схема з процесором фоннейманівської архітектури

Розширену структурну схему МПС з процесором фоннейманівської

архітектури наведено на рисунку 1.

Схема процесора містить пристрій керування, АЛП, регістри: адреси, да-

них, команд, стану, акумулятор, лічильник команд та вказівник стека.

Пристрій керування відповідно до кодів команд та зовнішніх сигналів

керування і сигналів синхронізації виробляє сигнали керування для всіх

блоків структурної схеми МП, а також керує обміном інформацією між МП,

пам'яттю і ПВВ. Пристрій керування реалізує такі функції:

1. Функція початкового встановлення МП. Зовнішній сигнал початко-

вого встановлення процесора RESET формується при ввімкненні джерела

живлення МП або при натисканні кнопки RESET. У разі появи цього сигналу

пристрій керування забезпечує завантаження нульового значення у

програмний лічильник, що ініціює вибірку з пам'яті байта команди з

нульовою адресою. Наприкінці вибірки вміст лічильника команд збіль-

шується на одиницю і вибирається байт команди з наступною адресою.

Таким чином виконується вся записана у пам'яті програма.

2. Функція синхронізації. Згідно із зовнішніми сигналами керування і

сигналами синхронізації пристрій керування синхронізує роботу всіх блоків

МП.

3. Функція переривань. Із надходженням сигналу переривання пристрій

керування ініціює роботу підпрограми обробки відповідного переривання.

Потреба у реалізації функцій переривань виникає тоді, коли під час

виконання основної програми треба перевести МП на розв'язання іншої

задачі, наприклад, обробки аварійної ситуації або роботи з ПВВ.

4. Функція узгодження швидкодії модулів мікропроцесорної системи.

Під час обслуговування пам'яті та ПВВ із значно меншою швидкодією, ніж

МП, узгодження швидкодії вирішується генерацією тактів очікування МП, а

під час обслуговування пристроїв з більшою швидкодією, ніж МП,

використовується режим безпосереднього доступу до пам'яті.

Арифметико-логічний пристрій являє собою комбінаційну схему на

основі суматора, який сигналами з виходів пристрою керування налагод-

жується на виконання певної арифметичної або логічної операції: додавання,

віднімання, І, АБО, НЕ, виключне АБО, зсув, порівняння, десяткова корекція.

Отже, АЛП виконує арифметичні або логічні операції над операндами, які

пересилаються з пам'яті і/або регістрів МП. Одержаний після виконання

команди в АЛП результат пересилається в регістр або комірку пам'яті.

Регістри призначені для зберігання n-розрядного двійкового числа.

Вони являють собою п тригерів зі схемами керування читанням/записом та

вибірки. Регістри створюють внутрішню пам'ять МП і використовуються для

зберігання проміжних результатів обчислень.

Акумулятор – це регістр, у якому зберігається один з операндів. Після

виконання команди в акумуляторі замість операнда розміщується результат

операції.

Вказівник команду або програмний лічильник, призначений для збері-

гання адреси комірки пам'яті, яка містить код наступної команди. Програму

дій МП записано в пам'яті у вигляді послідовності кодів команд. Для

переходу до наступної команди вміст лічильника збільшується на одиницю у

момент вибирання команди з пам'яті. Наприкінці виконання команди в

лічильнику команд зберігається адреса наступної команди.

Вказівник стека – це регістр, який зберігає адресу останньої зайнятої ко-

мірки стека. Стеком або стековою пам'яттю називається область пам'яті,

організованої за принципом «останній прийшов – перший пішов».

Регістр команд зберігає код команди протягом усього часу виконання

команди.

Регістр адреси і регістри даних призначені для зберігання адрес і даних,

які використовуються під час виконання поточної команди у МП.

Регістр стану або регістр прапорців (ознак) призначений для зберігання

інформації про результат операції в АЛП і являє собою декілька тригерів, які

набувають одиничних або нульових значень.

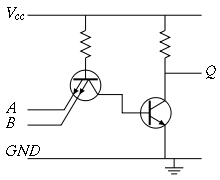

Транзисторно-транзисторная логика (ТТЛ, TTL) — разновидность цифровых логических микросхем, построенных на основе биполярных транзисторов и резисторов. Название транзисторно-транзисторный возникло из-за того, что транзисторы используются как для выполнения логических функций (например, И, ИЛИ), так и для усиления выходного сигнала (в отличие от резисторно-транзисторной и диодно-транзисторной логики).

Простейший базовый элемент ТТЛ выполняет логическую операцию И-НЕ, в принципе повторяет структуру ДТЛ микросхем и в то же время за счёт использования многоэмиттерного транзистора, объединяет свойства диода и транзисторного усилителя что позволяет увеличить быстродействие и энергопотребление, снизить потребляемую мощность и усовершенствовать технологию изготовления микросхемы.

ТТЛ получила широкое распространение в компьютерах, электронных музыкальных инструментах, а также в контрольно-измерительной аппаратуре и автоматике (КИПиА). Благодаря широкому распространению ТТЛ входные и выходные цепи электронного оборудования часто выполняются совместимыми по электрическим характеристикам с ТТЛ. Максимальное напряжение в схемах с ТТЛ может достигать 24В, однако это приводит к большому уровню паразитного сигнала. Достаточно малый уровень паразитного сигнала при сохранении достаточной эффективности достигается при напряжении 5В, поэтому данная цифра и вошла в технический регламент ТТЛ.

ТТЛ стала популярной среди разработчиков электронных систем после того, как в 1965 году фирма Texas Instruments представила серию интегральных микросхем 7400. Данная серия микросхем стала промышленным стандартом, но ТТЛ-микросхемы производятся и другими компаниями. Более того, фирма Texas Instruments не была первой, кто начал выпуск ТТЛ микросхем, несколько ранее его начали фирмы Sylvania и Transitron. Тем не менее промышленным стандартом стала именно серия 74 фирмы Texas Instruments, что в значительной мере объясняется большими производственными мощностями фирмы Texas Instruments, а также её усилиями по продвижению серии 74. Поскольку биполярные ИМС серии 74 фирмы Texas Instruments стали наиболее распространёнными, их функционально и параметрически повторяет продукция других фирм (Advanced Micro Devices, серия 90/9N/9L/9H/9S Fairchild, Harris, Intel, Intersil, Motorola, National и т.д).

Важность ТТЛ заключается в том, что ТТЛ-микросхемы оказались более пригодны для массового производства и при этом превосходили по параметрам ранее выпускавшиеся серии микросхем (резисторно-транзисторная и диодно-транзисторная логика).

[править] Принцип работы

Упрощённая схема элемента 2И-НЕ.

Принцип работы ТТЛ с простым инвертором:

Биполярные транзисторы могут работать в режимах: отсечки, нормально активный, инверсно активный и насыщения. В инверсно активном режиме эмиттерный переход закрыт, а коллекторный переход открыт. В инверсном режиме коэффициент усиления транзистора значительно меньше, чем в нормальном режиме, из-за несимметричного конструктивного исполнения переходов база-коллектор и база-эмиттер. При нулевом уровне на любом входе многоэмиттерного транзистора VT1 (на упрощённой схеме — справа) он работает в нормальном режиме и формирует на базе VT2 потенциал близкий к нулю. В этом состоянии неосновные носители из базы VT2 рассасываются не только через коллектор, но и через открытый VT1.

Если ноль подаётся на один из входов VT1, то наблюдается максимальный входной ток I=(E-0,7)/R1. В этом случае через другие эмиттерные переходы может наблюдаться паразитный ток. Чтобы он не был слишком велик неиспользуемые входы элемента присоединяются к источнику питания +5В, −5В через резистор с сопротивлением 1кОм, который может работать на 10 входов ТТЛ. Если свободные входы не подключаются ни к чему, то логика работы схемы сохраняется но паразитная ёмкость входных цепей будет уменьшать быстродействие цепи из расчёта 2 нс на 1 вход. Свободные входы могут воспринимать сигнал помехи, который может привести к сбою в работе схемы. Если на все входы поступает уровень логической единицы, то VT1 окажется инверсно-включенным, ток R1 течёт через коллектор VT1 в базу VT2, на выходе формируется нуль.

Если резистор R2 не используется, то мы имеем дело с элементом с открытым коллектором, у которого в условном обозначении используется дополнительный символ.

Логический элемент 3И-НЕ в серии микросхем 74LS(К555)[1]

ТТЛ (как и ТТЛШ) является прямым наследником ДТЛ и использует тот же принцип действия. Входной ТТЛ-транзистор (в отличие от обычного) имеет несколько, обычно от 2 до 8, эмиттеров. Эти эмиттеры выполняют роль входных диодов (если сравнивать с ДТЛ). Многоэмиттерный транзистор по сравнению с применявшейся в схемах ДТЛ сборкой из отдельных диодов занимает меньше места на кристалле и обеспечивает более высокое быстродействие. Следует отметить, что в микросхемах ТТЛШ, начиная с серии 74LS, вместо многэмиттерного транзистора используется сборка диодов Шоттки (серия 74LS) или PNP транзисторы в сочетании с диодами Шоттки (серии 74AS, 74ALS), так что фактически произошёл возврат к ДТЛ. Название ТТЛ заслуженно носят лишь серии 74, 74H, 74L, 74S, содержащие многоэмиттерный транзистор. Все более поздние серии многоэмиттерного транзистора не содержат, фактически являются ДТЛ и носят название ТТЛШ (ТТЛ Шоттки) лишь «по традиции», будучи развитием именно ДТЛ.

Транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ)

В ТТЛШ используются транзисторы Шоттки, в которых барьер Шоттки не позволяет транзистору войти в режим насыщения в результате чего диффузионная ёмкость мала и задержки переключения малы, а быстродействие высокое.

ТТЛШ отличается от ТТЛ наличием диодов Шоттки в цепях база — коллектор, что исключает насыщение транзистора, а также наличием демпфирующих диодов Шоттки на входах (редко на выходах) для подавления импульсных помех, образующихся из-за отражений в длинных линиях связи (длинной считается линия, время распространения сигнала в которой больше длительности его фронта, для самых быстрых ТТЛШ микросхем линия становится длинной начиная с длины в несколько сантиметров).

БІЛЕТ № 12

JK-тригер: загальні відомості, класифікація, типи.

Особливості додавання, віднімання, множення і ділення двійково-десяткових чисел.

Дати характеристику основних етапів створення програми мовою Асемблер (трансляція, компонування).