- •Представление числовой информации. Системы счисления. Кодирование текста. Ascii коды. Кодирование графических данных. Кодирование звука.

- •Основные блоки эвм. Материнская плата. Процессор. Оперативная память и кэш память. Внешняя память. Видеосистема. Периферийные устройства. Мультимедийные возможности компьютера.

- •Виды программного обеспечения. Операционная система Windows 7. Настройка рабочей среды. Стандартные и служебные программы.

- •Алгебра логики. Определения. Основные операции. Логические формулы.

- •Логические законы и правила преобразования логических выражений. Решение задач.

- •Связь между алгеброй логики и двоичным кодированием. Схемы и, или, не, и-не, или-не. Триггер, сумматор.

- •Текстовые редакторы Microsoft Word 2007 и OpenOffice.Org Writer. Основные функции. Сравнение возможностей.

- •9. Программы подготовки презентаций Microsoft PowerPoint 2007 и OpenOffice.Org Impress Основные функции. Сравнение возможностей.

- •10. Табличные процессоры Microsoft Excel 2007 и OpenOffice.Org Calc. Основные функции. Сравнение возможностей.

- •11. Алгоритмизация. Определения. Способы записи алгоритма. Виды алгоритмов.

- •12. Языки программирования. Классическое программирование. Визуальные средства разработки программ. Среда программирования.

- •14. Определение компьютерной сети. Обзор вычислительных сетей. Классификация компьютерных сетей. Сетевые топологии. Понятие сетевых протоколов.

- •16. Понятия модуляции и демодуляции сигналов. Квантование. Способы модуляции сигналов. Устройство модема. Классификация модемов.

- •20. Жизненный цикл кис и его этапы. Понятие информационной модели предметной области, информационные объекты. Создание информационной модели туристского предприятия.

- •21. Системы управления базами данных (субд). Классификация субд. Архитектура субд, История развития субд. Инструментальные средства быстрой разработки прикладных программ (rad).

Связь между алгеброй логики и двоичным кодированием. Схемы и, или, не, и-не, или-не. Триггер, сумматор.

Математический аппарат алгебры логики очень удобен для описания того, как функционируют аппаратные средства компьютера, поскольку основной системой счисления в компьютере является двоичная, в которой используются цифры 1 и 0, а значений логических переменных тоже два: “1” и “0”.

Из этого следует два вывода:

одни и те же устройства компьютера могут применяться для обработки и хранения как числовой информации, представленной в двоичной системе счисления, так и логических переменных;

на этапе конструирования аппаратных средств алгебра логики позволяет значительно упростить логические функции, описывающие функционирование схем компьютера, и, следовательно, уменьшить число элементарных логических элементов, из десятков тысяч которых состоят основные узлы компьютера.

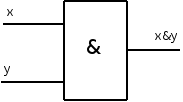

Схема

И (конъюнкция):

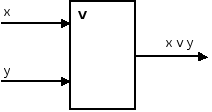

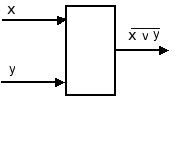

Схема

ИЛИ (дизъюнкция):

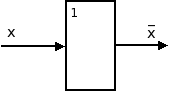

Схема

НЕ (инвертор):

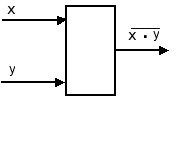

Схема

И-НЕ:

Схема

ИЛИ-НЕ:

http://informatique.org.ru/V_logical-foundations-of-PC.php

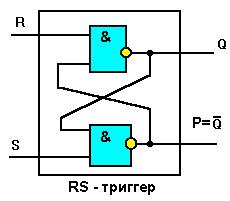

Триггер — это логическое устройство, способное хранить 1 бит информации. К триггерам относятся устройства, имеющие два устойчивых состояния. Простейший триггер — RS-триггер, образован из двух элементов И-НЕ (или ИЛИ-НЕ). Он позволяет запоминать 1 бит информации, поскольку информация в компьютере представляется в двоичном виде.

Cхема

RS-триггера

В обычном (исходном) состоянии на входы триггера поданы 1. Для записи информации на вход R подан 0. Для сброса информации и подготовки к приёму новой информации на вход S подается 0 и триггер вернётся в исходное состояние.

Поскольку один триггер запоминает 1 бит информации, то для запоминания 1 байта (8 бит) нужно 8 триггеров, для запоминания 1 Кб (1024 байт) надо 8192 триггеров. Современные микросхемы ОЗУ способны запоминать десятки мегабайт информации

В целях максимального упрощения работы компьютера все многообразие математических операций сводится к сложению двоичных чисел. Поэтому главной частью процессора является сумматор.

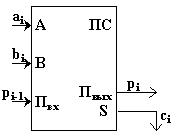

Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел.

Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины.

Много разрядный двоичный сумматор, предназначенный для сложения много разрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров, с рассмотрения которых мы и начнём.

Условное обозначение одноразрядного сумматора

При сложении чисел A и B в одном i-ом разряде приходится иметь дело с тремя цифрами:

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами.

Если требуется складывать двоичные слова длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.