6.Законы алгебры логики

На основе рассмотренных выше аксиом, выводятся теоремы, содержащие основные законы АЛ:1.Закон нулевого множества:

0 v x = x; 0 & x = 0; 0 & x1 & x2 &... & xn &... = 0. |

2.Закон универсального множества:

|

3.Закон повторения: x & x = x; x v x = x.

4.Закон двойной инверсии: х = х5.Законы дополнительности: а) исключенного третьего x v x = 1.б) логическое противоречие x & x = 0.6.Коммутативный (переместительный) закон: x & y = y & x; x v y = y v x.7.Ассоциативный (сочетательный) закон:

x&(y&z) = (x&y)&z = x&y&z; x v (yvz) = (xvy) v z = x v y v z. |

8.Дистрибутивный (распределительный) закон: x&(y v z) = x&y v x&z;

x v y&z = (x v y)&(x v z).9Законы поглощения:

x & (x v y) = x; x v x&y = x. x & (x v y) = x & y; x v x&y = x v y. |

10.Законы склеивания: а) полного(x v y)&(x v y) = x.б) неполного x&y v x&y = x v x&y v x&y;

(xvy)&(xvy) = x&(x v y)&(x v y). |

11.Законы инверсии (теоремы де Моргана):

x1&x2&... &xn = x1vx2v..vxn; |

|

x1vx2v... vxn = x1&x2&...&xn. |

|

12.Теоремы разложения (декомпозиции ЛФ):

f (x,y,...,z) = x& f (1,y,...,z) v x& f (0,y,...,z);

f (x,y,...,z) = (xv f (0,y,...,z))&(xv f (1,y,...,z)).

13.Следствия из теорем разложения:

x & f (x,y,..,z) = x & f (1,y,..,z); |

x v f (x,y,..,z) = x v f (0,y,..,z); |

x & f (x,y,..,z) = x & f (0,y,..,z); |

x v f (x,y,..,z) = x v f (1,y,..,z). |

14.Теорема Шеннона (обобщение теорем де Моргана):

f (x,y,...,z,&,v)=f (x,y,...,z,v,&). |

|

Данная теорема утверждает, что инверсия любой функции в АЛ получается путем замены каждой переменной ее инверсией и одновременно взаимной заменой символов конъюнкции и дизъюнкции.

Справедливость любого закона АЛ можно доказать разными методами. Законы (1-5) доказываются путем прямой подстановки вместо переменной значений 0 и 1. Ряд законов доказывается методом перебора всех возможных значений переменных, для которых проверяется справедливость закона. Для доказательства закона достаточно показать тождественность выражений, образующих левую и правую стороны доказываемого соотношения при всех наборах переменных, принимающих значения 0 или 1. Общий формальный метод доказательства законов АЛ состоит в том, что справедливость каждого закона доказывается на основе аксиом и ранее доказанных законов. Доказательство заключается в приведении обеих частей выражения к одному виду с помощью последовательных преобразований. Для доказательства законов инверсии следует воспользоваться методом математической индукции.

7.Функционально-полные базисы (ФПБ)Система булевых функций W называется функционально-полной, если произвольная булева функция вида f (x1, x2, ..., xn) может быть представлена суперпозицией функций x1, x2, ... ,xn и суперпозицией конечного числа функций системы W.В качестве простейших принято рассматривать следующие пять базисов:1Дизъюнкция (xivxj), конъюнкция (xi&xj), инверсия (xi); 2.Дизъюнкция (xivxj), инверсия (xi); 3.Конъюнкция (xi&xj), инверсия (xi); 4.Стрелка Пирса (xi xj = Xi V Xj); 5.Штрих Шеффера (xi | xj = Xi & Xj). С точки зрения практической реализации булевых функций функциональная полнота базисов (1-5) показывает, что произвольная логическая сеть может быть построена из простых функциональных элементов, вплоть до случая элементов одного типа (например, Пирса или Шеффера).В действительности электронной промышленностью выпускается ограниченный, но заведомо избыточный набор логических элементов, что позволяет сократить общее число микросхем в конкретном логическом блоке за счет расширения номенклатуры.

|

|

11.Аналитическое

представление булевой функции.

Рассмотрим

булеву функцию f

(X1,

X2,

..., Xn);

каждому набору входных переменных (X1,

X2,

..., Xn)

можно сопоставить двоичное число вида:i

= X1·

2n-1

+ X2·

2n-2

+ ... + Xn·

20.Можно

ввести функцию Fi(X1,

X2,

..., Xn)

следующим образом:Fi

= {0;1},1 – если номер набора есть;0 – в

противном случае.Тогда заданную функцией

алгебры логики можно представить в

форме:Fi(X1,

X2,

..., Xn)

= Fi1

v Fi2

v ... v Fik

= v Fij,

ij Т,где

Т есть множество наборов, на которых

функция принимает истинное значение

("1").В инженерной практике номера

наборов i записывают десятичными числами

и функцию задают в виде:F = v (j1,

j2,

..., jn)

=

![]() (j1,

j2,

..., jn)Для

примера(в столбик) X1

00001111 X2

001100 X3

01010101

f

00010111

получим:F(X1,

X2,

..., Xn)

= 1011

v

1101

v

1110

v

1111F

= v

(3, 5, 6, 7) =

(3,

5, 6, 7)Множество Т = (3, 5, 6, 7)Доказано, что

функцию Fi

можно представить как конъюнкцию

аргументов (X1,

X2,

..., Xn),

такую, что если Xi

в наборе (X1,

X2,

..., Xn)

равен 0, то в конъюнкцию входит инверсия

Xi

(т.е. Xi),

если Xi

равен 1, то в конъюнкцию входит Xi.

(j1,

j2,

..., jn)Для

примера(в столбик) X1

00001111 X2

001100 X3

01010101

f

00010111

получим:F(X1,

X2,

..., Xn)

= 1011

v

1101

v

1110

v

1111F

= v

(3, 5, 6, 7) =

(3,

5, 6, 7)Множество Т = (3, 5, 6, 7)Доказано, что

функцию Fi

можно представить как конъюнкцию

аргументов (X1,

X2,

..., Xn),

такую, что если Xi

в наборе (X1,

X2,

..., Xn)

равен 0, то в конъюнкцию входит инверсия

Xi

(т.е. Xi),

если Xi

равен 1, то в конъюнкцию входит Xi.

12.Графическое

представление булевой функции. Карты

карно.графическое

представление мат объектов является

наиболее наглядным и удобным для

конструкт использования. Поэтому

широкое применение находит представление

булевых функций с помощью пространственных

двоичных решёток.Поскольку одна булева

переменная может принимать два значения

"0" и "1", то её можно

интерпретировать отрезком прямой,

являющимся одномерным пространством.![]() От

одной переменной может быть построено

четыре функции в ал. Их можно представить

на этом отрезке, показывая нулевое

значение функции как "0", а единичное

- как "1" .

От

одной переменной может быть построено

четыре функции в ал. Их можно представить

на этом отрезке, показывая нулевое

значение функции как "0", а единичное

- как "1" .

|

|

|||

x |

g1 |

g2 |

g3 |

g4 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

Для

двух и трех переменных мы получим

квадрат на плоскости и куб в трёхмерном

пространстве соответственно.Для нашего

примера:f

(X1,X2,X3)

= X1·

X2·

X3v

X1·

X2·

X3v

X1·

X2·

X3v

X1·

X2·

X3.любая

таблично заданная функция алгебры

логики может быть представлена в

форме:Фi(X1,

X2,

..., Xn)

= Фi1·

Фi2·

... Фik

= &Фij,

ij Т0,где

Фi(X1,

X2,

..., Xn)

- характеристическая функция нуля,

определённая как:Фi

= {0;1}0 – если номер набора есть i,1 – в

противном случае.Т0

– есть множество наборов, из которых

функция обращается в ноль.

Для

двух и трех переменных мы получим

квадрат на плоскости и куб в трёхмерном

пространстве соответственно.Для нашего

примера:f

(X1,X2,X3)

= X1·

X2·

X3v

X1·

X2·

X3v

X1·

X2·

X3v

X1·

X2·

X3.любая

таблично заданная функция алгебры

логики может быть представлена в

форме:Фi(X1,

X2,

..., Xn)

= Фi1·

Фi2·

... Фik

= &Фij,

ij Т0,где

Фi(X1,

X2,

..., Xn)

- характеристическая функция нуля,

определённая как:Фi

= {0;1}0 – если номер набора есть i,1 – в

противном случае.Т0

– есть множество наборов, из которых

функция обращается в ноль.

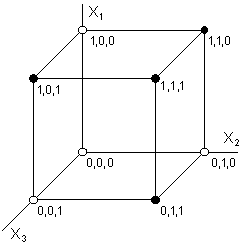

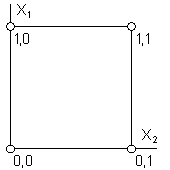

8.Формы представления логических функций. Аналитическое представление.Рассмотрим булеву функцию f (X1, X2, ..., Xn); каждому набору входных переменных (X1, X2, ..., Xn) можно сопоставить двоичное число вида: i = X1· 2n-1 + X2· 2n-2 + ... + Xn· 20.Можно ввести функцию Fi(X1, X2, ..., Xn) следующим образом: Fi = {0;1}, 1 – если номер набора есть; 0 – в противном случае.Тогда заданную функцией алгебры логики можно представить в форме: Fi(X1, X2, ..., Xn) = Fi1 v Fi2 v ... v Fik = v Fij, ij Т, где Т есть множество наборов, на которых функция принимает истинное значение ("1").Графическое представление математических объектов является наиболее наглядным и удобным для конструктивного использования. Поэтому широкое применение находит представление булевых функций с помощью пространственных двоичных решёток.Одна булева переменная может принимать два значения "0" и "1", то её можно интерпретировать отрезком прямой, являющимся одномерным пространством. Для двух и трех переменных мы получим квадрат на плоскости и куб в трёхмерном пространстве.

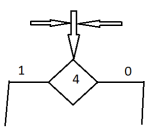

10.Карты

Карно.Нормальные формы булевых

функцийКарта

Карно

– это

двумерная табличная форма представления

булевой функции, позволяющая

в наглядной графической форме легко

отыскать минимальные ДНФ логических

функций. Каждой клетке в таблице

сопоставляется дизъюнкт СДНФ

минимизируемой

функции, причем так, что любым осям

симметрии таблицы соответствуют

зоны, взаимно инверсные по какой-либо

переменной.расположение

клеток позволяет легко определить

склеивающиеся термы СДНФ (отличающиеся

знаком инверсии только одной переменной):

они располагаются в таблице симметрично.

Например,

следующая карта Карно построена для

импликации двух переменных х

у.

В ячейки карты вписываются значения

из таблицы истинности функции, при

этом, если перед соответствующей

переменной стоит знак отрицания, то в

таблице истинности выбирается строка

с ложным значением данной переменной,

иначе – с истинным значением. Единичные

значения функции показывают те

дизъюнкты, которые присутствуют в СДНФ

этой функции. Расположения элементов

в картах Карно функции 2 переменных-в

один конъюнкт эта переменная входит

без отрицания, а в другой – с

отрицанием. Алгоритм поиска минимальной

ДНФ по карте Карно основан на выявлении

на карте мин кол-ва макс квадратов или

прямоугольников со сторонами, равными

степени двойки, так, чтобы они состояли

только из ячеек, содержащих единицы.

Нормальные

формы. Произведение

Единичные

значения функции показывают те

дизъюнкты, которые присутствуют в СДНФ

этой функции. Расположения элементов

в картах Карно функции 2 переменных-в

один конъюнкт эта переменная входит

без отрицания, а в другой – с

отрицанием. Алгоритм поиска минимальной

ДНФ по карте Карно основан на выявлении

на карте мин кол-ва макс квадратов или

прямоугольников со сторонами, равными

степени двойки, так, чтобы они состояли

только из ячеек, содержащих единицы.

Нормальные

формы. Произведение![]() называется

элементарной

конъюнкцией

ранга k, если все переменные в нем

различны. Логическая единица считается

элементарной конъюнкцией ранга 0.

Логическая сумма

называется

элементарной

конъюнкцией

ранга k, если все переменные в нем

различны. Логическая единица считается

элементарной конъюнкцией ранга 0.

Логическая сумма![]() называется

элементарной

дизъюнкцией

ранга r, если все переменные в ней

различны. Логический ноль считается

элементарной дизъюнкцией ранга 0.Формула

вида u1

v

u2

v

... v

ui

где: u1,

u2,

... ui

– различные элементарные конъюнкции

рангов r1,

r2,

... ri

соответственно называется дизъюнктивной

нормальной формой

(ДНФ), а число

называется

элементарной

дизъюнкцией

ранга r, если все переменные в ней

различны. Логический ноль считается

элементарной дизъюнкцией ранга 0.Формула

вида u1

v

u2

v

... v

ui

где: u1,

u2,

... ui

– различные элементарные конъюнкции

рангов r1,

r2,

... ri

соответственно называется дизъюнктивной

нормальной формой

(ДНФ), а число

![]() –

сложностью

ДНФ.

Формула вида S1·

S2·

... · St

где:

S1,

S2,

... St

– различные элементарные дизъюнкции

рангов p1,

p2,

... pt

соответственно называется конъюнктивной

нормальной формой

(КНФ), а число

–

сложностью

ДНФ.

Формула вида S1·

S2·

... · St

где:

S1,

S2,

... St

– различные элементарные дизъюнкции

рангов p1,

p2,

... pt

соответственно называется конъюнктивной

нормальной формой

(КНФ), а число

![]() –

сложностью

КНФ.Всякая

булева функция, отличная от тождественного

"0" может быть задана ДНФ и, в общем

случае, неоднозначно. Аналогичное

правило действует и для КНФ, если булева

функция не тождественна "1".По

таблице задающей булеву функцию f

(Х1,

Х2,

... Хn)

строится совершенная

ДНФ:

u1

v

u2

v

... v

uS,

где

–

сложностью

КНФ.Всякая

булева функция, отличная от тождественного

"0" может быть задана ДНФ и, в общем

случае, неоднозначно. Аналогичное

правило действует и для КНФ, если булева

функция не тождественна "1".По

таблице задающей булеву функцию f

(Х1,

Х2,

... Хn)

строится совершенная

ДНФ:

u1

v

u2

v

... v

uS,

где

![]() таковы,

что i = 1, 2, ..., S и наборы i1,

i2,

..., in

таковы, что f

(i1,

i2,

..., in)

= 1.Совершенная

КНФ

имеет вид:

S1

& S2

& ... & SC

где

таковы,

что i = 1, 2, ..., S и наборы i1,

i2,

..., in

таковы, что f

(i1,

i2,

..., in)

= 1.Совершенная

КНФ

имеет вид:

S1

& S2

& ... & SC

где

![]() таковы,

что i

= 1, 2, ..., S

и наборы i1,

i2,

..., in

таковы, что f

(i1,

i2,

..., in)

= 0.Совершенная ДНФ и КНФ для заданной

булевой функции строятся однозначно.

Они четко получаются из таблицы

истинности булевой функции следующим

образом.Для

СДНФ:1необходимо

выбрать из таблицы истинности функции

все наборы аргументов, на которых

функция принимает значения "1";

2.выписать

элементарные конъюнкции, соответствующие

этим наборам элементов; если Хi

входит в данный набор как 1, он вписывается

без изменения в конъюнкцию, если Хi

входит в данный набор как 0, то в конъюнкции

вписывается отрицание Хi

(т.е. Xi);

3.все

полученные элементарные конъюнкции

соединяются между собой знаками

дизъюнкции (т.е. v).

Для

СКНФ:1.необходимо

выбрать в таблице истинности функции

все наборы аргументов, на которых

функция принимает значения "0";

2.выписать

элементарные дизъюнкции, соответствующие

этим наборам элементов; если Xi

входит в данный набор как 0, он вписывается

без изменений в дизъюнкцию, если Xi

входит в данный набор как 1, то в дизъюнкцию

вписывается его отрицание (т.е. Xi);

3.все

полученные элементарные дизъюнкции

соединяются между собой знаками

конъюкции .

таковы,

что i

= 1, 2, ..., S

и наборы i1,

i2,

..., in

таковы, что f

(i1,

i2,

..., in)

= 0.Совершенная ДНФ и КНФ для заданной

булевой функции строятся однозначно.

Они четко получаются из таблицы

истинности булевой функции следующим

образом.Для

СДНФ:1необходимо

выбрать из таблицы истинности функции

все наборы аргументов, на которых

функция принимает значения "1";

2.выписать

элементарные конъюнкции, соответствующие

этим наборам элементов; если Хi

входит в данный набор как 1, он вписывается

без изменения в конъюнкцию, если Хi

входит в данный набор как 0, то в конъюнкции

вписывается отрицание Хi

(т.е. Xi);

3.все

полученные элементарные конъюнкции

соединяются между собой знаками

дизъюнкции (т.е. v).

Для

СКНФ:1.необходимо

выбрать в таблице истинности функции

все наборы аргументов, на которых

функция принимает значения "0";

2.выписать

элементарные дизъюнкции, соответствующие

этим наборам элементов; если Xi

входит в данный набор как 0, он вписывается

без изменений в дизъюнкцию, если Xi

входит в данный набор как 1, то в дизъюнкцию

вписывается его отрицание (т.е. Xi);

3.все

полученные элементарные дизъюнкции

соединяются между собой знаками

конъюкции .

13)Двойственность

булевых функций.Операция

(или функция) f

называется двойственной

д\ операции, если табл, задающ ф-ю f,

получается из табл, задающей ф-ю, путём

замены в ней всюду "0" на "1" и

"1" на "0", включая и замену

значений функции.Прим:рассмотрим

ф-и дизъюн и коньюк 2 перем, кот задаются

соответствующ табл(в

столбик)Х10011

Х20101

V0111;

X10011

X20101

&

0001Преобразуем

вторую таблицу в соответствии с введенным

обозначением, получим:X1

1100X21010

?1110

Х10011

Х20101

V0111Что

соответствует таблице операции

дизъюнкции с точностью до перестановки

строк.Преобразование формул, при котором

знаки всех операций в логическом

выражении заменяются на знаки двойственных

им операций, "0" заменяется на "1",

а "1" на "0", называется

преобразованием двойственности.прим

рассмотрим преобразование следующей

функции3переменных(табл3перем).

Выполним

из функции преобразование

двойственности(Табл.Х111110000Х211001100Х310101010f01100111)Совершенные

нормальные формы для двойственной

функции f

*

примут вид:

Выполним

из функции преобразование

двойственности(Табл.Х111110000Х211001100Х310101010f01100111)Совершенные

нормальные формы для двойственной

функции f

*

примут вид:

14)Минимиз

лог ф-й: общее представление.Задача

минимиз булевых функций возникает из

практич потребностей построения лог

схем, различающих аналитич выражения

бул функций.Первич аналитич формой,

получаемой из таблич предст-я лог ф-и

явл СДНФ или СКНФ. В бол-ве случаев знач

ф-и в виде СДНФ и СКНФ явл заведомо не

экономной, избыточ и м\б построена

эквивал ф-я, реализующая в своем

представлении меньшее число перем и

операций.Сложностью нормальной формы

следует понимать сумму рангов её

составляющих, т.е. число букв в ней.

=>ДНФ, имеющая наим сумму рангов среди

всех ДНФ, эквивалентных данной функции,

назыв-ся мин ДНФ (МДНФ). ДНФ, имеющая

наим длину среди всех ДНФ, эквивал

данной ф-и называется кратчайшей ДНФ

(КДНФ).Тупиковая ДНФ-

ДНФ,

при удалении из которой любой коньюкции,

полученная в результате ДНФ не будет

эквивалентна исходной.Способы

минимизации:1Граф

способ минимиз (к Карно)Граф

способ реализ Бул ф-й карт Карно

представляет собой операции склеив и

поглощ.Карты Карно рассм-ся как

перестроенные сооответств-им образом

табл.истинности функций. Можно

рассматривать как 3х

мерную развертку булевого куба. Основным

методом минимизации лог

ф-и представленных в СДНФ,СКНФ явл оп-и

попар склеив(м\у 2 термами или членами,

содержащ одинаковые переменные) неполн

и элемент п Н-р,1)

2)

2)

главной

задачей минимизации при СКНФ и СДНФ

является поиск термов пригодных к

склейке с последующ. поглощением. Карта

Карно м.б. составлена для любого числа

переменных.После того как карта заполнена

можно приступать к минимиз, если

необходимо получить МДНФ,то в карте

рассм-ся только клетки, к-ые содержат

единицы; если МКНФ-клетки, где содержатся

нули.Минимизация

провод-ся по след-им правилам(для

ДНФ)1.Объед-т

смежн клетки содерж 1 в область так,

чтобы одна область содержала 2n

клеток.2.Область д\распол-ся симм оси.

Оси располагаются через каждые 4

клетки.3. Не смеж области расп-ся симм

относ осей они м\объед-ся в одну.4.Область

д.б. как можно больше,а кол-во областей

меньше.5. Обл-ти могут пересекаться.Далее

выбирается 1ая обл-ть для перем не меняющ

значение в этой обл-ти. Выпис-ся конъюнкц,

е.неменяющ перем нулевая над ней ставят

инверсию.Далее выполняется аналог

операция для всех областей , после этого

конъюнкции обла объед-ся в дизъюнкц.ДляКНФ:

рассм-ся клетки с нулями ,неменяющ перем

в пределах одной обл объед-ся в

дизъюнкции.Дизъюнкции областей объед-ся

в конъюн-ции, но при этом минимиз

считается законченной.

главной

задачей минимизации при СКНФ и СДНФ

является поиск термов пригодных к

склейке с последующ. поглощением. Карта

Карно м.б. составлена для любого числа

переменных.После того как карта заполнена

можно приступать к минимиз, если

необходимо получить МДНФ,то в карте

рассм-ся только клетки, к-ые содержат

единицы; если МКНФ-клетки, где содержатся

нули.Минимизация

провод-ся по след-им правилам(для

ДНФ)1.Объед-т

смежн клетки содерж 1 в область так,

чтобы одна область содержала 2n

клеток.2.Область д\распол-ся симм оси.

Оси располагаются через каждые 4

клетки.3. Не смеж области расп-ся симм

относ осей они м\объед-ся в одну.4.Область

д.б. как можно больше,а кол-во областей

меньше.5. Обл-ти могут пересекаться.Далее

выбирается 1ая обл-ть для перем не меняющ

значение в этой обл-ти. Выпис-ся конъюнкц,

е.неменяющ перем нулевая над ней ставят

инверсию.Далее выполняется аналог

операция для всех областей , после этого

конъюнкции обла объед-ся в дизъюнкц.ДляКНФ:

рассм-ся клетки с нулями ,неменяющ перем

в пределах одной обл объед-ся в

дизъюнкции.Дизъюнкции областей объед-ся

в конъюн-ции, но при этом минимиз

считается законченной.

15)Постановка

задачи минимиз лог ф-й.Задача

минимиз бул ф-й возникает из практич

потребн построения лог схем, различающ

аналитич выражения бул ф-й.Первичн

аналит формой, получ из табличн представ-я

лог ф-и явл СДНФ или СКНФ.В бол-ве случаев

значение ф-и в виде СДНФ и СКНФ явл

заведомо не экономной, избыточн и м\б

построена эквивал ф-я, реализующ в своем

представлении меньшее число переменных

иопераций.Например,

Используя

законы алгебры логики, получим:

Используя

законы алгебры логики, получим: Простейш

или мин представление бул ф-и необходимо

искать в опред базисе. Наилучшие

результаты получены для базиса,

включаюшего инверсию, дизъюкцию и

коньюкцию. Поэтому в дальнейшем задача

минимизации будет рассматриваться

именно в этом базисе.В соответствии

заданным ранее определением под

сложностью нормальной формы следует

понимать сумму рангов её составляющих,

т.е. число букв в ней. Поэтому ДНФ, имеющая

наим сумму рангов среди всех ДНФ, эквивал

данной ф-и, назыв мин ДНФ (МДНФ).Если к

ДНФ примен лишь операции склеив AB

v

AB

= A

и поглощ AB

v

A = A,

то рано или поздно дальнейш преобраз

окажутся невозможн. В этом случае будет

получаться тупиковая ДНФ, т.е. такая

ДНФ, при удалении из которой любой

коньюкции, полученная в результате ДНФ

не будет эквив исходной.Разработанные

методы минимизации достаточно хорошо

работают для функций первой и третьей

группы по классификации Потёмкина и

не дают гарантированного результата

для функций второй группы.Потёмкин

предложил разделять логические функции

на три группы:функции малого числа

аргументов(ф-и 3 – 5 арг, кот часто встреч

при реализ цифр аппаратуры.); "объективные"

функции многих аргументов(ф-и >5 арг,

кот отраж некот естеств, технич или

природн зав-ти.); "субъективные"

функции многих аргументов(ф-и больш

числа арг. Д\них функций харак наличие

внут структуры и возмож-тей декомпоз

на более простые позиции).Интервалом

l-го

ранга

называется подмножество вершин двоичного

n-мерного куба, соответств элементарн

конъюнкции l-го

ранга.Покрытием

l-го

ранга

называется подмножество клеток к Карно

n-го порядка, соответствующ элементарной

конъюнкции l-го

ранга.При задании бул функции в виде

ДНФ, будет задано и мн-во ее еденичн

значений, что будет соответствовать

комбинации интервалов на пространств

кубе или комбинации покрытий на к Карно.

Простейш

или мин представление бул ф-и необходимо

искать в опред базисе. Наилучшие

результаты получены для базиса,

включаюшего инверсию, дизъюкцию и

коньюкцию. Поэтому в дальнейшем задача

минимизации будет рассматриваться

именно в этом базисе.В соответствии

заданным ранее определением под

сложностью нормальной формы следует

понимать сумму рангов её составляющих,

т.е. число букв в ней. Поэтому ДНФ, имеющая

наим сумму рангов среди всех ДНФ, эквивал

данной ф-и, назыв мин ДНФ (МДНФ).Если к

ДНФ примен лишь операции склеив AB

v

AB

= A

и поглощ AB

v

A = A,

то рано или поздно дальнейш преобраз

окажутся невозможн. В этом случае будет

получаться тупиковая ДНФ, т.е. такая

ДНФ, при удалении из которой любой

коньюкции, полученная в результате ДНФ

не будет эквив исходной.Разработанные

методы минимизации достаточно хорошо

работают для функций первой и третьей

группы по классификации Потёмкина и

не дают гарантированного результата

для функций второй группы.Потёмкин

предложил разделять логические функции

на три группы:функции малого числа

аргументов(ф-и 3 – 5 арг, кот часто встреч

при реализ цифр аппаратуры.); "объективные"

функции многих аргументов(ф-и >5 арг,

кот отраж некот естеств, технич или

природн зав-ти.); "субъективные"

функции многих аргументов(ф-и больш

числа арг. Д\них функций харак наличие

внут структуры и возмож-тей декомпоз

на более простые позиции).Интервалом

l-го

ранга

называется подмножество вершин двоичного

n-мерного куба, соответств элементарн

конъюнкции l-го

ранга.Покрытием

l-го

ранга

называется подмножество клеток к Карно

n-го порядка, соответствующ элементарной

конъюнкции l-го

ранга.При задании бул функции в виде

ДНФ, будет задано и мн-во ее еденичн

значений, что будет соответствовать

комбинации интервалов на пространств

кубе или комбинации покрытий на к Карно.

16)

Граф способ минимиз (использ к Карно).Граф

способ реализац Бул ф-й к Карно предст

собой операции 1склеив и поглощ.К Карно

рассм-ся как перестр сооответствующ

образом табл.истинности ф-й. М\рассматр

как 3х

мерную развертку бул куба. Основн

методом минимиз лог ф-и явл операции

попарн склеивания неполного и

элементарного поглощения. Опер попарн

склеив осущ м\у 2 термами или членами,

содержащ один переменные. Вхожд которых

прямые и инверсные совпадают для всех

перем кроме одной. В этом случае все

перем кроме 1 м\вынести за скобки,а

оставшиеся в скобках прямое и инверсное

вхождение1 перем подвергать склейке.

Н-р,1)

2)

Т.о.

главной задачей минимизации при СКНФ

и СДНФ является поиск терминов пригодных

к склейке с последним поглощением, что

для больших форм может оказаться

достаточно сложной задачей Булевых

функций n-переменных

представленные в виде СДНФ и СКНФ. Могут

иметь в своём составе 2n

различных термов.Все эти члены составляют

некоторую структуру топологических

эквивалентному n-мерному

кубу, причём любые 2 терма соединённые

ребром пригодны для склейки и поглощения.

(п)В случае функции 3х

переменных

приходиться иметь дело с кубом.Для

упрощения работы с булев. Функциями

большого числа переменных предложим

следующий прием: куб представляющий

собой структуру термов разворачивается

на плоскость(р)Анал-но можно работать

с ф-ями 4х

, 5ти

и более переменных.К Карно м.б. состав

д\люб числа перем. К Карно представл

собой табл. истинности составленной в

2х

мерном виде.Верхн строка к.К. явл-ся

соседней с нижней, а правый столбец

соседним слева,т.е. сворач в тор,на

пересечении строки и столбца простирается

соответствующее значение из табл.

истинности ф-ций. После того как карта

заполнена можно приступать к минимизации,

если необходимо получить МДНФ,то в

карте рассм-ся только клетки, к-ые

содержат1; если МКНФ-клетки, где

содержатся 1.Минимиз провод-ся по след-им

правилам(для ДНФ)1.Объединяет смежные

клетки содержащие единицы в область

так, чтобы одна область содержала 2n

клеток2.Область должна располагаться

симметрично оси(осей). Оси располагаются

через каждые 4 клетки.3. Не смежные

области располагаются симметрично

относительно осей(оси) они могут

объединяться в одну.4.Область д.б. как

можно больше,а кол-во областей меньше.5.

Обл-ти могут пересекаться6.Возможно

несколько вариантов покрытия. Далее

выбирается 1ая обл-ть для переменных

не меняющих своё значение в этой обл-ти.

Выпис-ся конъюнкция, если неменяющаяся

переменная нулевая над ней ставят

инверсию.Далее выполняется аналогичная

операция для всех областей , после этого

конъюнкции областей объед-ся в

дизъюнкции.ДляКНФ: рассм-ся клетки с

нулями ,неменяющиеся переменные в

пределах одной области объед-ся в

дизъюнкции.Дизъюнкции областей объед-ся

в конъюн-ции, но при этом минимизация

считается законченной.При задании бул

функции в виде ДНФ, будет задано и мн-во

ее еденичных значений, что будет

соответствовать комбинации интервалов

на пространств кубе или комбинации

покрытий на карте Карно.Задача нахождения

МДНФ может быть сформулирована как

задача построения такого множества

покрытий единичных значений булевой

функции, при котором сложность ДНФ

будет минимальной.Графически это

означает, что необходимо и достаточно

найти множество покрытий минимального

ранга, представляющих множество

единичных значений булевой функции.

2)

Т.о.

главной задачей минимизации при СКНФ

и СДНФ является поиск терминов пригодных

к склейке с последним поглощением, что

для больших форм может оказаться

достаточно сложной задачей Булевых

функций n-переменных

представленные в виде СДНФ и СКНФ. Могут

иметь в своём составе 2n

различных термов.Все эти члены составляют

некоторую структуру топологических

эквивалентному n-мерному

кубу, причём любые 2 терма соединённые

ребром пригодны для склейки и поглощения.

(п)В случае функции 3х

переменных

приходиться иметь дело с кубом.Для

упрощения работы с булев. Функциями

большого числа переменных предложим

следующий прием: куб представляющий

собой структуру термов разворачивается

на плоскость(р)Анал-но можно работать

с ф-ями 4х

, 5ти

и более переменных.К Карно м.б. состав

д\люб числа перем. К Карно представл

собой табл. истинности составленной в

2х

мерном виде.Верхн строка к.К. явл-ся

соседней с нижней, а правый столбец

соседним слева,т.е. сворач в тор,на

пересечении строки и столбца простирается

соответствующее значение из табл.

истинности ф-ций. После того как карта

заполнена можно приступать к минимизации,

если необходимо получить МДНФ,то в

карте рассм-ся только клетки, к-ые

содержат1; если МКНФ-клетки, где

содержатся 1.Минимиз провод-ся по след-им

правилам(для ДНФ)1.Объединяет смежные

клетки содержащие единицы в область

так, чтобы одна область содержала 2n

клеток2.Область должна располагаться

симметрично оси(осей). Оси располагаются

через каждые 4 клетки.3. Не смежные

области располагаются симметрично

относительно осей(оси) они могут

объединяться в одну.4.Область д.б. как

можно больше,а кол-во областей меньше.5.

Обл-ти могут пересекаться6.Возможно

несколько вариантов покрытия. Далее

выбирается 1ая обл-ть для переменных

не меняющих своё значение в этой обл-ти.

Выпис-ся конъюнкция, если неменяющаяся

переменная нулевая над ней ставят

инверсию.Далее выполняется аналогичная

операция для всех областей , после этого

конъюнкции областей объед-ся в

дизъюнкции.ДляКНФ: рассм-ся клетки с

нулями ,неменяющиеся переменные в

пределах одной области объед-ся в

дизъюнкции.Дизъюнкции областей объед-ся

в конъюн-ции, но при этом минимизация

считается законченной.При задании бул

функции в виде ДНФ, будет задано и мн-во

ее еденичных значений, что будет

соответствовать комбинации интервалов

на пространств кубе или комбинации

покрытий на карте Карно.Задача нахождения

МДНФ может быть сформулирована как

задача построения такого множества

покрытий единичных значений булевой

функции, при котором сложность ДНФ

будет минимальной.Графически это

означает, что необходимо и достаточно

найти множество покрытий минимального

ранга, представляющих множество

единичных значений булевой функции.

17)Аналитические

способы минимизации (метод Квайна).Метод

минимиз Квайна представляет собой лок

алгоритм, включающ опред послед-ть

этапов . Предполагается, что исходная

минимиз функция задач, в СДНФ.ЭТАП 1.

Нахождение первичных импликант.

Импликантой

некоторой бул ф-и назыв др бул ф-я, такая

что мн-во нул знач импликанты Nимп.(0)

пересекается со мн-вом нул знач ф-и

Nf (0),

а мн-во единичн знач Nимп.(1)

принадлежит Nf

(1).Первичн

импликантой

бул ф-и назыв такая импликанта, никакая

часть которой не является импликантой

исходной функции. На данном этапе

рассматриваются все элементарн

конъюнкции (ЭК) ранга n, первоначально

входящие в СДНФ. Они попарно сравниваются

м\у собой с целью нахождения поглощ

вида:Fxi

v

Fxi

= F,при

кот получаются ЭК ранга (n – 1). После

получения всех возможных ЭК ранга (n –

1) они вновь сравниваются попарно между

собою для получения ЭК ранга (n – 2) и

т.д. ЭК, принявшие участие в поглощениях,

отмечаются некоторым символом. Процесс

заканчивается тогда, когда полученные

ЭК ранга m не склеиваются м\у собою. Все

не отмеченные ЭК будут являться

первичными импликантами.Для данного

построения целесообразно использовать

квадратные таблицы, размерностью l

x l,

где l

– число ЭК k-го ранга; k = n, n – 1, ...,

m.ЭТАП 2.

Расстановка меток и нахождение

существенных импликант.В результате

выполнения первого этапа минимиз ф-я

оказалась предст в виде:f

(x1,

x2,

..., xn)

=

![]() где

li

– первичные импликанты.Поэтому составл

таблица, строки кот соответ первичн

импликантам, а столбцы ЭК исх ф-и. Если

в некоторую ЭК входит одна из первичных

импликант, то на пересечении соответствующей

строки и столбца ставится метка. Если

после заполнения всей таблицы в некотором

столбце оказывается только одна метка,

то первичная импликанта, находящаяся

в данной строке, называется существенной.Из

таблицы исключаются строки, соответствующие

существенным импликантам, и столбцы

ЭК, покрываемых этими существенными

импликантами ЭТАП 3.

Вычеркивание избыточных столбцов и

избыточн первичных импликант.Если в

таблице полученной на предыдущем этапе

имеются столбцы, в которых метки

расположены в одинаковых строках, то

один из таких столбцов вычеркивается.

Так как покрытие оставшегося столбца

будет осуществлять покрытие удаленной

ЭК.Если после удаления избыточных

столбцов в таблице появляются строки,

в которых нет ни одной метки, то они

вычеркиваются, так как первичные

импликанты, соответствующие этим

строкам не покрывают оставшиеся в

рассмотрении ЭК.ЭТАП 4.

Выбор мин покрытия максимальными

интервалами.Из таблицы, полученной в

результате выполнения третьего этапа,

выбирается совокупность первичных

импликант, которая включает хотя бы по

одной метке в каждом столбце. При

нескольких возможных вариантах

выбирается покрытие минимальной

сложности.

где

li

– первичные импликанты.Поэтому составл

таблица, строки кот соответ первичн

импликантам, а столбцы ЭК исх ф-и. Если

в некоторую ЭК входит одна из первичных

импликант, то на пересечении соответствующей

строки и столбца ставится метка. Если

после заполнения всей таблицы в некотором

столбце оказывается только одна метка,

то первичная импликанта, находящаяся

в данной строке, называется существенной.Из

таблицы исключаются строки, соответствующие

существенным импликантам, и столбцы

ЭК, покрываемых этими существенными

импликантами ЭТАП 3.

Вычеркивание избыточных столбцов и

избыточн первичных импликант.Если в

таблице полученной на предыдущем этапе

имеются столбцы, в которых метки

расположены в одинаковых строках, то

один из таких столбцов вычеркивается.

Так как покрытие оставшегося столбца

будет осуществлять покрытие удаленной

ЭК.Если после удаления избыточных

столбцов в таблице появляются строки,

в которых нет ни одной метки, то они

вычеркиваются, так как первичные

импликанты, соответствующие этим

строкам не покрывают оставшиеся в

рассмотрении ЭК.ЭТАП 4.

Выбор мин покрытия максимальными

интервалами.Из таблицы, полученной в

результате выполнения третьего этапа,

выбирается совокупность первичных

импликант, которая включает хотя бы по

одной метке в каждом столбце. При

нескольких возможных вариантах

выбирается покрытие минимальной

сложности.

18) Аналитические способы минимизации (метод Квайна-МакКласки).Основным недостатком метода Квайна является необходимость полного по парного сравнения ЭК на этапе нахождения первичных импликант. Мак-Класки предложил модернизацию алгоритма Квайна, которая заключается в том, что все ЭК, входящие в СДНФ записывается в виде двоичных чисел (номеров наборов), которые группируются по числу входящих в них единиц в непересекающиеся классы. В класс с номером i войдут все ЭК содержащие в своей двоичной записи i единиц. По парное сравнение следует производить м\у соседними по номеру классами, т.к только в них могут находиться склеивающиеся ЭК.При образовании ЭК ранга меньше n вместо исключенных переменных ставится символ стирания x.когда дальнейшие склеивания не возможны, поэтому переходим ко второму этапу.

19) Понятие СДНФ, КДНФ, ТДНФ, МДНФ, СКНФ, МКНФ.Совершенная дизъюнктивная нормальная форма (СДНФ)Ф-я представляется суммой групп. Каждая группа состоит из произведения, в которую входят все переменные.Например: f(x1,x2,x3)=x1·x2·x3 + x1·x2·x3 + x1·x2·x3 Алгоритм построения СДНФ по таблице истинности1.В таблице истинности отмечаем те наборы переменных, на кот знач ф-и равно 1. 2.Для каждого отмеч набора записываем конъюнкцию всех перем по следующ правилу: е знач некоторой переменной есть 1, то в конъюнкцию включаем саму перем, иначе ее отрицание. 3.Все полученные конъюнкции связ операциями дизъюнкции.Совершенная конъюнктивная нормальная форма (СКНФ)Функция представляется произведением групп. Каждая группа состоит из суммы, в которую входят все переменные. Например: f(x1,x2,x3)=(x1+x2+x3) · (x1+x2+x3) · (x1+x2+x3) Минимальной ДНФ (МДНФ) ф-и f(x1, x2, …, xn) называется ДНФ, реализующая ф-ю f и содержащая мин число символов переменных по сравнен со всеми другими ДНФ, реализующими функцию f. МДНФ данной формулы м\найти, перебрав конечн число равносильных ей ДНФ и выбрав среди них ту, кот содержит мин число перем.при большом числе переменных такой перебор практически невыполним. Существуют эффект способы нахождения мДНФ. Рассмотрим два из них. Каждый из рассмотренных ниже методов состоит из двух этапов:-построение сокращенной ДНФ;-построение матрицы покрытий. Построение МДНФ. Тупиковой ДНФ (ТДНФ) функции f называется такая ДНФ ее простых импликант, из которых нельзя выбросить ни одного импликанта, не изменив функции f. Теорема. Всякая минимальная ДНФ некоторой функции является ее тупиковой ДНФ. Для получения МДНФ функции f необходимо построить все ТДНФ функции f и выбрать те из них, которые содержат минимальное число букв. КДНФ - каноническая дизъюнктивная нормальная форма

20) Алгоритм проектирования комбинационных схемПод комбинац схемой (КС) поним лог (цифр) сх, вх сигналы кот зависят только от значений вх сигналов в данный момент времени и не зависят от предшествующ вх и вых сигналов. Можно сказать, что КС - это правильная схема, постр из функц элементов, явл автоматами без памяти.правильной называют лог сх без обратных связей, соедин эл-тов в кот выполнены по правилам, соответ в функц отношении операции суперпозиции ф-й.Осн задачами теории КС явл задачи анализа и синтеза схем.Задача анализа состоит в нахожд общ конструктивн приема (алгоритма), позволяющ по любой КС построить ф-ю этой сх и по ней опр зав-ть сигнала на каждом из ее вых от сигналов на вх. Решение задачи состоит в выписывании суперпозиц ф-й, опред соединением эл схемы.Задача синтеза КС сводится к представ реализ ф-й в виде суперпозиции ф-й, реализ некоторым заранее заданным набором лог эл-ов.(Р)Данный алг м\видоизм-ся в конкр условиях проектирования.

21) Этапы синтеза КС:I Этап.1. По данному алг работы устр-ва выд независ перем (выходы датчиков, ключей, кнопок и т.п.).2. Выдел вых сигн схемы. Отмеч знач вых на кажд наборе аргум. Пров-ся независ состояния вых от последоват появл вх наборов. Е. зав-ть наблюд-ся, то это неКС и нужно пользоваться дрметодами.3. Состав табл истин или структур формула ф-и.II Этап.Провод-ся минимиз бул ф-и известн способами.III Этап.Мин дизъюнктивная норм форма предст-ся в виде суперпоз-и элементар наборов в зав-ти от элементн базиса, имеющегося от разработчика.

22)Приведение

булевых функций к данному функциональному

базису и построение функциональной

схемыД\получ

функц сх, соответствующ заданной ф-и

ал, необходимо выразить ф-ю в некот

функцион-полном базисе и сопост каждой

элементар ф-и функцион элемент ей

соответствующ. Процесс такого преобразов

сост в последовательн декомпоз исх

формы представлен зад ф-и на подф-и,

представле в зад функц базисе и

продолжается до тех пор, пока не будет

найдена эквивалент БФ в требуемом

базисе.Разработать КС для системы охр

сигнализ, кот выдает сигнал тревоги

если сраб 1из2датчиков на окнах или

датчик на вх двери или вместе и нет

сигнала снятия тревоги с пульта.I

Этап.Выделим одно исполн уст-во - электрич

сирену и 4 датч -2на окнах,1на двери и

датч снятия сигнала

тревоги с пульта охр. Введем обозначения:

Х1--сигнал

датч1окна, Х2-датч2окна,Х3-датч

дверей, Х4-снятия

тревоги с пульта. Сигн вкл электрич

сирены представ собой лог ф-ю вида:

у=f(X1,X2,X3,X4).

Построим Табл.истин д\функции у на

основе словесного алгоритма работы

схемы. Получим запись функции![]() II

Этап.Выполним минимиз лог, использ к

Карно. Получим:

II

Этап.Выполним минимиз лог, использ к

Карно. Получим:![]() III

и IV Этапы.Рассмотрим полученные функции

у в различ базисах.В баз 2И-НЕ

получим:

III

и IV Этапы.Рассмотрим полученные функции

у в различ базисах.В баз 2И-НЕ

получим:![]() Обозначим

Обозначим

![]() Постр

сх в базисе 2ИЛИ-НЕ.Обозначим

Постр

сх в базисе 2ИЛИ-НЕ.Обозначим

![]()

![]() Попробуем

использовать базис 2И–НЕ, 2ИЛИ

Попробуем

использовать базис 2И–НЕ, 2ИЛИ![]() М\построить

бесконеч число вариантов эквивал функц

схем.схемы будут эквивал логически, но

не схемотехнически (по кол-ву функц

эл-ов, корпусов, v

и s).

М\построить

бесконеч число вариантов эквивал функц

схем.схемы будут эквивал логически, но

не схемотехнически (по кол-ву функц

эл-ов, корпусов, v

и s).

24)

Синтез КС с несколькими выходамиКС

с несколькими выходами м\б описано

системой бул ф-й вида:т.е она должна на

одних и тех же наборах вх перем формир

несколько вых разрядов.Нетрудно понять,

что существует тривиальный метод

проектирования КС с нескольикми

выходами, который заключается в том,

что каждая функция из системы реализуется

отдельно КС. При этом структура такой

КС будет иметь вид:Такой метод реализации

является заведомо избыточным, т.к.

функции, входящие в систему могут

содержать одинаковые ЭК или скобочные

выражения. Известен метод совместной

минимиз системы БФ, который заключается

в нахождении совместных импликант и

построении МДНФ системы функции через

такие импликанты. Данный метод

предусматривает нахождение всех

конъюкций вида:Процесс построения

таких произведений достаточно трудоемок,

а результаты совместной минимизации

часто оказываются незначительными для

КС средней сложности (n = 3

![]() 6,

m = 3

6).При

n и m больших, чем 6-7 реализация метода

совместной импликации вручную становится

практически невозможной. Поэтому, с

точки зрения инженерной практики,

целесообразно выполнять минимизацию

функций системы (4.4.1.) по отдельности,

а затем найти или выделить совпадающие

ЭК или более сходные фрагменты. При

этом открываются широкие возможности

поиска оптимальных реализаций, как и

для КС с одним выходом

6,

m = 3

6).При

n и m больших, чем 6-7 реализация метода

совместной импликации вручную становится

практически невозможной. Поэтому, с

точки зрения инженерной практики,

целесообразно выполнять минимизацию

функций системы (4.4.1.) по отдельности,

а затем найти или выделить совпадающие

ЭК или более сходные фрагменты. При

этом открываются широкие возможности

поиска оптимальных реализаций, как и

для КС с одним выходом

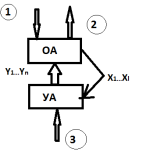

25АвтоматноепреобразованиеинформацииРезультат

преобразования в\в зависит не только

от того какая информация появилась на

вх , но и от предысто преобразования.

Сущ более сложные не функц преобразов

инфо. Их реализ зависит не только от вх

но и от того что было на вх раньше. Такие

преобразов называют автоматами.Число

возможных вх историй бесконечно. На

мн-ве предыст вводится отнош эквивал-ти.

2 предыст считают эквивал,е.они одинаковым

образом, влияют на дальнейш поведение

автомата. Для своего функционир автомат

не обязательно должен запоминать все

вх истории. Достаточно запомнить класс

эквивал кот принадлежит та или иная

история. Ситуация, когда кол-во классов

эквивал вх истории конечно, явл

простейшей. Соответств вх модель назыв

конечн автоматным преобразоват инфо

или КА.Внутр сост автом назыв класс

эквивален его вх историй. Неформально

состояние системы - это хар-ка, однозначно

определяющ ее дальнейш поведение, а

также все последующ реакции системы

на внеш события.На1 и тот же вх сигнал

КА может реагир по-разному, в зав-ти от

того в каком состоянии он находится в

данный момент.Сост представл собой

класс эквивал предысторий вх, сост

м\изменятся только при прих очередн вх

сигнала. При получ вх сигнала КА выдает

не только инфо на вх как ф-ю этого вх

сигн и сост, но и меняет свое состояние.

Функц автомата удобно представлять

графВ

БП

автомата хранит инф. о текущ сост S,

кот вместе с вх сигн х опред вых реакцию

авт-а y

и след состояние S'.

На вход КА в каждом такте поступает

один из возможных вх сигн, а на его вых

появляется вых сигнал, явл ф-й его текущ

сост и поступивш вх сигн внутрен сост

также меняется. Моменты сраб определ

либо принудительно (тактирующим

синхросигналом), либо асинхронно

(наступление внешнего события).КА: S-конечное

непустое множество множества

состояний.Х--конечное непустое множество

входных сигналов (входной алфавит)У--конечное

непустое множество выходных сигналов

(выходной алфавит)s0-

начальное состояние;

S-конечное

непустое множество множества

состояний.Х--конечное непустое множество

входных сигналов (входной алфавит)У--конечное

непустое множество выходных сигналов

(выходной алфавит)s0-

начальное состояние;

-функция

перехода.

-функция

перехода.

-функция

выходов.Представление КА: графическое,

табличное

-функция

выходов.Представление КА: графическое,

табличное

26 Реализация конечных автоматов:2реализации: программная,аппаратнаяПрограммная(составление блок схем программ работы автомата и самой программы)Пример: Автомат .Топология блок схемы прогр повторяет топологию графа. С каждым состоянием связана операция NEXT, выполняющ функц ожид очередн сигн и чтение его в некоторый станд буфер и послед анализ, какой это сигнал. В зав-ти от того, какой сигнал пришел на вход, выполняется та или иная ф-я(Y0..Y5), и происходит переход к след состоянию. АппаратнаяТребует построения ус-в памяти для запом текущ состояния автомата (триггеры).Функциональный блок автомата реализуется как конечный преобразователь.Общий подход к реализации:1) кодирование вход и вых сигналов двоичном виде2)по таблицам переходов и вых составляются кодир таблицы переходов и вых.3) по код табл проводится минимиз двоичн ф-й в зад базисе4) решаются вопросы синхронизации, т.е. привязки моментов выдачи выходного сигнала и изменения состояния внутр памяти моментным поступлением вх сигналов.

28

Минимизация конечных автоматов.Разные

автоматы могут функц одинаково даже,

е. у них разное число состояний. Важной

задачей явл нахождение мин автомата,

кот реализ заданное автоматн отображ.

Эквивалент естеств считать 2 автомата

которые нельзя различить никакими вх

сигналами. 2 состояния P

и Q

некоторого автомата А называются эквив

если справедливо след утверждение. Люб

цепочка поданная на автомат в состоянии

q0

даст такую же реакцию как, когда автомат

находится в состоянии q2.Эквивал

состояния м\объединять в 1класс,

состоянием кот явл классы эквивалент

состояний.Е.мы можем опред на мн-ве сост

автомата макс возможные разбиения на

классы, то выбирая классы эквивал как

новое состояние получим мин автомат

эквивалент исходному.Сущ алгоритм

опред мин отношения эквивалент на мн-ве

состояний КА.Алгоритм состоит в

последовательном построении на мн-ве

состояний автомата А классов разбиений,

таких что в1класс разбиения

Люб

цепочка поданная на автомат в состоянии

q0

даст такую же реакцию как, когда автомат

находится в состоянии q2.Эквивал

состояния м\объединять в 1класс,

состоянием кот явл классы эквивалент

состояний.Е.мы можем опред на мн-ве сост

автомата макс возможные разбиения на

классы, то выбирая классы эквивал как

новое состояние получим мин автомат

эквивалент исходному.Сущ алгоритм

опред мин отношения эквивалент на мн-ве

состояний КА.Алгоритм состоит в

последовательном построении на мн-ве

состояний автомата А классов разбиений,

таких что в1класс разбиения попадают k

состояния, которые неразличимы вх

цепочками длинной k.

Такие

состояния счит находящ в отнош эквивалент

k.

Если

выполняется условие

попадают k

состояния, которые неразличимы вх

цепочками длинной k.

Такие

состояния счит находящ в отнош эквивалент

k.

Если

выполняется условие

,

то тогда p и q называются к-различимыми.

,

то тогда p и q называются к-различимыми. Очевидно,

что все состояния в автомате ноль

эквивалентны, при подаче пустых цепочек

на вх автомата, вых также явл пустая

цепочка независ от состояния , в кот

находится автомат.Разбиение пи1 легко

построить. В один блок пи1 попадают все

состояния, в которых автомат одинаково

реагирует на входные сигналы.

Очевидно,

что все состояния в автомате ноль

эквивалентны, при подаче пустых цепочек

на вх автомата, вых также явл пустая

цепочка независ от состояния , в кот

находится автомат.Разбиение пи1 легко

построить. В один блок пи1 попадают все

состояния, в которых автомат одинаково

реагирует на входные сигналы.

Разбиение

пи0 содержащее один единственный блок,

в который входят все состояния автомата

и разбиения пи1, в каждом блоке которого

собрано состояние неразличимое входными

сигналами, является исходным при

построении цепочки разбиения

Определив

как строится след распред из предыдущ,

м\построить всю цепочку. Теорема: Если

Разбиение

пи0 содержащее один единственный блок,

в который входят все состояния автомата

и разбиения пи1, в каждом блоке которого

собрано состояние неразличимое входными

сигналами, является исходным при

построении цепочки разбиения

Определив

как строится след распред из предыдущ,

м\построить всю цепочку. Теорема: Если

,

то для того чтобы

,

то для того чтобы

необходимо и достаточно чтобы выполнялось

следующ условие

необходимо и достаточно чтобы выполнялось

следующ условие Для

того что бы 2 к-эквивалент КА были бы

л+1-эквивалентн необходимо и достаточно,

чтобы под возд любого вх сигнала автомат

переходил в пару состояний, который

были бы к- эквивал.Д \т, чтобы вх цепочка

длинны к+1 не различала пару состояний

p и q нужно, чтобы автомат из этих

состояний переходил под воздействие

x0

в такие состояния, которые не различимы

цепочкой (x1

, x2

,… xk),

т.е.

Для

того что бы 2 к-эквивалент КА были бы

л+1-эквивалентн необходимо и достаточно,

чтобы под возд любого вх сигнала автомат

переходил в пару состояний, который

были бы к- эквивал.Д \т, чтобы вх цепочка

длинны к+1 не различала пару состояний

p и q нужно, чтобы автомат из этих

состояний переходил под воздействие

x0

в такие состояния, которые не различимы

цепочкой (x1

, x2

,… xk),

т.е.

и

и

были бы к-неразличимым.

были бы к-неразличимым.

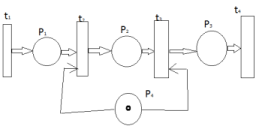

31.

Моделирование систем и событий с помощью

сетей Петри.Реал

система функц во времени, событии

происходит в нек момент времени и

действует нек время. В синхр моделях

дискретн систем события явно привязаны

к некоторым моментам или интервалам

времени, в кот происх одноврем измен

состояния все компонентов системы,

т.е. измен состояния всей системы в

целом. Смена состояния системы происходит

последовательно. В с Петри обычно

отказываются от введения дискр времени

и тактированных последоват изменения

состояний, заменяя их причинно-следств

связями м\у событиями. Если же возникает

необход осуществит привязку ко времени,

то моменты или интервалы времени

представляют как события. Т.о. синхронные

системы могут описываться в терминах

асинхронных моделей. Отказ от времени

приводит к тому, что события в асинхр

модели просматрив как элементар или

составные. Взаимодействие событий в

сложных асинхр системах имеет как

правило сложн динам структуру. Глоб

ситуации в системе формир с пом-ю лок

операций, кот наз-ся условиями реализации

событий. Д\реш указанных задач дискр

системы достаточ представить, как

структуры, образованные из элементов2типов:

события и условия. В с.Петри они

представлены абстракт символами из 2

непересекающ алфавитов или мн-в, кот

назыв-ся соответств мн-вами позиций и

переходов. Условия и события переходы

связаны отнош непосредств зав-ти, кот

изображ с пом-ю направленных дуг.

Е.возникает необх-сть осущ привязку ко

времени, то моменты или интервалы

времени представ как события

С=(Р,Т,Е,W,М)

Р-множество позиций; Т-множество

переходов; Е-отношение инцидентности;

М-начальная маркировка сети; W-функция,

задающая кратность дуг.

![]() Выполнен

условий изображается разметкой, т.е.

помещением некоторого числа фишек в

позиции и места. Неформально работу

сетей можно представить как совокупность

локальных действий, которые называются

срабатыванием переходов. Они соответствуют

реализациям событий и приводят к

изменению разметки позиций, т.е. к

локальному изменению условий в системе.

С=(Р,Т,I,О)тождественно(Р,Т,Е).Маркировка

заключ в присвоении фишек или маркеров

позициям с.Петри. При работе сети фишки

в кружках перемещаются в выходные

позиции. Переход может сработать только

тогда, когда он разрешен.Е.в системе

нет одного перехода готового к

срабатыванию – это тупиковая ситуация.

Динамика сети Петри отражается в

изменении маркеровки. Пример:

Выполнен

условий изображается разметкой, т.е.

помещением некоторого числа фишек в

позиции и места. Неформально работу

сетей можно представить как совокупность

локальных действий, которые называются

срабатыванием переходов. Они соответствуют

реализациям событий и приводят к

изменению разметки позиций, т.е. к

локальному изменению условий в системе.

С=(Р,Т,I,О)тождественно(Р,Т,Е).Маркировка

заключ в присвоении фишек или маркеров

позициям с.Петри. При работе сети фишки

в кружках перемещаются в выходные

позиции. Переход может сработать только

тогда, когда он разрешен.Е.в системе

нет одного перехода готового к

срабатыванию – это тупиковая ситуация.

Динамика сети Петри отражается в

изменении маркеровки. Пример:

Требуется

описать с помощью сПетри работу группы

пользователей на единств рабочей

станции при зад хар-ках потока запроса

на её использование и хар-ках поступ

задач.

Требуется

описать с помощью сПетри работу группы

пользователей на единств рабочей

станции при зад хар-ках потока запроса

на её использование и хар-ках поступ

задач. -

поступл запроса на использ станции;

-

поступл запроса на использ станции;

-

занятие станции;

-

занятие станции;

-освобожд

станции;

-освобожд

станции;

-

выход обслуж заявки.

-

выход обслуж заявки.

используется д\отображения состояния

станции, если в

есть метка, это означает, что станция

свободна и пришедш заявка вызывает

срабатывание

,

пока заявка не будет обработана.

используется д\отображения состояния

станции, если в

есть метка, это означает, что станция

свободна и пришедш заявка вызывает

срабатывание

,

пока заявка не будет обработана.

32.

Расширения сетей Петри.Ингибиторные

сети

– это сПетри, дополн спец ингибиторными

дугами. Переход в ингибит сети может

сработать , если каждая его вх поз ,

соедин с переходом обычной дугой

кратностью W(P,t)

,содержит не менее W(P,t)

фишек . А кажд вх поз, соедин с переходом

ингибит дугой , имеет нул разметку .

Весь вес ингибит дуги всегда равен

1.Приоритетные

сПетри.Здесь

вводятся приоритеты срабатывания

переходов.Если в сети существует

несколько переходов готовых к

срабатыванию. Структурированные

сПетри.Здесь

некоторые из переходов явл. сложными.

При их срабатывании запускается сеть,

др условия иерархии исп-ся для моделир

модульн вычислит систем.Цветные

сП.Введение

набора цветов фишек исп-ся для моделир

аппаратн средств фишек использ

д\моделирования аппарат средств.Сети

с измен структурой, кратность ребер не

явл постоянной. Существуют временные

с П.,

в них переходам ставится в соответствующее

время нахождения фишки внутри этой

позиции.Стахостические

сети.Элементарные сети П.-

может одновременно присутствовать

только1фишка, вес дуг всегда еденица.Сущ-ют

сети П. высокого

уровня –

наличие возможности применять

цвета.Дискретные

непрерывные сети П.:ДНСП= Уравнение

динамики для непрерывных сПетри:

Уравнение

динамики для непрерывных сПетри: ,

, -

функция;

-

функция;

-

управляющий вектор;

-

управляющий вектор;

-

транспонированная матрица.Элементы

управл.вектора принимают значения 0

или 1, 1 - если даны переход готов к

срабатыванию , 0- если нет.

отражает

структуру сети, показывает какое

количество фишек перем-ся между позицией

и переходом.Вложенные

сети П.

состоят из сист сети и элемент сетей,

представляющ собой обыкнов сети П. Во

вложенных сетях существуют элементарн

и сетевые фишки.Динамика поведения в

ложной сети харак-ся 4-мя шагами:1.

срабатыв переходов сист сети в соот-ии

с паравилами; 2. срабатывание преходов

в элемент сетях; 3. шаг гор синхронизации,

срабатывание переходов, помеченных

особым символом; 4. шаг вертик

синхронизации.Гибридные

сети отличаются математическим

описанием.

-

транспонированная матрица.Элементы

управл.вектора принимают значения 0

или 1, 1 - если даны переход готов к

срабатыванию , 0- если нет.

отражает

структуру сети, показывает какое

количество фишек перем-ся между позицией

и переходом.Вложенные

сети П.

состоят из сист сети и элемент сетей,

представляющ собой обыкнов сети П. Во

вложенных сетях существуют элементарн

и сетевые фишки.Динамика поведения в

ложной сети харак-ся 4-мя шагами:1.

срабатыв переходов сист сети в соот-ии

с паравилами; 2. срабатывание преходов

в элемент сетях; 3. шаг гор синхронизации,

срабатывание переходов, помеченных

особым символом; 4. шаг вертик

синхронизации.Гибридные

сети отличаются математическим

описанием.

33.

Понятие структурного синтеза автоматов.

Теорема о структурной полноте.Процесс

постр сх автомата обычно разделяют на

две стадии: 1.абстрактный синтез; 2.

структурный синтез.На стадии абстр.

Синтеза вып-ся построение табл переходов

и выходов автомата. На стадии структ.

синтеза вып-ся схемная реализация

абстрактного автомата, т.е. строится

структ. автомат из более простых

автоматов, называемых элементарными.

Элементарные автоматы бывают двух

видов: авт-т с памятью, имеющие более

одного состояния и авт-ты без памяти –

с одним состоянием. Авт-ты с памятью

наз-ют элементами памяти или запоминающие

элементы, авт-ты без памяти – комбинационные

или лог элементы. Элементы памяти

соединяются между собой с помощью лог

элементов (и, или, не). При структурном

синтезе авт-та необходимо выбрать

систему элементов, из которых в дальнейшем

будет строиться авт-т. Д.т.ч м\б построить

сх любого КА, такая система авт-ов должна

быть структурно полной. Теорема:

система

элемент авт-ов, содержащ функцион полную

систему логич эл-ов, хотя бы один авт-т

Мура с памятью, обладающ полной сист

перех и полн сист вых, явл структурно

полной. Полнота перех в автоматах

означает след-ее: для люб пары состояний

сущ

хотя бы один вх сигнал, к-ый переводит

авт-т из состояния

сущ

хотя бы один вх сигнал, к-ый переводит

авт-т из состояния

в сост-ие

в сост-ие

.

В авт-те, обладающ полной сист перех

д\встречаться все состояния. Полнота

выхода авт-та отлич следующ: в кажд сост

автомат выдает вых сигнал, отличн от

сигналов, выдаваемых в др. состояниях.

Требование полноты сист вых связано с

необходим различ внутр сост элементар

авт-ов. Т.к. в авт-те, необладающ полн

сист вых различ сост невозм=>невозмож

обеспеч зад усл функционир системы.

Авт-т Мура удовлетворяет требованиям

и полноте системы и выходов. Цель

структурного синтеза авт-та заключается

в построении цифр схемы авт-та на основе

системы лог уравн, в кот записыв завис

вых сигналов авт-тв и сигн, подав на вх

запом эле-ов от вх сигналов авт-та и

сигн с вых элем-ов памяти.

.

В авт-те, обладающ полной сист перех

д\встречаться все состояния. Полнота

выхода авт-та отлич следующ: в кажд сост

автомат выдает вых сигнал, отличн от

сигналов, выдаваемых в др. состояниях.

Требование полноты сист вых связано с

необходим различ внутр сост элементар

авт-ов. Т.к. в авт-те, необладающ полн

сист вых различ сост невозм=>невозмож

обеспеч зад усл функционир системы.

Авт-т Мура удовлетворяет требованиям

и полноте системы и выходов. Цель

структурного синтеза авт-та заключается

в построении цифр схемы авт-та на основе

системы лог уравн, в кот записыв завис

вых сигналов авт-тв и сигн, подав на вх

запом эле-ов от вх сигналов авт-та и

сигн с вых элем-ов памяти.

34. Типы элементарных автоматов памяти. Триггеры.В настоящ время в выч технике используются элементар автоматы, имеющие след особенности:1. Элементарн авт-ты явл автом Мура с2внутрен состоян;2. Авт-т выдает 2различных вых сиг, соответс 2его внутр состояниям;3. Элемент авт-ты м\иметь в общем случае несколько физич вх, на каждый из которых могут подавать сигналы, закодированные цифры 0 и 1.

![]() В

кач-ве эл-ых авт-ов в выч технике обычно

исп-ся триггеры различных типов. Триггер-

это устр-во, имеющ 2сост, в кот он переходит

под действием вх сигналов. Выделяют

информац и синхросигн. Информац сигналы

определяют новое состояние триггера

и присутствуют в люб триггерах. По типу

инф. сигналов сущ-ют след класс-ция

триггеров:D,T,RS,JK

– триггеры. RST,DV

– триггеры и т.д.Синхросигн С не явл

обяз и вводится в триггерах с целью

фиксац мом перехода триг в новое сост,

на него поступают импульсы генератора,

синхронизир работу цифр авт-та. Период

следования импульсов соответст1такту

автоматн времени.Т-триггер назыв авт-т

Мура с2уст-ми состояниями и 1входом,

к-ые изменяют свое сост на противополож,

когда на вх поступает новый вх сигнал.

Т- триггер наз-ют триггером со счетным

входом. В соответствии с состоянием,

принимаемым триггером, вход S-

единичный, R-

нулевой, поэтому переход в триггере не

определен.Таблица переходов:

В

кач-ве эл-ых авт-ов в выч технике обычно

исп-ся триггеры различных типов. Триггер-

это устр-во, имеющ 2сост, в кот он переходит

под действием вх сигналов. Выделяют

информац и синхросигн. Информац сигналы

определяют новое состояние триггера

и присутствуют в люб триггерах. По типу

инф. сигналов сущ-ют след класс-ция

триггеров:D,T,RS,JK

– триггеры. RST,DV

– триггеры и т.д.Синхросигн С не явл

обяз и вводится в триггерах с целью

фиксац мом перехода триг в новое сост,

на него поступают импульсы генератора,

синхронизир работу цифр авт-та. Период

следования импульсов соответст1такту

автоматн времени.Т-триггер назыв авт-т

Мура с2уст-ми состояниями и 1входом,

к-ые изменяют свое сост на противополож,

когда на вх поступает новый вх сигнал.

Т- триггер наз-ют триггером со счетным

входом. В соответствии с состоянием,

принимаемым триггером, вход S-

единичный, R-

нулевой, поэтому переход в триггере не

определен.Таблица переходов:

-

R

S

0

0

0

0

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

0

1

0

1

0

1

1

0

-

1

1

1

-

Таблица функций:

-

S

0

0

х

0

0

1

0

1

1

0

1

0

1

1

0

х

J |

K |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

является безразличным, поэтому стоит

в таблице переменная х, к-ая может

принимать два значения 0 или 1. Аналогично

1 в 1 при R=0

S=0,

R=0

S=1,

поскольку при таком переходе S-

безразлично, то переменная х. Авт-ты,

к-ые могут переходить из одного состояния

в другое под действтем нескольких

комбинаций входных сигналов, наз-ся

авт-ми с избыточной системой переходов.

Избыточность можно использовать для

упрощения схемы, придавая переменной

х такие значения, которые позволяют

минимизировать число элементов, поэтому

если схемы двух элементарных автоматов

равноценны по сложности, то предпочтение

авт-ту, имеющему большую систему

переходов.Закон функционирования

является безразличным, поэтому стоит

в таблице переменная х, к-ая может

принимать два значения 0 или 1. Аналогично

1 в 1 при R=0

S=0,

R=0

S=1,

поскольку при таком переходе S-

безразлично, то переменная х. Авт-ты,

к-ые могут переходить из одного состояния

в другое под действтем нескольких

комбинаций входных сигналов, наз-ся

авт-ми с избыточной системой переходов.

Избыточность можно использовать для

упрощения схемы, придавая переменной

х такие значения, которые позволяют

минимизировать число элементов, поэтому

если схемы двух элементарных автоматов

равноценны по сложности, то предпочтение

авт-ту, имеющему большую систему

переходов.Закон функционирования

-

триггеров:

-

триггеров:

при

при

-

триггеры- универсальный авт-т Мура с

двумя усталостными состояниями и двумя

входами J

и K,

в котором приусловии JxK=1

осуществляет инверсию предыдущего

состояния, а в остальных случаях

функционирует в соответствии с таблицей

истинности

-

триггеры- универсальный авт-т Мура с

двумя усталостными состояниями и двумя

входами J

и K,

в котором приусловии JxK=1

осуществляет инверсию предыдущего

состояния, а в остальных случаях

функционирует в соответствии с таблицей

истинности

-

триггеров, при этом вход

-

триггеров, при этом вход

эквивалентен

входу S,

а вход К входу R.

Этот триггер не имеет запрещенной

комбинации входных сигналов, а таблица

истинности имеет след-ий вид:

Q(t+1)=f(J,K,Q(t)

эквивалентен

входу S,

а вход К входу R.

Этот триггер не имеет запрещенной

комбинации входных сигналов, а таблица

истинности имеет след-ий вид:

Q(t+1)=f(J,K,Q(t)

Триггер относится к разряду универсальных, т.к. на его основе можно построить RS,D,T- тригерры. RS тр. получается из JK – триггера наложением ограничений на комбинацию входных сигналов J=K=1, т.к. эта комбинация является запрещенной для RS – триггеров.

![]() Счетный

триггер получается путем объединения

входов

и

К.

Счетный

триггер получается путем объединения

входов

и

К.

-

триггер строится путем подключения к

входу инвектора, на который подается

тот же сигнал что и на вход J.

В этом случае вход J

выполняет функцию входа D,

а все устройство в целом реализует

таблицу переходов D-

триггера. В интегральной технике

применяется только синхронные JK-

триггеры, которые при С=0 сохраняют свое

состояние, а при С=1 работают как

асинхронные триггеры.

-

триггер строится путем подключения к

входу инвектора, на который подается

тот же сигнал что и на вход J.

В этом случае вход J

выполняет функцию входа D,

а все устройство в целом реализует

таблицу переходов D-

триггера. В интегральной технике

применяется только синхронные JK-

триггеры, которые при С=0 сохраняют свое

состояние, а при С=1 работают как

асинхронные триггеры.

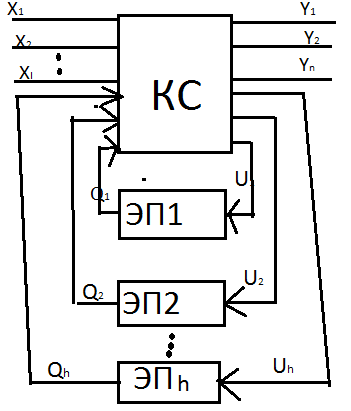

35.

Канонический метод структурного синтеза

авт-та.На

стадии абстрактного синтеза обычно

используется представление авт-та в

виде1блока, имеющ 1вх и 1вых. На стадии

структур синтеза авт-та авт-т изображают

в виде обобщенной структурн схемы, в

которой есть l-входных

и l-выходных

сигналов, по которым предаются движения

сигналов

(входные

переменные) и

(входные

переменные) и

(

выходные переменные или функции выхода

авт-та.

(

выходные переменные или функции выхода

авт-та.

П редставляется

обобщенная схема авт-та, состоящая из

двух частей: комбинационной схемы и

набора элементов памяти. Переменные

редставляется

обобщенная схема авт-та, состоящая из

двух частей: комбинационной схемы и

набора элементов памяти. Переменные

соответствуют выходным сигналам

элементов памяти, называют внутренними

переменными авт-та.

соответствуют выходным сигналам

элементов памяти, называют внутренними

переменными авт-та.

используются в схеме для обозначения

сигналов, изменяющих состояние элементов

в памяти. Их называют функциями

возбуждения. В качестве элементов

памяти на практике чаще всего используют

элементарные авт-ты, которые имеют

только входные и выходные линии. Каждое

состояние абстрактного авт-та

кодируются в структурных авт-ах набором

состояний элементов памяти. Если все

авт-ты одинаковые, то их число определяется

следующим выражением R≥

используются в схеме для обозначения

сигналов, изменяющих состояние элементов

в памяти. Их называют функциями

возбуждения. В качестве элементов

памяти на практике чаще всего используют

элементарные авт-ты, которые имеют

только входные и выходные линии. Каждое

состояние абстрактного авт-та

кодируются в структурных авт-ах набором

состояний элементов памяти. Если все

авт-ты одинаковые, то их число определяется

следующим выражением R≥ .

M-

число состояний синтезируемого авт-та.

b-

число состояний элементарного авт-та.

Обычно для элементарного авт-та b=2=>

R≥

.

M-

число состояний синтезируемого авт-та.

b-

число состояний элементарного авт-та.

Обычно для элементарного авт-та b=2=>

R≥ .

В отличие от абстрактного авт-та,

имеющего один входной и один выходной

канал, структурный авт-т имеет l-входных

и n-

выходных каналов. Каждый входной и

выходной сигнал абстрактного авт-та