- •Курс лекций «Вычислительные машины, системы и сети»

- •Часть 1. Вычислительные машины. 3

- •Часть 2. Вычислительные системы. 202

- •1.3 Материнская плата

- •1.4 Процессор

- •1.5 Устройства хранения данных

- •Лекция 2. Эволюция микрокомпьютеров.

- •1.1.Основные направления эволюции микрокомпьютеров.

- •Лекция 3. Машинная организация процессора 80286

- •1.1. Введение.

- •2.2. Структура памяти.

- •2.3. Сегментация памяти.

- •2.4. Структура ввода-вывода.

- •2.5. Регистры.

- •Лекция 4. Операнды и режимы адресации операндов.

- •Лекция 5. Общая организация памяти.

- •Лекция 6. Прерывание микропроцессора в эвм.

- •Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •Обработка прерываний в персональной эвм

- •Лекция 7. Последовательный интерфейс rs–232c.

- •Общие сведения о интерфейсе rs–232c

- •Виды сигналов

- •Тестовое оборудование для интерфейса rs–232c

- •Лекция 8. Последовательный интерфейс сом-порт.

- •Использование сом-портов

- •Функции bios для сом-портов

- •Сом-порт и РпР

- •Лекция 9. Программируемый связной интерфейс.

- •Лекция 10. Передача данных между эвм с помощью модемов. Типы и характеристики модемов.Набор ат-команд.

- •Ат-команды

- •Лекция 11. Программируемый периферийный интерфейс.

- •Лекция 12. Параллельный интерфейс:lpt-порт. Понюхов е. В.

- •Интерфейс Centronics

- •Сигналы интерфейса Centronics

- •Традиционный lpt-порт

- •Функции bios для lpt-порта

- •Расширения параллельного порта

- •Физический и электрический интерфейс

- •Режимы передачи данных

- •Полубайтный режим ввода — Nibble Mode

- •Конфигурирование lpt-портов

- •Использование параллельных портов

- •Неисправности и тестирование параллельных портов

- •Лекция 13. Программируемые таймеры и счетчики событий.

- •Лекция 14. Универсальная последовательная шина usb.

- •2.Шина usb.Общая характеристика.

- •Структура usb

- •3.Физический интерфейс

- •Протокол

- •Устройства usb - функции и хабы

- •Хост-контроллер

- •Лекция 15. Протокол работы usb-шины.

- •Описание протоколов используемых при передаче данных Структура usb пакета

- •Поля usb пакета

- •Типы usb пакетов

- •Приоритеты передач по usb-шине

- •Источники информации

- •Лекция 16. Интерфейс ieee-1394 (FireWire).

- •Технические характеристики

- •Топология шины

- •Пример топологии ieee-1394

- •Совместимость

- •Кабели и разъемы

- •Список литературы

- •Лекция 17. Организация прямого доступа к памяти.

- •Лекция 18. Устройства ввода эвм. Клавиатура. Введение

- •1. Основные части клавиатуры

- •1.1. Клавиши пишущей машинки (алфавитно-цифровая клавиатура)

- •Режимы ввода символов

- •Названия специальных знаков

- •1.2. Служебные клавиши

- •Индикаторы режимов

- •Клавиши управления курсором

- •1.3. Функциональные клавиши

- •1.4. Малая цифровая клавиатура

- •2. Принципы работы клавиатуры

- •Лекция 19. Интерфейс эвм с видеотерминалом. Видеоадаптер. Режимы изображений: текстовый и графический режимы. Видеопамять. Анимация изображений. Интерфейс эвм с видеотерминалом.

- •Видеоадаптер.

- •Лекция 20. Накопитель магнитных дисков: гибкий и жесткий. Структура дисков: дорожки, сектора, блоки. Обмен информации между эвм и магнитными дисками.

- •Лекция 21. Сканер. Считывание изображения. Типы обрабатываемых изображений. Качество изображения.

- •Лекция 22. Назначение и функции операционной системы.

- •Часть 2. Вычислительные системы. Лекция 23. Классификация систем параллельной обработки данных.

- •Сеть с топологией кольцо

- •Литература

- •Лекция 24. Классификация мультипроцессорных систем по способу организации основной памяти.

- •Лекция 25. Обзор архитектур многопроцессорных вычислительных систем.

- •Лекция 26. Направление развития в высокопроизводительных вычислительных системах.

- •Универсальные системы с фиксированной структурой

- •Направления развития микропроцессоров

- •Системы с фиксированной структурой из серийных микропроцессоров

- •Специализированные системы с фиксированной структурой

- •Специализированные системы с программируемой структурой

- •Технологическая база развития современных архитектур

- •Архитектуры многопотоковых процессоров

- •Кластер Green Destiny

- •Программируемый микропроцессор

- •Однородные вычислительные среды

- •Литература

- •Однокристальный ассоциативный процессор сам2000

- •Литература

- •Однокристальный векторно-конвейерный процессор sx-6

- •Литература

- •Лекция 27. Принципы построения телекоммуникационных вычислительных систем.

- •2.Компоненты телекоммуникационной системы

- •3. Типы телекоммуникационных сетей.

- •4. Топологии вычислительной сети.

- •5. Модем

- •Часть 3. Вычислительные сети. Лекция 28. Эталонная модель взаимодействия открытых систем.

- •Лекция 29. Локальные вычислительные сети.

- •10Base-2 или тонкий Ethenet

- •10Base-5 или толстый Ethenet

- •2.2.2. Компоненты сети

- •2.2.3. Проводная сеть в умном доме(LexCom Home)

- •Лекция 30. Беспроводные сети на основе службы gprs.

- •Чем привлекательна эта технология?

- •Передача данных: gprs и gsm

- •Что дает абоненту технология gprs?

- •Принципы построения системы gprs

- •Терминальное оборудование gprs

- •Скорости передачи в системе gprs

- •Перспективы развития услуг на базе gprs

- •Перспективы пакетной передачи данных

- •Gprs модемы существуют в нескольких исполнениях:

- •Лекция 31. Беспроводные сети Radio-Ethernet.

- •Заключение

- •Лекция 32. Беспроводные локальные сети на основе Wi-Fi - технологии. Введение.

- •Архитектура, компоненты сети и стандарты

- •Организация сети

- •Физический уровень ieee 802.11

- •Канальный уровень ieee 802.11

- •Типы и разновидности соединений

- •2. Инфраструктурное соединение.

- •4. Клиентская точка.

- •5. Соединение мост.

- •Список использованной литературы:

Системы с фиксированной структурой из серийных микропроцессоров

MPP-системы из серийных микропроцессоров делают возможным сохранение традиционного стиля программирования. Принципиальным ограничением производительности этих вычислительных систем служит сам характер функционирования процессора. Фазы «выборка команды», «дешифрование команды», «выборка операндов» представляют собой «накладные расходы» на собственно необходимое пользователю действие — «исполнение команды». Производительность теряется либо прямо, если фазы выполнения команды реализуются последовательно с минимальными затратами оборудования, либо опосредованно путем увеличения затрат аппаратуры на совмещение фаз разных команд, как в современных микропроцессорах. Однако при этом возрастает объем оборудования микропроцессора, а, следовательно, уменьшается суммарное количество процессоров однокристальной вычислительной системы, вызывая соответствующее уменьшение производительности. В однокристальных векторно-конвейерных процессорах влияние рассматриваемого фактора ограничения производительности снижается, но не исключается полностью.

Специализированные системы с фиксированной структурой

Важность решения некоторых актуальных задач оправдывает построение специализированных вычислительных систем. В качестве яркого представителя этого класса систем можно указать систему GRAPE-6 [8], предназначенную для решения задачи взаимодействия N тел. Существующая конфигурация GRAPE-6 включает 2048 специализированных конвейерных микропроцессоров, каждый из которых имеет 6 конвейеров, используемых для вычисления гравитационного взаимодействия между частицами. GRAPE-6 представляет собой кластер, образованный из 16 узлов, объединенных коммутатором Gigabit Ethernet. Каждый узел состоит из ПК на базе микропроцессора AMD Athlon XP-1800+, функционирующего под управлением ОС Linux, и 4 специализированных плат, объединенных между собой и платами соседних узлов специальными каналами. На каждой плате устанавливается 32 специализированных кристалла GRAPE-6.

Теоретическая пиковая производительность GRAPE-6 — 63,4 трлн. оп./с. На реальной задаче по моделированию формирования внешних планет солнечной системы достигнута производительность 29,5 трлн. оп./с. Для сравнения, кластер Green Destiny, который при решении на 220 универсальных микропроцессорах задачи N тел, моделирующей формирование Галактики с использованием 200 млн. частиц, показывает производительность 38,9 млрд. оп./с.

Универсальные системы с программируемой структурой

Такие вычислительные системы строятся из программируемых логических интегральных схем (ПЛИС), содержащих одну или несколько матриц вентилей и позволяющих программно скомпоновать из этих вентилей в одном корпусе электронную схему, эквивалентную схеме, включающей от нескольких десятков до тысяч интегральных схем стандартной логики [9].

Основная идея архитектуры подобных вычислительных систем состоит в том, чтобы программно настроить схему, реализующую требуемое преобразование данных. В [10] приведено сравнение реализации фильтра на Alpha 21164 и Xilinx XC4085XL–09. Микропроцессор Alpha 21164 выполняет две 64 разрядных операции за такт при тактовой частоте 433 МГц, что эквивалентно производительности 55,7 бит/нс. XC4085XL-09 имеет 3136 программируемых логических блоков и минимальную длительность такта 4,6 наносекунд. Для корректного сравнения можно принять, что один программируемый логический блок реализует 1-битную арифметическую операцию. В этих предположениях производительность ПЛИС равна 682 бит/нс. Таким образом, при реализации фильтра на ПЛИС достигается производительность, в 12 раз большая, чем на микропроцессоре Alpha 21164.

Основная трудность в использовании реконфигурируемых вычислений состоит в подготовке для заданного алгоритма настроечной информации для создания в ПЛИС схемы, реализующей этот алгоритм. Естественно, поскольку ПЛИС создавались для построения электронной аппаратуры, то изготовители обеспечили, в первую очередь, системы подготовки настроечной информации на высокоуровневых языках электронного проектирования, таких, как Verilog и VHDL [11]. Однако эти языки непривычны для разработчиков алгоритмов. Сегодня в качестве языков программирования ПЛИС используются языки описания потоковых вычислений.

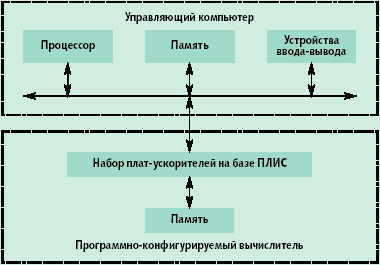

Компания Star Bridge Systems (www.starbridgesystems.com) производит семейство программно реконфигурируемых вычислителей Hypercomputer System HC-X и предлагает комплексное решение для организации реконфигурируемых вычислений (рис. 1). Старшая модель семейства, суперкомпьютер HC-98m, состоит из управляющего компьютера и двухплатного программно реконфигурируемого вычислителя, включающего 14 ПЛИС Virtex-II серии 6000 и 4 Virtex-II серии 4000. В совокупности это составляет 98 млн. вентилей. После включения питания первая ПЛИС программируется из постоянного запоминающего устройства на плате. В этой ПЛИС формируется порт шины PCI-X, через который управляющий компьютер будет, используя среду разработки программ Viva, программировать остальные ПЛИС.

|

|

|

Рис. 1. Структура узла универсальной вычислительной системы, построенного на ПЛИС |