- •Курс лекций «Вычислительные машины, системы и сети»

- •Часть 1. Вычислительные машины. 3

- •Часть 2. Вычислительные системы. 202

- •1.3 Материнская плата

- •1.4 Процессор

- •1.5 Устройства хранения данных

- •Лекция 2. Эволюция микрокомпьютеров.

- •1.1.Основные направления эволюции микрокомпьютеров.

- •Лекция 3. Машинная организация процессора 80286

- •1.1. Введение.

- •2.2. Структура памяти.

- •2.3. Сегментация памяти.

- •2.4. Структура ввода-вывода.

- •2.5. Регистры.

- •Лекция 4. Операнды и режимы адресации операндов.

- •Лекция 5. Общая организация памяти.

- •Лекция 6. Прерывание микропроцессора в эвм.

- •Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •Обработка прерываний в персональной эвм

- •Лекция 7. Последовательный интерфейс rs–232c.

- •Общие сведения о интерфейсе rs–232c

- •Виды сигналов

- •Тестовое оборудование для интерфейса rs–232c

- •Лекция 8. Последовательный интерфейс сом-порт.

- •Использование сом-портов

- •Функции bios для сом-портов

- •Сом-порт и РпР

- •Лекция 9. Программируемый связной интерфейс.

- •Лекция 10. Передача данных между эвм с помощью модемов. Типы и характеристики модемов.Набор ат-команд.

- •Ат-команды

- •Лекция 11. Программируемый периферийный интерфейс.

- •Лекция 12. Параллельный интерфейс:lpt-порт. Понюхов е. В.

- •Интерфейс Centronics

- •Сигналы интерфейса Centronics

- •Традиционный lpt-порт

- •Функции bios для lpt-порта

- •Расширения параллельного порта

- •Физический и электрический интерфейс

- •Режимы передачи данных

- •Полубайтный режим ввода — Nibble Mode

- •Конфигурирование lpt-портов

- •Использование параллельных портов

- •Неисправности и тестирование параллельных портов

- •Лекция 13. Программируемые таймеры и счетчики событий.

- •Лекция 14. Универсальная последовательная шина usb.

- •2.Шина usb.Общая характеристика.

- •Структура usb

- •3.Физический интерфейс

- •Протокол

- •Устройства usb - функции и хабы

- •Хост-контроллер

- •Лекция 15. Протокол работы usb-шины.

- •Описание протоколов используемых при передаче данных Структура usb пакета

- •Поля usb пакета

- •Типы usb пакетов

- •Приоритеты передач по usb-шине

- •Источники информации

- •Лекция 16. Интерфейс ieee-1394 (FireWire).

- •Технические характеристики

- •Топология шины

- •Пример топологии ieee-1394

- •Совместимость

- •Кабели и разъемы

- •Список литературы

- •Лекция 17. Организация прямого доступа к памяти.

- •Лекция 18. Устройства ввода эвм. Клавиатура. Введение

- •1. Основные части клавиатуры

- •1.1. Клавиши пишущей машинки (алфавитно-цифровая клавиатура)

- •Режимы ввода символов

- •Названия специальных знаков

- •1.2. Служебные клавиши

- •Индикаторы режимов

- •Клавиши управления курсором

- •1.3. Функциональные клавиши

- •1.4. Малая цифровая клавиатура

- •2. Принципы работы клавиатуры

- •Лекция 19. Интерфейс эвм с видеотерминалом. Видеоадаптер. Режимы изображений: текстовый и графический режимы. Видеопамять. Анимация изображений. Интерфейс эвм с видеотерминалом.

- •Видеоадаптер.

- •Лекция 20. Накопитель магнитных дисков: гибкий и жесткий. Структура дисков: дорожки, сектора, блоки. Обмен информации между эвм и магнитными дисками.

- •Лекция 21. Сканер. Считывание изображения. Типы обрабатываемых изображений. Качество изображения.

- •Лекция 22. Назначение и функции операционной системы.

- •Часть 2. Вычислительные системы. Лекция 23. Классификация систем параллельной обработки данных.

- •Сеть с топологией кольцо

- •Литература

- •Лекция 24. Классификация мультипроцессорных систем по способу организации основной памяти.

- •Лекция 25. Обзор архитектур многопроцессорных вычислительных систем.

- •Лекция 26. Направление развития в высокопроизводительных вычислительных системах.

- •Универсальные системы с фиксированной структурой

- •Направления развития микропроцессоров

- •Системы с фиксированной структурой из серийных микропроцессоров

- •Специализированные системы с фиксированной структурой

- •Специализированные системы с программируемой структурой

- •Технологическая база развития современных архитектур

- •Архитектуры многопотоковых процессоров

- •Кластер Green Destiny

- •Программируемый микропроцессор

- •Однородные вычислительные среды

- •Литература

- •Однокристальный ассоциативный процессор сам2000

- •Литература

- •Однокристальный векторно-конвейерный процессор sx-6

- •Литература

- •Лекция 27. Принципы построения телекоммуникационных вычислительных систем.

- •2.Компоненты телекоммуникационной системы

- •3. Типы телекоммуникационных сетей.

- •4. Топологии вычислительной сети.

- •5. Модем

- •Часть 3. Вычислительные сети. Лекция 28. Эталонная модель взаимодействия открытых систем.

- •Лекция 29. Локальные вычислительные сети.

- •10Base-2 или тонкий Ethenet

- •10Base-5 или толстый Ethenet

- •2.2.2. Компоненты сети

- •2.2.3. Проводная сеть в умном доме(LexCom Home)

- •Лекция 30. Беспроводные сети на основе службы gprs.

- •Чем привлекательна эта технология?

- •Передача данных: gprs и gsm

- •Что дает абоненту технология gprs?

- •Принципы построения системы gprs

- •Терминальное оборудование gprs

- •Скорости передачи в системе gprs

- •Перспективы развития услуг на базе gprs

- •Перспективы пакетной передачи данных

- •Gprs модемы существуют в нескольких исполнениях:

- •Лекция 31. Беспроводные сети Radio-Ethernet.

- •Заключение

- •Лекция 32. Беспроводные локальные сети на основе Wi-Fi - технологии. Введение.

- •Архитектура, компоненты сети и стандарты

- •Организация сети

- •Физический уровень ieee 802.11

- •Канальный уровень ieee 802.11

- •Типы и разновидности соединений

- •2. Инфраструктурное соединение.

- •4. Клиентская точка.

- •5. Соединение мост.

- •Список использованной литературы:

Лекция 11. Программируемый периферийный интерфейс.

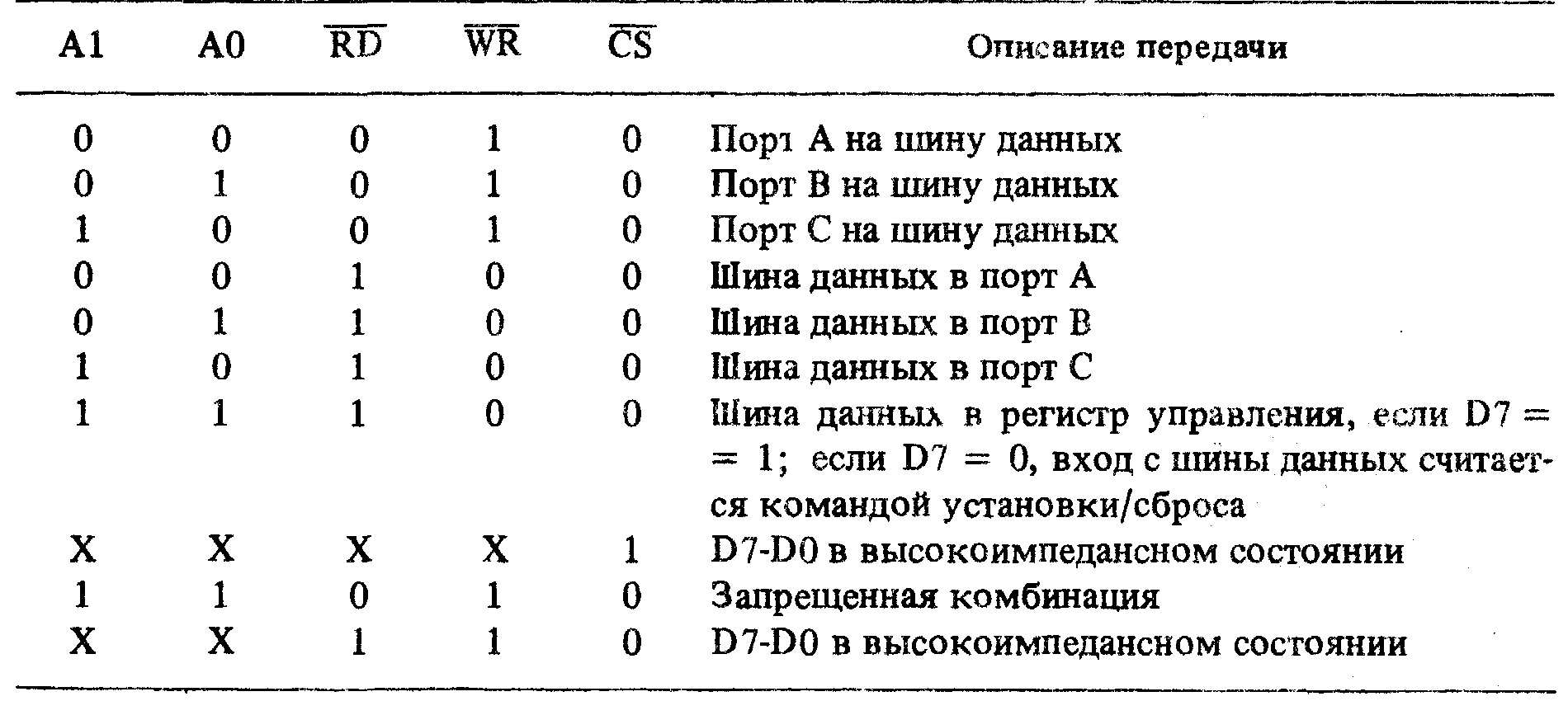

Примером параллельного интерфейса служит микросхема 8255А программируемого периферийного интерфейса. Как показано на рис. 9.21, она имеет регистр управления и три отдельно адресуемых порта A, B и С. Обращение к 8255А определяет сигнал CS, а направление обращения - сигналы RD и WR. Адресуемый регистр определяют сигналы на входах А1 и АО. Следовательно, младший адрес порта, назначаемый 8255А, должен быть кратным 4. Полная адресация 8255А содержится в табл 9.2

Таблица 9.2

Адресация микросхемы 8255А

Так как биты порта С иногда используются как биты управления, 8255А спроектирован так, что в них можно выводить по отдельности, пользуясь командой установки/сброса. Когда 8255А принимает байт, направляемый в его регистр управления, он анализирует бит 7 данных. Если этот бит содержит 1, данные передаются в регистр управления; если же бит 7=0, данные считаются командой установки/сброса и применяются для установки или сброса определяемого командой бита порта С. Биты 3-1 дают номер изменяемого бита, а бит 0 показывает сброс или установку. Остальные биты не используются.

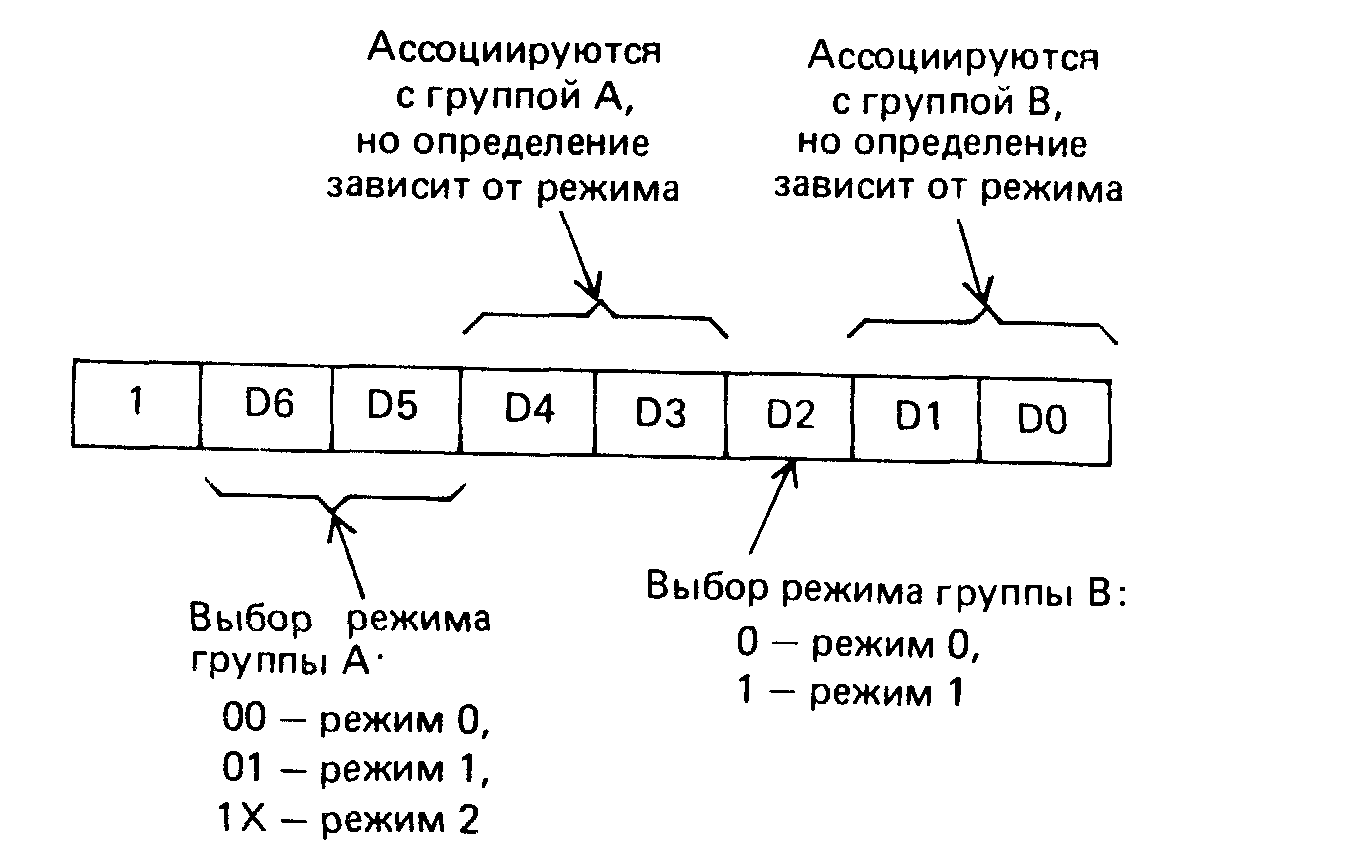

Биты трех портов выведены на контакты, которые подключаются к устройству ввода-вывода. Они разделены на группы А и В, причем группу А образуют биты порта А и 4 старших бита порта С, а группу В - порт В и 4 младших бита порта С. Группа А может работать в трех режимах (0, 1, 2), а группа В - в двух режимах (0 и 1). Режимы определяются содержимым регистра управления, формат которого приведен на рис. 9.22.

Рис. 9.21. Схема интерфейса 8255А

Режим 0. В этом режиме группа разделяется на два набора. В группе А этими наборами являются порт А и старшие 4 бита порта С, а в группе В - порт В и младшие биты порта С. Каждый набор можно использовать для ввода или вывода, но не для двунаправленных передач. Биты D4, D3, D1 и DO в регистре управления определяют, какие наборы предназначены для ввода, а какие - для вывода. Эти биты ассоциируются с наборами следующим образом:

Рис. 9 22. Формат регистра управления микросхемы 8255А

D4 порт A

D3 старшая половина порта С,

D1 - порт В,

DO - младшая половина порта С

Если бит содержит 0, соответствующий набор применяется для вывода, а в противном случае для ввода

Режим 1. Когда в этом режиме работает группа A, порт А используется для ввода или вывода в соответствии с битом D4 (D4 = 1 указывает ввод), а старшая половина порта С применяется для сигналов квитирования и управления.

При вводе старшим битам пота С назначены следующие названия и определения:

РС4 STBA - сигнал 0 на этом контакте заставляет РА7-РАО "стробироваться" в порт А.

РС5 IВFA — показывает, что входной буфер заполнен. Устанавливается в 1, когда порт А содержит данные, которые еще не введены в процессор. Когда действует сигнал 0, устройство может вводить в интерфейс новый байт.

РС6, РС7 - применяются для вывода сигналов управления в устройство или ввода состояния из устройства. Если бит D3 в регистре управления содержит 0, эти линии выходные; в противном случае - входные.

При выводе:

РС4, РС5 - выполняют те же функции, что и РС6, РС7 при вводе.

РС7 ОВFA - показывает, что выходной буфер заполнен. Формирует сигнал 0 в устройство, когда порт А выводит в устройство новые данные.

РС6 АСКA - устройство подает 0 на этот вход, когда оно восприняло данные из порта А.

В режиме 1 с группой А ассоциируется РСЗ, обозначаемый INTRA. Этот сигнал применяется как линия запроса прерывания и подключается к одной из линий IR системной шины. При вводе в порт А на этом выходе формируется сигнал 1, когда новые данные помещаются в порт А (т. е. им управляет РС4), и сигнал 0, когда процессор считывает данные. При выводе на выходе INTRA формируется сигнал 1, когда содержимое порта А воспринято устройством, и сигнал 0, когда процессор загружает новые данные. Если группа В находится в режиме 1, порт В является входным или выходным в зависимости от состояния бита D1 регистра управления (D1 = 1 определяет порт В входным). При вводе РС2 и РС1 обозначаются STBB и IBFB; они выполняют для группы В те же функции, что и сигналы STBA и IВFA для группы А. Аналогично при выводе РС1 и РС2 обозначаются OBFB и АСКB. Выход РС0 превращается в INTRB и используется аналогично INTRA. Разрешением прерываний для группы А управляют РС4 в режиме ввода и РС6 в режиме вывода. Например, в режиме ввода прерывание для группы А разрешается установкой РС4 и запрещается сбросом РС4 с помощью команды установки/сброса. Аналогично разрешением прерываний для группы В управляет установка/сброс РС2.

Режим 2. В данном режиме может работать только группа А, хотя в ней для генерирования запросов прерываний используется РСЗ. В режиме 2 порт А становится двунаправленным, а 4 старших бита порта С определяются следующим образом:

РС4 STBA сигнал 0 на этой линии заставляет данные с РА7-РАО стробироваться в порт А.

РС5 IВFA - формируется сигнал 1, когда в порт А загружаются новые данные 1 с линий РА7-РАО, и сигнал 0, когда процессор считывает данные.

РС6 АСКA - показывает, что устройство готово воспринимать данные с линий РА7-РАО.

PC7 OBFA – формирует сигнал 0, когда процессор загружает в порт A новые данные, а сигнал 0, когда данные принягы устройством.

Когда гpyппа А находится в режиме 2, группа В может работать в peжиме 0 или 1. Если группа В находится в режима 0 только РС2 - РC0 можно использовать для ввода или вывода, так как PC3 служит запросом прерываний для группы A. Обычно если группа A работает в режиме 2, РС2 – РC0 подгключаются к контактам управления и состояния устройства, которое подсоединено к линиям порта A. Для этих же целей может применяться порт B.

Во всех тех режимах порт С отражает сигналы на линиях РС7-РСО и его можно считать командой IN.

9 2.2 Пример использования

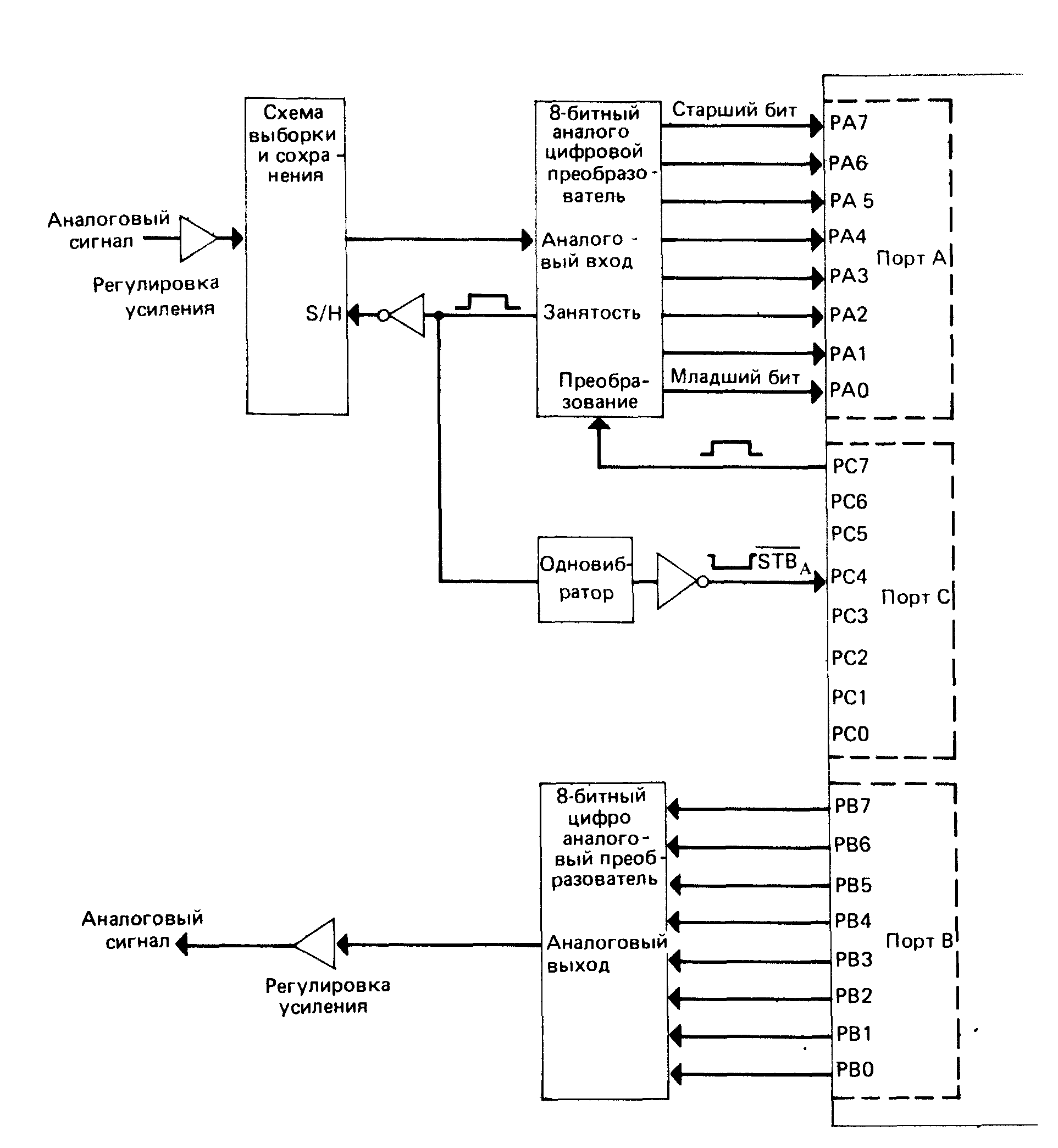

На рис. 9.23 показано возможное подключение микросхемы 8255А к аналого-цифровой и цифро-аналоговой подсистемам. Так во время аналого-цифрового преобразования аналоговое напряжение должно оставаться неизменным, необходима схема выборки и сохранения. Группа А работает на ввод в режиме 1. Преобразование инициируется сигналом на выходе РС7, это стимулирует преобразователь выдать сигнал занятости. Линия занятости подключена на .вход управления выборкой и сохранением (S/H) и на вход одновибратора, запускаемого спадающим фронтом. Пока сигнал занятости имеет высокий уровень, схема выборки и сохранения поддерживает постоянный выход, а когда в конце преобразования сигнал занятости снимается, запускается одновибратор. Его выход инвертируется и подается на вход SТВA (РС4) микросхемы 8255А. Он заставляет цифровой отсчет стробироваться в порт А. В цифро-аналоговой части подсистемы порт В работает как выходной в режиме 0; он подключен непосредственно на двоичный вход цифро-аналогового преобразователя. Квитирование здесь не применяется.

Предположим, что порты А, В и С и регистр управления имеют адреса FFF8, FFF9 FFFA и FFFB. Тогда команды

MOV AL, 10110000В

OUT DX, AL

заставляют порт А работать в режиме 1, порт В - в режиме 0, а РС7 быть выходом. Следующий фрагмент формирует импульс на входе запуска аналого-цифрового преобразователя.

MOV DX, OFFFBH

MOV AL, 00001111B

OUT DX, AL

MOV AL, 00001110B

OUT DX, AL

Здесь первая команда загружает в регистр DX адрес, ассоциируемый с командой установки/сброса, который coвпадает с адресом регистра управления Следующие две команды формируют сигнал PC7 = 1, а последние две - сигнал РС7 = 0. Фрагмент программного ввода преобразованных данных имеет вид

MOV DX.OFFFAH

AGAIN; IN AL,DX

TEST AL.,001OOOOOB

JZ AGAIN

MOV DX. OFFF8H

IN AL, DX

Рис. 9.23. Интерфейс аналого-цифровой и цифро-аналоговой подсистем с применением микросхемы 8255А

Для вывода байта из регистра AL в цифро-аналоговый преобразователь требуются только две команды.

MOV DX, OFFF9H

OUT DX, AL

Как только байт появляется в порту В, его биты сразу подаются на входы цифро-аналогового преобразователя, который в свою очередь сразу же преобразует их в аналоговый сигнал.

В данном примере предполагается, что синхронизация преобразований осуществляется программой и что коэффициенты усиления входного и выходного аналоговых усилителей регулируются. Чтобы получить от программы равномерное распределение входных и выходных отсчетов, необходимо учитывать времена выполнения команд.

MOV CX, N

IDLE NOP

LOOP IDLE

между вводами или выводами. Схема ввода с программной синхронизацией отсчетов аналого-цифрового преобразования представлена на рис. 9.24

Часто в аналого-цифровой и цифро-аналоговой подсистеме применяются программируемые генераторы синхронизации и усилители, что позволяет более точно управлять расположением отсчетов и цифро-аналоговых выходов, а также динамически изменять усиление. Кроме того, в такую подсистему часто вводят контроллер ПДП для увеличения скорости ввода и вывода.

На рис 9.23 показаны только 8-битные преобразователи, имеющие разрешающую способность 1 из 256. Если диапазон входного или выходного напряжений равен -10 . . . +10 В, разрешающая способность составляет

20/256= 0,078В.

Для улучшения разрешающей способности применяются 10-, 12- или 14-битные преобразователи. В этом случае приходится пользоваться комбинацией портов А и С или В и С или параллельно включать две микросхемы 8255А.