- •2.Машинные формы представления чисел с фиксированной запятой. Прямой, обратный и дополнительный коды.

- •3.Модифицированные обратный и дополнительный коды и их прикладное значение.

- •Эквивалентности

- •7.Функции алгебры логики. Функционально-полные системы элементарных логических функций.

- •9.Системы логических элементов. Основные параметры. Условно-графические обозначения элементов, выполняющих элементарные логические функции.

- •19.Типы конфликтов в конвейере. Конфликты по управлению, конфликты по данным, структурные конфликты и методы уменьшения их влияния на снижение производительности микропроцессора.

- •20.Структура 32-разрядного микропроцессора. Особенности работы микропроцессора в реальном и защищенном режимах.

- •23.Мультипрограммный режим работы компьютера. Одноочередные дисциплины распределения ресурсов.

- •25.Запоминающие устройства: назначение, основные параметры, классификация. Иерархическая структура зу современных эвм.

- •26.Запоминающие устройства: назначение, основные параметры, классификация. Назначение и принципы работы кэш-памяти.

- •28.Прерывания. Последовательность действий компьютера при обработке запросов прерываний. Назначение и структура контроллера приоритетных прерываний.

- •29.Классификация прерываний. Обработка прерываний в реальном режиме. Таблица векторов прерываний.

- •49. Локальные вычислительные сети. Основные характеристики сетей Ethernet, Token Ring.

- •Значения

- •31 32.Этапы развития архитектуры микропроцессоров. Технология mmx, sse, sse-2. Основные направления развития архитектуры универсальных микропроцессоров:

- •В настоящее время для повышения производительности микропроцессоров используется ряд новых подходов, основными из которых являются:

- •35Архитектура микропроцессора Itanium. Данный микропроцессор относится к новой, 64-разрядной архитек туре ia-64.Структура микропроцессора Itanium:

26.Запоминающие устройства: назначение, основные параметры, классификация. Назначение и принципы работы кэш-памяти.

Памятью эвм назыв.совокупность устройств,служащих для запоминания,хранения и выдачи инф. Основные параметры ЗУ:емкость,быстродействие.Емкостью пам.назыв.max кол-во данных хранящися в ЗУ.Быстродейств.памя.определ.продолжительностью операции обращения.То есть врем.затрачив.на поиск инф.и на ее считывания;или на поиск места в памяти и на запись.

ЗУ:->по типу обращ.->только чтение.

->запись,чтение.

->по организ.доступа.->c произв.доступа.

->с последов.доступом.

->c прям.или циклическим дост

Кэш память-это спец образом организованая ЗУ,предназначеная для хранения часто используемой инф.и организованая в виде ассоциотивной памяти.

!Обращение к кэш пам.происх.по физическому адресу,формируемому микро процессом.Если необходимой инф.в кэш пам.нет(кэш промох),то происходит обращение к ОЗУ к этому адресу.Инф.считывается к ОЗУ в микропроц.и одноврем.сохр.в кэш пам. !Если нужная инф.находится в кэш пам.то это кэш попадание.

28.Прерывания. Последовательность действий компьютера при обработке запросов прерываний. Назначение и структура контроллера приоритетных прерываний.

Прерывание-это прекращение выполнения текущей команды или текущей последовательности команд для обработки некоторого события специальной программой - обработчиком прерывания, с последующим возвратом к выполнению прерванной программы. Аппаратные прерывания используются для организации взаимодействия с внешними устройствами. Запросы аппаратных прерываний поступают на специальные входы микропроцессора. Они бывают:1)маскируемые, которые могут быть замаскированы программными средствами компьютера ;2)немаскируемые, запрос от которых таким образом замаскирован быть не может. Программные прерывания вызываются следующими ситуациями:1)особый случай, возникший при выполнении команды и препятствующий нормальному продолжению программы (переполнение, нарушение защиты памяти, отсутствие нужной страницы в оперативной памяти и т.п.);2)наличие в программе специальной команды прерывания INT n, используемой обычно программистом при обращениях к специальным функциям операционной системы для ввода-вывода информации.

Последовательность действий компьютера:1)определение наиболее приоритетного незамаскированного запроса на прерывание (если одновременно поступило несколько запросов);2)определение типа выбранного запроса;3)сохранение текущего состояния счетчика команд и регистра флагов;4)определение адреса обработчика прерывания по типу прерывания и передача управления первой команде этого обработчика;5)выполнение программы - обработчика прерывания;6)восстановление сохраненных значений счетчика команд и регистра флагов прерванной программы;7)продолжение выполнения прерванной программы.

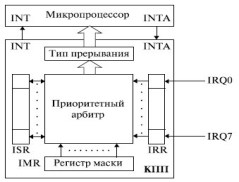

Контроллер приоритетных прерываний:Микропроцессор имеет 2 входа для приема запросов прерываний: вход INT-по нему принимаются запросы,обработка которых может быть замаскирована сбросом флага IF в регистре флагов,-и вход немаскируемых прерываний NMI.Вход NMI фактически закреплен за запросами прерываний от схем контроля питания. Поэтому при такой архитектуре микропроцессора в микропроцессорной системе обязательно должны использоваться средства, которые позволяют предварительно обрабатывать и передавать на вход маскируемых прерываний INT микропроцессора запросы от многочисленных внешних устройств, входящих в состав микропроцессорной системы. В качестве такой схемы используется контроллер приоритетных прерываний(КПП).Структура: