- •11. Ситуации риска в логических схемах

- •11.1. Введение

- •11.2. Явления временной задержки в логических элементах

- •11.3. Условия возникновения выбросов

- •11.4. Возникновение ситуаций статического риска в комбинационных схемах

- •11.5. Устранение статического риска

- •11.6. Построение гарантированных от риска комбинационных схем

- •11.7. Анализ схем для обнаружения ситуаций риска

- •11.8. Ситуации динамического риска

- •11.9. Ситуации существенного риска

- •Упражнения

11. Ситуации риска в логических схемах

11.1. Введение

Во многих случаях неправильная работа реальных логических схем может объясняться наличием с них ситуаций риска, поэтому для разработчика логических схем необходимо иметь ясное представление о причинах появления таких ситуаций и знать об их влиянии на работу схем.

Существует три типа риска в логических схемах:

а) статический риск;

б) динамический риск;

в) существенный риск.

Статический и динамический риск может возникнуть в комбинационных, а также в асинхронных схемах, реализованных на логических элементах. Существенный риск может возникать только в асинхронных схемах.

В этой главе описываются случаи появления ситуаций риска в логических схемах, а также излагаются методы их обнаружения. Кроме этого, приводятся методы проектирования, позволяющие избавляться от ситуаций риска.

11.2. Явления временной задержки в логических элементах

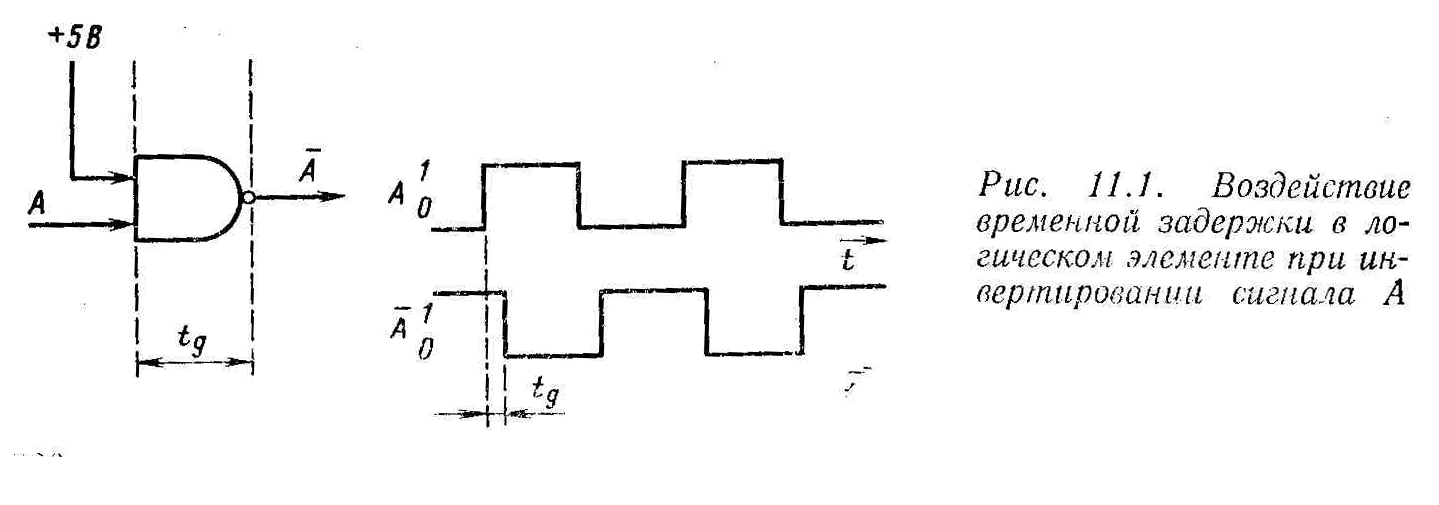

Е сли

в комбинационной схеме в качестве

инвертора используется двухвходовый

логический элемент И-НЕ, как показано

на рис. 11.1, то между требуемым изменением

на выходе и вызывающим его изменением

на входе существует конечная временная

задержка tg.

Это показано на временных диаграммах,

из которых видно, что в результате

изменения А

от 0 до 1 изменение А

от 1 до 0 происходит на tg

секунд позднее. Аналогично этому, при

изменении А

от 1 до 0 соответствующее изменение А

от 0 до 1 осуществится также на tg

позднее.

сли

в комбинационной схеме в качестве

инвертора используется двухвходовый

логический элемент И-НЕ, как показано

на рис. 11.1, то между требуемым изменением

на выходе и вызывающим его изменением

на входе существует конечная временная

задержка tg.

Это показано на временных диаграммах,

из которых видно, что в результате

изменения А

от 0 до 1 изменение А

от 1 до 0 происходит на tg

секунд позднее. Аналогично этому, при

изменении А

от 1 до 0 соответствующее изменение А

от 0 до 1 осуществится также на tg

позднее.

11.3. Условия возникновения выбросов

Если, как показано

па рис. 11.2, на входы элемента И подаются

одновременно сигнал А

и его отрицание

![]() ,

полученное при помощи логического

элемента И-НЕ, изображенного на рис.

11.1, то по правилам алгебры логики сигнал

на его выходе должен быть равен

,

полученное при помощи логического

элемента И-НЕ, изображенного на рис.

11.1, то по правилам алгебры логики сигнал

на его выходе должен быть равен

![]() .

Однако, как можно видеть на временных

диаграммах, в течение интервалов времени,

отмеченных штриховкой, А

и

одновременно равны 1, так что в это время

выходной сигнал

.

Однако, как можно видеть на временных

диаграммах, в течение интервалов времени,

отмеченных штриховкой, А

и

одновременно равны 1, так что в это время

выходной сигнал

![]() .

Выходная функция этого элемента, равная

.

Выходная функция этого элемента, равная

![]() ,

состоит из серии положительных выбросов,

возникающих при изменении А

от 0 до 1 и имеющих длительность в tg

с. Это явление, безусловно, объясняется

временной задержкой логического

инвертора, показанного на рис. 11.1.

,

состоит из серии положительных выбросов,

возникающих при изменении А

от 0 до 1 и имеющих длительность в tg

с. Это явление, безусловно, объясняется

временной задержкой логического

инвертора, показанного на рис. 11.1.

Схему, в которой

возможна генерация сигнала![]() ,

называют схемой со статическим нулевым

риском (0-риском), поскольку выходной

сигнал, который должен быть все время

равен логическому «0», в короткие

временные интервалы устанавливается

в «1».

,

называют схемой со статическим нулевым

риском (0-риском), поскольку выходной

сигнал, который должен быть все время

равен логическому «0», в короткие

временные интервалы устанавливается

в «1».

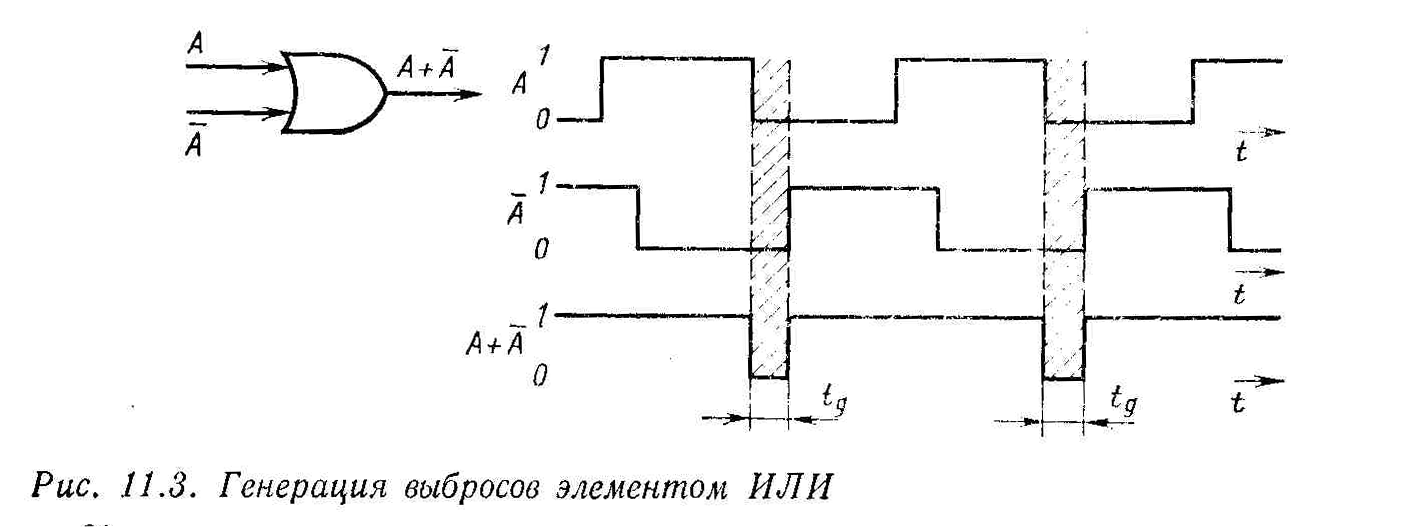

В другом случае,

если сигналы А

и

поступают на входы двухвходового

элемента ИЛИ, как показано на рис. 11.3,

то на выходе элемента появится функция

![]() ,

которая в соответствии с алгеброй логики

должна быть равна логической «1».

Расположение импульсов А

и

на рис. 11.3 показывает, что в течение

временных периодов, соответствующих

заштрихованным частям рисунка, оба они

одновременно равны «0». В течение этих

заштрихованных интервалов, имеющих

небольшую продолжительность, выходной

сигнал равен логическому «0». В таком

случае говорят, что схема имеет статический

единичный риск (1-риск). так как сигнал

на ее выходе, равный в нормальном

состоянии «1», на короткие периоды

времени переходит в логический «0».

Следует отметить, что для элемента ИЛИ

отрицательные выбросы появляются в

моменты, когда А

изменяется от 1 до 0.

,

которая в соответствии с алгеброй логики

должна быть равна логической «1».

Расположение импульсов А

и

на рис. 11.3 показывает, что в течение

временных периодов, соответствующих

заштрихованным частям рисунка, оба они

одновременно равны «0». В течение этих

заштрихованных интервалов, имеющих

небольшую продолжительность, выходной

сигнал равен логическому «0». В таком

случае говорят, что схема имеет статический

единичный риск (1-риск). так как сигнал

на ее выходе, равный в нормальном

состоянии «1», на короткие периоды

времени переходит в логический «0».

Следует отметить, что для элемента ИЛИ

отрицательные выбросы появляются в

моменты, когда А

изменяется от 1 до 0.

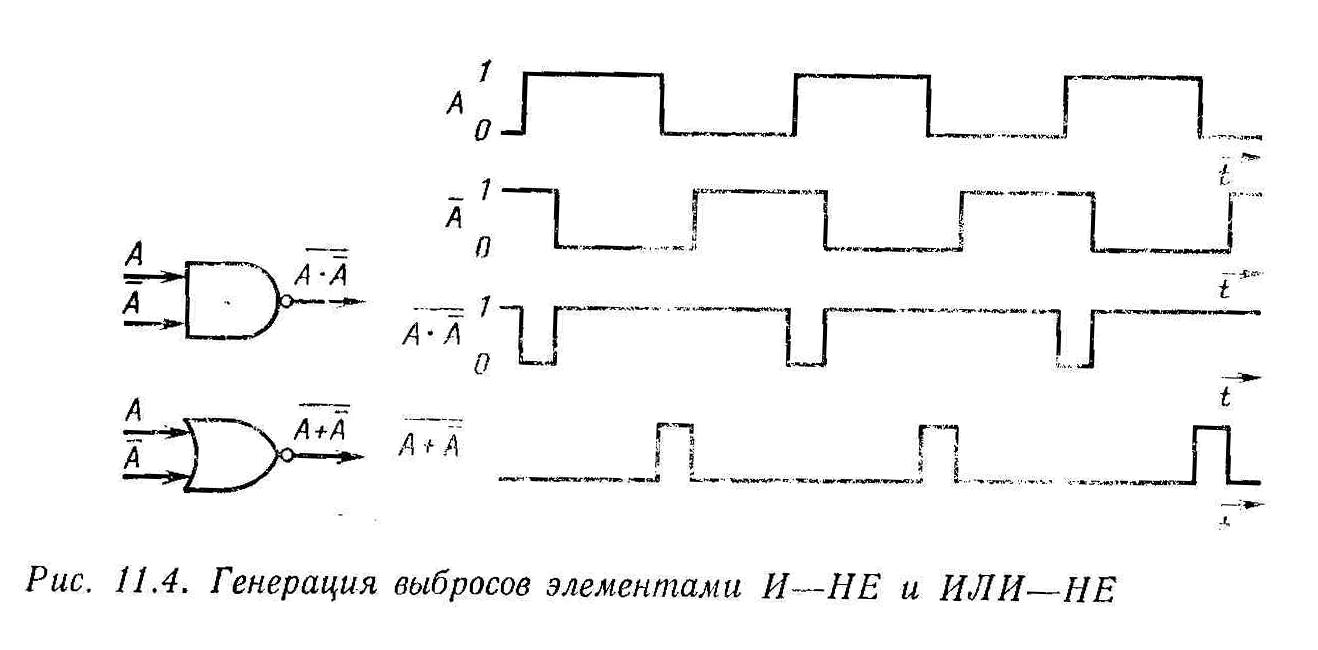

Возникновение

выбросов на выходах элементов И-НЕ

ИЛИ-НЕ показано на рис. 11.4. Отрицательные

выбросы генерируются элементом И-НЕ в

момент перехода А

из 0 в 1. Схема имеет статический 1-риск.

В схеме ИЛИ-НЕ генерируются положительные

выбросы во время переходов А

из 1 в 0. Эта схема имеет статический

0-риск.

Возникновение

выбросов на выходах элементов И-НЕ

ИЛИ-НЕ показано на рис. 11.4. Отрицательные

выбросы генерируются элементом И-НЕ в

момент перехода А

из 0 в 1. Схема имеет статический 1-риск.

В схеме ИЛИ-НЕ генерируются положительные

выбросы во время переходов А

из 1 в 0. Эта схема имеет статический

0-риск.