- •Схемотехника билеты.

- •5. Статические параметры имс.

- •6. Динамические параметры имс.

- •7. Характеристики имс.

- •13. Лэ с повышенной помехоустойчивостью.

- •14. Триггеры. Классификация.

- •16. Синхронные r-s триггеры.

- •21. Параллельные регистры.

- •22. Дешифратор. Уго дешифраторов. Принцип действия.

- •25. Мультиплексоры. Уго мультиплексоров. Принцип действия.

- •26. Демультиплексоры. Уго демультиплексоров. Принцип действия.

- •28. Накапливающий сумматор.

- •Три особенности накапливающего сумматора.

- •29. Последовательный сумматор.

- •30. Схемы сравнения параллельного типа.

- •31. Умножители двоичных чисел.

- •32. Матричная реализация булевых функций.

- •33. Программируемые логические матрицы.

- •34. Плис.

30. Схемы сравнения параллельного типа.

Для сравнения

операндов в цифровых системах используются

специальные схемы сравнения – двоичные

компараторы. Простейшая схема для

определения равенства двух одноразрядных

операндов А и В реализуется логической

операцией «Равнозначность»

.

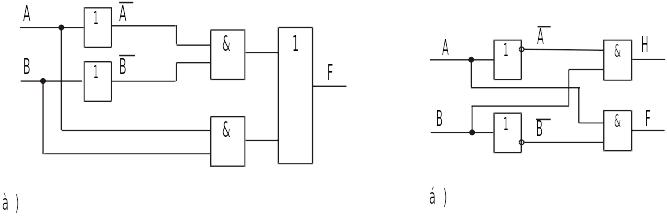

На рис. 76,а представлена функциональная

схема реализующая функцию

.

На рис. 76,а представлена функциональная

схема реализующая функцию

.

.

Рис. 76

Для определения равенства многоразрядных операндов выполняется логическое умножение, т.е. конъюнкция результатов сравнения отдельных разрядов:

Fn = F0F1...Fn-1.

Более сложными и широко используемыми являются схемы сравнения для определения неравенства операндов А и В, в которых реализуются функции:

;

;

.

.

Для одноразрядных

операндов A0 и B0

такие функции сравнения реализуются

на основе операции «Запрет»: F0=A0 ,

,

(рис. 76,б).

(рис. 76,б).

Для двухразрядных операндов А=А1А0 и В=В1В0 функции неравенства определяются следующими выражениями:

Аналогично можно записать функции сравнения для n-разрядных операндов.

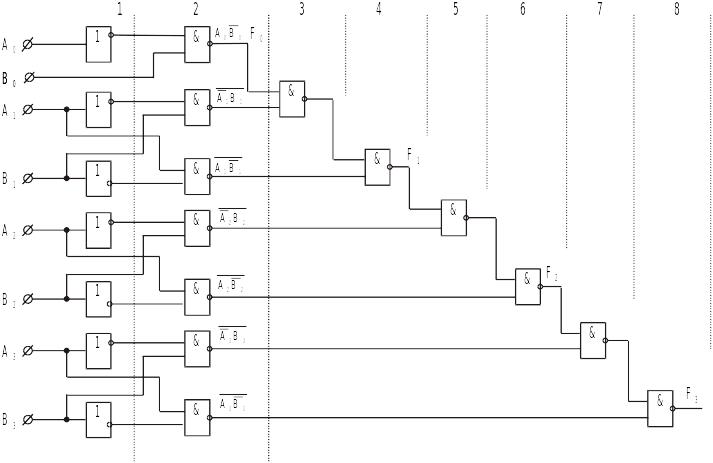

Операция сравнения производится последовательно начиная с младшего разряда. Реализация функции F иллюстрируется схемой сравнения двух 4-х разрядных операндов (рис. 77). Схема представляет собой двоичный компаратор с последовательной структурой. Общая задержка формирования сигнала F равна tF = 2ntз. Для 4-х разрядных операндов tF = 8ntз. Поэтому для разрядности больше, чем 4, такие схемы имеют низкое быстродействие и не используются.

Рис. 77

Для повышения быстродействия цифровых компараторов используют одновременное (параллельное) сравнение всех разрядов операндов в соответствии с вышеуказанными выражениями, в которых осуществляется подстановка функции F и H, выраженных через соотношения операндов.

В этом случае формирование сигнала сравнения F происходит с задержкой tF=4tЗ и не зависит от числа разрядов операндов. Однако в таких схемах требуются логические элементы умножения с числом входов n+1, реализация которых при n>8 затруднена. Вариант схемной реализации параллельного двоичного компаратора представлен на рис. 78.

31. Умножители двоичных чисел.

Операция умножения требует значительных временных затрат, поэтому разработаны различные варианты схем умножения, обеспечивающие максимальное быстродействие. Высокое быстродействие имеют комбинационные схемы умножения. Простейший способ умножения двух n- и m-разрядных чисел описывается следующим алгоритмом:

,

,

где X – n-разрядное множимое,

Y – m-разрядный множитель,

Pj=X yj2j – частные произведения.

В качестве примера приведен процесс умножения двух чисел с разрядностью n = m = 4.

На рис. 83 приведена схема 4-х разрядного умножителя, реализованного по приведенному алгоритму с использованием ИМС полных сумматоров.

Рис. 83

32. Матричная реализация булевых функций.

Для реализации сложных булевых функций широко используются так называемые матричные схемы. Матричная схема представляет собой сетку ортогональных проводников, в пересечении которых могут устанавливаться полупроводниковые элементы (диоды или транзисторы) с односторонней проводимостью либо перемычки.

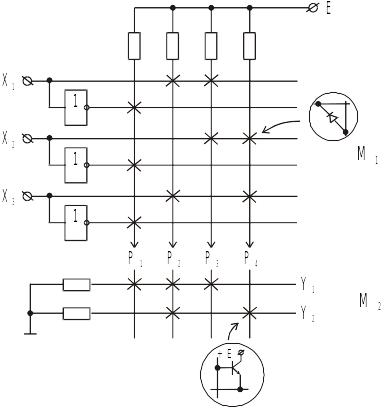

Для примера рассмотрим матричную структуру следующего вида (рис. 88).

Рис. 88

Матрица М1

имеет 6 горизонтальных и 4 вертикальные

шины. Входные шины х1, х2, х3

определенным образом связаны с

вертикальными шинами. Используя

полупроводниковые элементы в узлах

матрицы, можно реализовать на любом из

ее выходов любую конъюнкцию входных

переменных х1, х2, х3.

Для приведенной матрицы М1 можно записать:

.

.

Матрица М2 имеет 2 горизонтальные и 4 вертикальные шины. Указанный способ включения транзистора в местах пересечения шин М2 позволяет реализовать на любом из ее выходов любую дизъюнкцию входных переменных (Р1, Р2, Р3, Р4). Для приведенного примера: y1 = P1+P2+P3; y2 = P2+P4.

При соединении

матриц М1 и М2 по общей шине Р можно

получить систему булевых функций:

Аналогичным образом любая система булевых функций может быть реализована двухуровневой матричной схемой. Основным в построении схем с матричной структурой является определение точек пересечения шин, где должны быть включены коммутирующие элементы. Такая структура называется программируемой логической матрицей. Структурно ПЛМ представляют собой две матрицы, соединенные внутренней шиной (рис. 89).

Рис. 89

По способу программирования различают:

матрицы программируемые (настраиваемые) на заводе-изготовителе – масочно-программируемые МПЛМ;

программируемые пользователем – ППЛМ;

репрограммируемые (многократно) – РПЛМ.